SLVUC46D March 2021 – November 2023

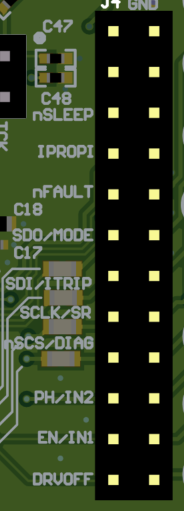

2.2.6 Device Signal and Control Header

The J4 header Figure 2-6 is provided for users who wany to interface an external control design and is also a convenient means for probing all device control signals. When interfacing with an external control design, remove the associated 0-ohm resistors immediately adjacent to the silk screen label.

Note: PH/IN2 signal is not present on

DRV814x-Q1EVM variants. Refer to the EVM schematic for more details.

Figure 2-6 DRV824x-Q1EVM Signal and

Control Header

Figure 2-6 DRV824x-Q1EVM Signal and

Control Header