SNLA343A April 2020 – July 2021 DP83825I

- Trademarks

- 1Introduction

- 2Device Overview

-

3Merging DP83825 Onto Sitara Steps

- 3.1 Step 1 – DP83825 vs. DP83822

- 3.2 Step 2 – Check 8710A Pins with AM335

- 3.3 Step 3 – De-populate the LAN8710A from AM335 EVM - BBB

- 3.4 Step 4 – Check the AM335 (BBB) RMII Connection Pins

- 3.5 Step 5 – Check the DP83825 Connection Pins

- 3.6 Step 6 – PinMux Tool To Generate DTS/DTSI Files.

- 3.7 Step 7 – DP83822 Code Base Review

- 3.8 Step 8 – DP83825 Code Base Review / Patch Adaption

- 3.9 Step 9 – Patch the Linux uboot/kernel

- 3.10 Step 10 – Change the Menu Config

- 3.11 Step 11 – Building the Components (menuconfig/dtb/zimage)

- 3.12 Step 12 – (Optional) Important Fix for DTS Build

- 3.13 Step 13 – Copy the Built Files onto the SD Card

- 3.14 Step 14 – Register Checking for the DP83825.

- 3.15 Step 15 – Linux Command To Assist The Debug

- 3.16 Step 16 – Linux ethtool Command Dumps (example)

- 3.17 Step 17 – Linux dmesg to Check the Ethernet Driver Status.

- 3.18 Step 18 – Testing Result with Detail Log Analysis (Success Case).

- 3.19 Step 19 – YouTube Demonstration Video

- 4Required Hardware and Software

- 5References

- 6Revision History

2 Device Overview

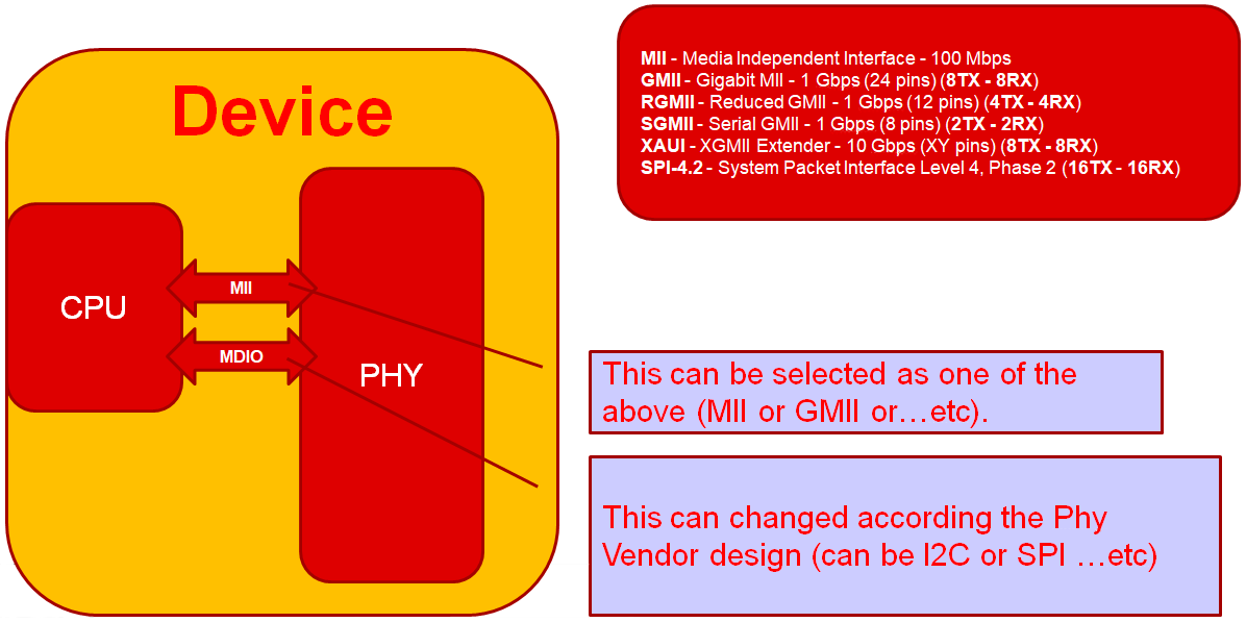

Figure 2-1, is a Sitara MDIO / MII arch example. In the Figure 2-1, the MDIO is a control interface to control the Phy (example: DP83825), and the MII is an interface for the Data Channel between CPU and Phy.

Figure 2-1 Sitara MDIO / MII Arch

Example

Figure 2-1 Sitara MDIO / MII Arch

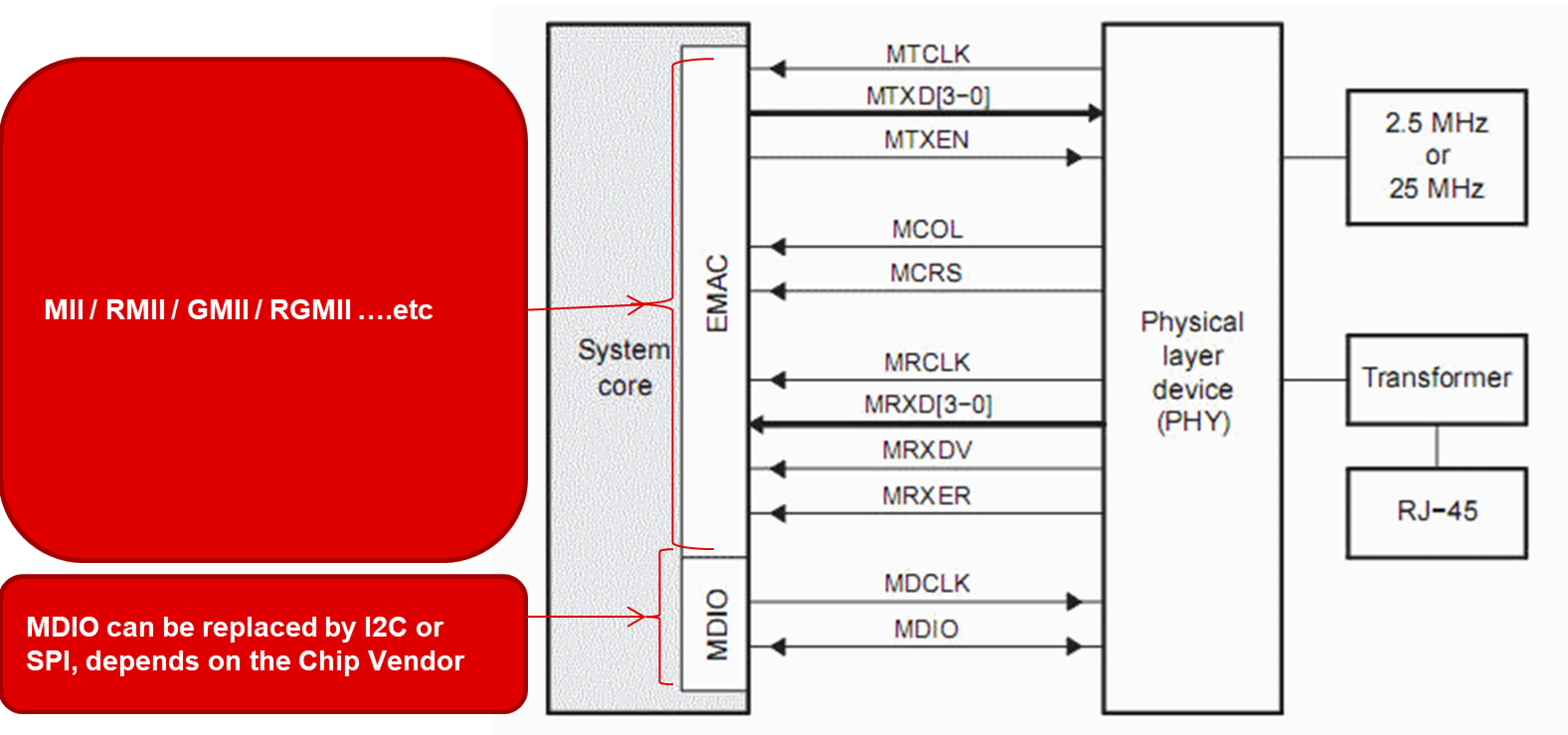

ExampleFigure 2-2, show an example that the MII can be replaced by the other Ethernet Phy spec, for example (RMII, RGMII, SGMII and so on). MDIO control interface can be replaced by I2C/SPI.

While using TI Sitara platform to adapt the TI Phy, we are continuing with MDIO. The EMAC in the Figure 2-2 is an Ethernet MAC layer.

Figure 2-2 Sitara MDIO / MII Detail

Arch

Figure 2-2 Sitara MDIO / MII Detail

Arch