SPRADG4A January 2024 – April 2024

- 1

- Abstract

- Trademarks

- 1General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 2Introduction

- 3System Description

- 4System Overview

- 5Hardware

-

6Software

- 6.1 Getting Started With Firmware

- 6.2 SysConfig Setup

- 6.3 Incremental Builds

- 7Testing and Results

- 8References

- 9Revision History

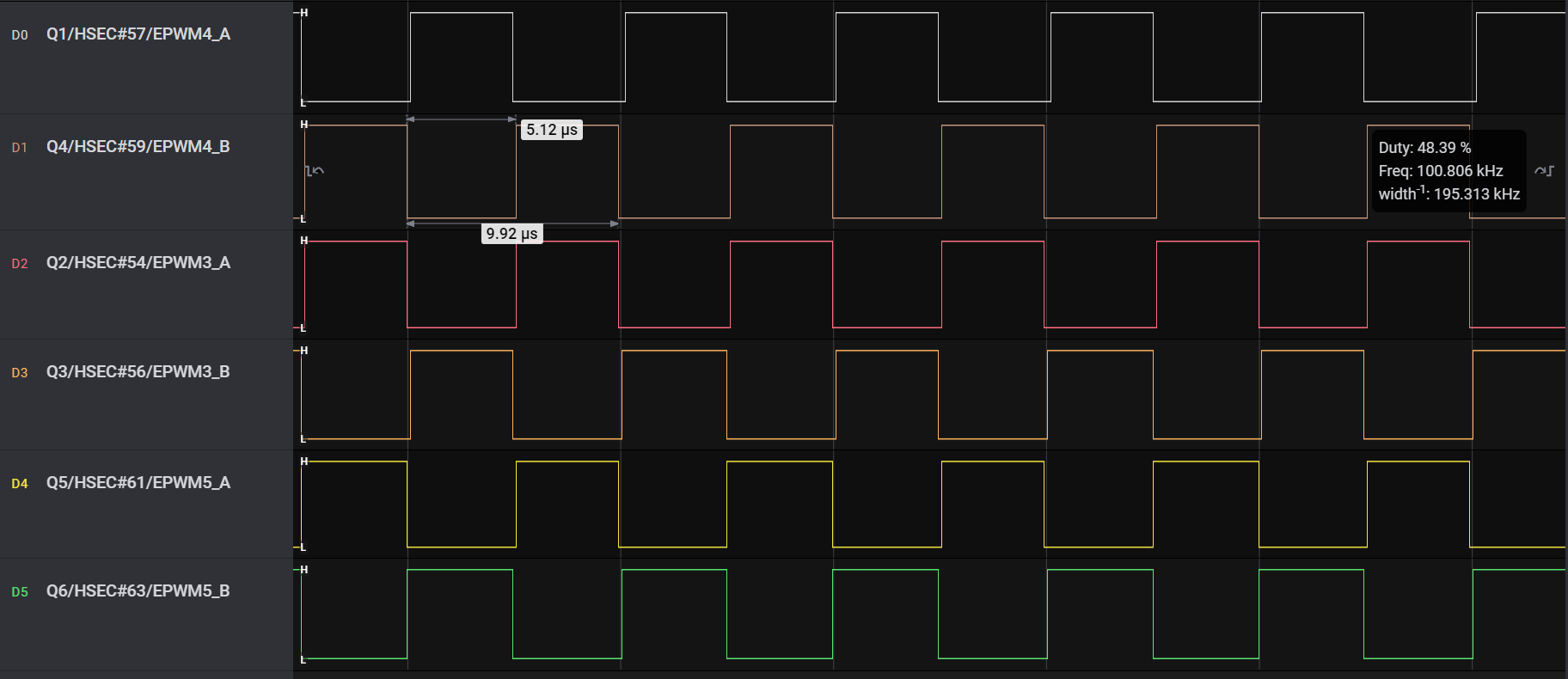

7.1 Lab 0: Basic PWM Check

Lab 0 can be run on the AM263x controlCARD and docking station. To execute Lab 0, build the code by following the steps mentioned in Section 6.3.1.1.3.2.

Connect the ADC4_AIN0, ADC1_AIN1, ADC3_AIN1, ADC3_AIN2 pins of the controlCARD docking station to ground point. Connect the EPWM3, EPWM4, EPWM5 pins of the controlCARD docking station to a logic analyzer to view the PWM waveforms.

- ADC4_AIN0 – Pins 25

- ADC1_AIN1 – Pins 18

- ADC3_AIN1 – Pins 30

- ADC3_AIN2 – Pins 32

- EPWM3 – Pins 54, 56

- EPWM4 – Pins 57, 59

- EPWM5 – Pins 61, 63

Figure 7-1 shows the expected PWM waveforms.

Figure 7-1 PWM Waveforms

Figure 7-1 PWM Waveforms