SPRUIR8B april 2020 – july 2023

- 1

- CLB Tool

- Trademarks

- 1Introduction

- 2Getting Started

- 3Using the CLB Tool

-

4Examples

- 4.1

Foundational Examples

- 4.1.1 CLB Empty Project

- 4.1.2 Example 3 – PWM Generation

- 4.1.3 Example 7 – State Machine

- 4.1.4 Example 13 – PUSH-PULL Interface

- 4.1.5 Example 14 – Multi-Tile

- 4.1.6 Example 15 – Tile to Tile Delay

- 4.1.7 Example 16 - Glue Logic

- 4.1.8 Exampe 18 - AOC

- 4.1.9 Example 19 - AOC Release Control

- 4.1.10 Example 20 - CLB XBARs

- 4.2

Getting Started Examples

- 4.2.1 Example 1 – Combinatorial Logic

- 4.2.2 Example 2 – GPIO Input Filter

- 4.2.3 Example 4 – PWM Protection

- 4.2.4 Example 5 – Event Window

- 4.2.5 Example 6 – Signal Generation and Check

- 4.2.6 Example 8 – External AND Gate

- 4.2.7 Example 9 – Timer

- 4.2.8 Example 10 – Timer With Two States

- 4.2.9 Example 11 – Interrupt Tag

- 4.2.10 Example 12 – Output Intersect

- 4.2.11 Example 17 – One-Shot PWM Generation

- 4.2.12 Example 21 - Clock Prescaler and NMI

- 4.2.13 Example 22 - Serializer

- 4.2.14 Example 23 - LFSR

- 4.2.15 Example 24 - Lock Output Mask

- 4.2.16 Example 25 - Input Pipeline Mode

- 4.2.17 Example 26 - Clocking Pipeline Mode

- 4.3 Expert Examples

- 4.1

Foundational Examples

- 5Enabling CLB Tool in Existing DriverLib Projects

- 6Frequently Asked Questions (FAQs)

- 7Revision History

3.5.1 The Statics Panel

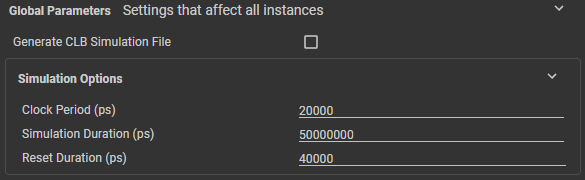

The top panel in the configuration tool contains “Global Parameters” settings used in simulation. Click the '?' icon to see a short description.

Figure 3-15 Static Options

Figure 3-15 Static OptionsThe "Generate CLB Simulation File" is used to generate the content of the "clb_simulation" file. This file, when executed, will generate the .vcd for all of the CLB Tile Designs. This .vcd file will appear in the directory above where the batch file is executed, within a newly created "simulation" directory.

The “Clock Period (ps)” is the period of the CLB clock in picoseconds used for simulation purposes. The “Simulation Duration (ps)” field allows users to control the duration of the simulation run in picoseconds. The “Reset Duration (ps)” field allows the user to insert a delay in picoseconds to mimic the effect of a device reset.