SSZTA83 april 2017 TCA9517 , TCA9802

If you’ve ever programmed anything in your life, you know the feeling of relief that comes with writing your code and having it work with no errors on your first try. Back in the days of Computer Science 101, this was much more feasible. Unfortunately, it rarely happens in the real world, although trial and error can sometimes be how we learn.

Take designing an Inter-Integrated Circuit (I2C) bus, for example. Many designers use I2C for its simplicity – however, the specification is still 64 pages of rules on how to communicate with the protocol. When your first printed circuit board (PCB) comes back and your I2C bus isn’t communicating properly, you’re in for a long night and a huge headache. So in this post, I’ll identify two very common I2C bus problems and introduce solutions to address them.

Headache No. 1: Static Voltage Offset Mismatch

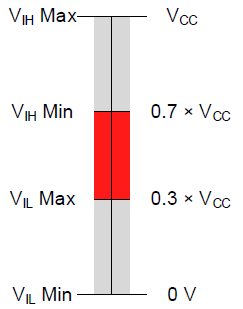

Figure 1 I2C Voltage-level Thresholds

Figure 1 I2C Voltage-level ThresholdsIdeally, your VOL spec should be as close to 0V as possible, in order to eliminate any potential to hit the undefined range after considering other parasitics such as series resistance or high current loads. Previously, most I2C devices (such as the TCA9517) had a static voltage offset, which results in a VOL of ~0.5V. However, TI has developed a new architecture that eliminates the requirement for a static voltage offset, resulting in a VOL of ~0.2V for the TCA9802, one variant of this new family of TCA980x products.

Headache No. 2: Rise-time Violations

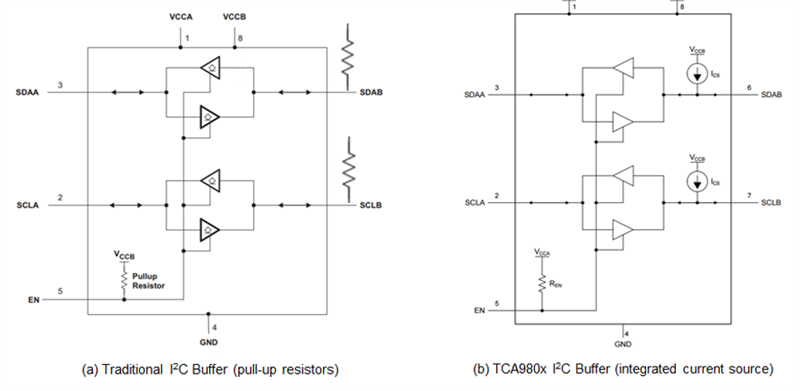

Figure 2 Architecture of a Traditional I2C Buffer (a) vs. the TCA980x Buffer (b)

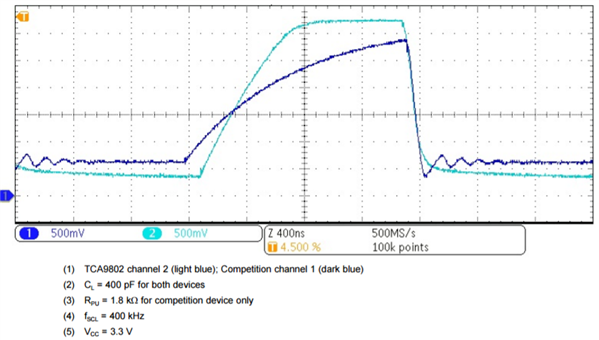

Figure 2 Architecture of a Traditional I2C Buffer (a) vs. the TCA980x Buffer (b)This constant current drive enables a quicker rise time and a more controlled falling edge, resulting in much stronger signal integrity, as shown in Figure 3. The light blue signal in Figure 3 shows the new current source-based architecture compared with a competitor solution shown in dark blue. This new architecture helps prevent ringing on the falling edge, which will also prevent noise reflections on the bus.

Figure 3 TCA980x Rise-time Benefit vs. the Competition

Figure 3 TCA980x Rise-time Benefit vs. the CompetitionTI’s new architecture takes these common design headaches into consideration and provides simple solutions to prevent them. I2C is a standard that intends to simplify designs, which is exactly what the new TCA980x family helps do.

For more details about solving problems with this device family, read the application report, “Advantages and Design Considerations of the TCA980x Family” or see the full portfolio.

Additional Resources

- Learn more about TI’s portfolio of I2C buffered translators, I/O expanders and switches.

- Find the right device for your application with the application report, “Choosing the Correct I2C Device for New Designs.”

- Watch this video which provides additional details about the the TCA980x family benefits.