TIDT280 May 2022

3.4.2 56-V Input Voltage

|

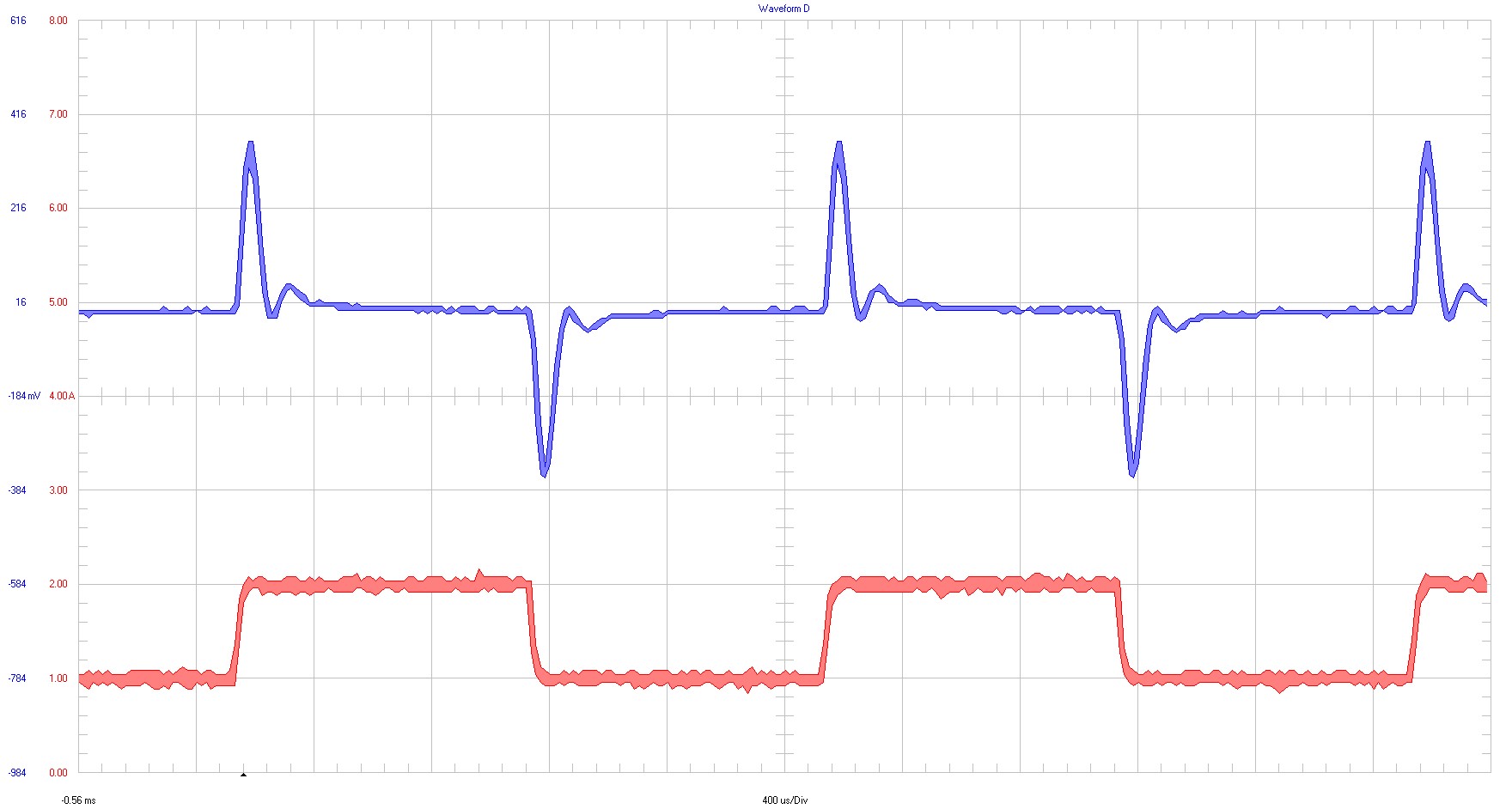

Ch1 ⇒ VOUT (AC) 200 mV / div 10-kHz bandwidth Ch2 ⇒ IOUT 1 A / div 20-MHz bandwidth 400 µs / div |

Figure 3-12 Load Transient 1 A to 2 A at

56-V Input Voltage