LMK04826BEVM の特徴

- JEDEC JESD204B をサポート

- 超低 RMS ジッタ性能

- デュアル・ループ・アーキテクチャ

- LOS (信号損失) 機能搭載、3 個の冗長型入力クロック

- 固定型または動的に調整可能な高精度デジタル遅延機能

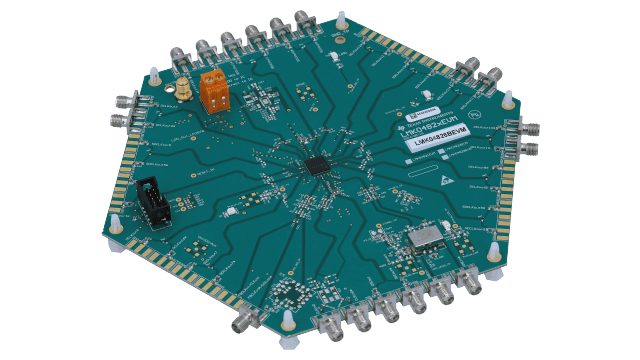

- この評価キットには、評価ボードに USB 接続するための USB2ANY モジュールが付属しています。

LMK04826BEVM に関する概要

LMK04826BEVM と LMK04828BEVM は、JEDEC JESD204B をサポートする、業界最高性能のクロック・コンディショナである LMK04820 製品ファミリに対応します。デュアル・ループ PLLatinum™ アーキテクチャを採用した結果、低ノイズ VCXO モジュールを使用して 100fs (フェムト秒) 以下のジッタ (12kHz~20MHz) を実現できます。このデュアル・ループ・アーキテクチャは、2 個の高性能フェーズ・ロック・ループ (PLL)、1 個の低ノイズ水晶発振器回路、1 個の高性能電圧制御発振器 (VCO) で構成されています。

最初の PLL (PLL1) は低ノイズのジッタ・クリーナ機能を実現し、2番目の PLL (PLL2) はクロックと SYSREF の生成を行います。PLL1は、外付けのVCXOモジュール、または内蔵の水晶発振器と外付けの調整可能水晶振動子およびバラクタ・ダイオードとともに動作するよう構成できます。非常に狭いループ帯域幅と組み合わせる場合、PLL1 は VCXO モジュールまたは調整可能な水晶振動子が出力する優れた近接位相ノイズ特性 (オフセットは 50kHz 以下) を活用し、入力クロックのクリーニングを実施します。PLL1の出力は、PLL2へのクリーンな基準入力として使用され、内蔵のVCOをロックします。

PLL2のループ帯域幅は、ファーアウト位相ノイズ(50kHzよりも高いオフセット)をクリーニングするよう最適化でき、この場合は内蔵のVCOが、PLL1で使用されているVCXOモジュールや調整可能水晶振動子よりも高性能になります。