封裝資訊

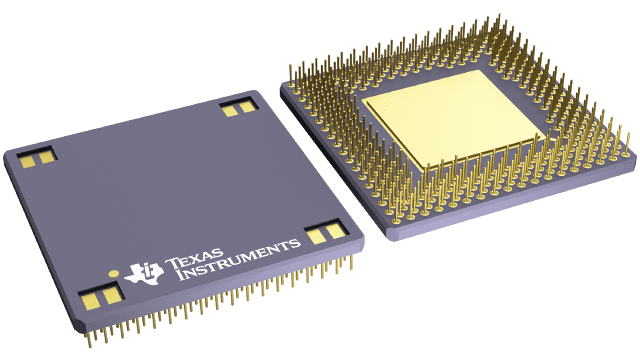

| 封裝 | 引腳 CPGA (GF) | 325 |

| 作業溫度範圍 (°C) -55 to 125 |

| 包裝數量 | 運送包裝 10 | JEDEC TRAY (5+1) |

SMJ320C40 的特色

- SMJ: QML Processing to MIL-PRF-38535

- SM: Standard Processing

- TMP: Commercial Level Processing TAB

- Operating Temperature Ranges:

- Military (M) -55°C to 125°C

- Special (S) -55°C to 100°C

- Commercial (C) -25°C to 85°C

- Commercial (L) 0°C to 70°C

- Highest Performance Floating-Point Digital Signal Processor (DSP)

- C40-60:

- C40-50:

- C40-40:

- 33-ns Instruction Cycle Time:

- 60 MFLOPS, 30 MIPS, 330 MOPS, 384 MBps

- 40-ns Instruction Cycle Time:

- 50 MFLOPS, 25 MIPS, 275 MOPS, 320 MBps

- 50-ns Instruction Cycle Time:

- 40 MFLOPS, 20 MIPS, 220 MOPS, 256 MBps

- Six Communications Ports

- 6-Channel Direct Memory Access (DMA) Coprocessor

- Single-Cycle Conversion to and From IEEE-745 Floating-Point Format

- Single Cycle 1/x, 1/

x

x - Source-Code Compatible With SMJ320C30

- Validated Ada Compiler

- Single-Cycle 40-Bit Floating-Point, 32-Bit Integer Multipliers

- 12 40-Bit Registers, 8 Auxiliary Registers, 14 Control Registers, and 2 Timers

- IEEE Standard 1149.1

Test-Access Port (JTAG)

Test-Access Port (JTAG) - Two Identical External Data and Address Buses Supporting Shared Memory Systems and High Data-Rate, Single-Cycle Transfers:

- High Port-Data Rate of 100 MBytes/s (Each Bus)

- 16G-Byte Continuous Program/Data/Peripheral Address Space

- Memory-Access Request for Fast, Intelligent Bus Arbitration

- Separate Address-, Data-, and Control-Enable Pins

- Four Sets of Memory-Control Signals Support Different Speed Memories in Hardware

- Packaging:

- 325-Pin Ceramic Grid Array (GF Suffix)

- 352-Lead Ceramic Quad Flatpack (HFH Suffix)

- 324-Pad JEDEC-Standard TAB Frame

- Fabricated Using Enhanced Performance Implanted CMOS (EPIC™) Technology by Texas Instruments (TI™)

- Separate Internal Program, Data, and DMA Coprocessor Buses for Support of Massive Concurrent Input/Output (I/O) of Program and Data Throughput, Maximizing Sustained Central Processing Unit (CPU) Performance

- On-Chip Program Cache and Dual-Access/Single-Cycle RAM for Increased Memory-Access Performance

- 512-Byte Instruction Cache

- 8K Bytes of Single-Cycle Dual-Access Program or Data RAM

- ROM-Based Bootloader Supports Program Bootup Using 8-, 16-, or 32-Bit Memories Over Any One of the Communications Ports

IEEE Standard 1149.1- 1990, IEEE Standard Test-Access Port and Boundary-Scan Architecture.

IEEE Standard 1149.1- 1990, IEEE Standard Test-Access Port and Boundary-Scan Architecture.

EPIC and TI are trademarks of Texas Instruments Incorporated.

SMJ320C40 的說明

The C40 digital signal processors (DSPs) are 32-bit, floating-point processors manufactured in 0.72-um, double-level metal CMOS technology. The 320C40 is a part of the fourth-generation DSPs from Texas Instruments and is designed primarily for parallel processing.

For additional information when designing for cold temperature operation, please see Texas Instruments application report 320C3x, 320C4x and 320MCM42x Power-up Sensitivity at Cold Temperature, literature number SGUA001.