SLOS921B December 2015 – September 2018 TAS5411-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Register Maps

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PWP|16

Thermal pad, mechanical data (Package|Pins)

- PWP|16

Orderable Information

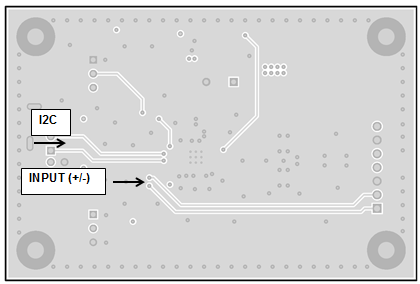

12.2.2 Second Layer – Signal Layer

If possible, route the I2C and the positive and negative input traces close together and cover with ground plane, keeping the signals from noise.

Figure 19. Signal Layer

Figure 19. Signal Layer