SLOS921B December 2015 – September 2018 TAS5411-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Register Maps

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PWP|16

Thermal pad, mechanical data (Package|Pins)

- PWP|16

Orderable Information

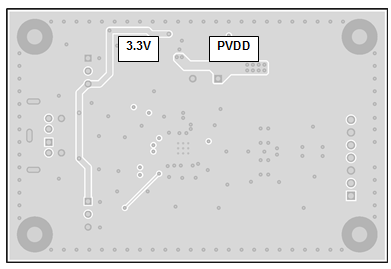

12.2.3 Third Layer – Power Layer

There is no need for a power plane, but TI recommends a wide single PVDD trace to keep the switching noise to a minimum and provide enough current to the device. The wide trace provides a low-impedance path from the power source to the PVDD pin and from the GND pin to the source return. Suppression of switching noise (ripple voltage) on both the positive and return (ground) paths requires a low impedance.

Figure 20. Power Layer

Figure 20. Power Layer