JAJSFA3B September 2012 – April 2018 CSD86360Q5D

PRODUCTION DATA.

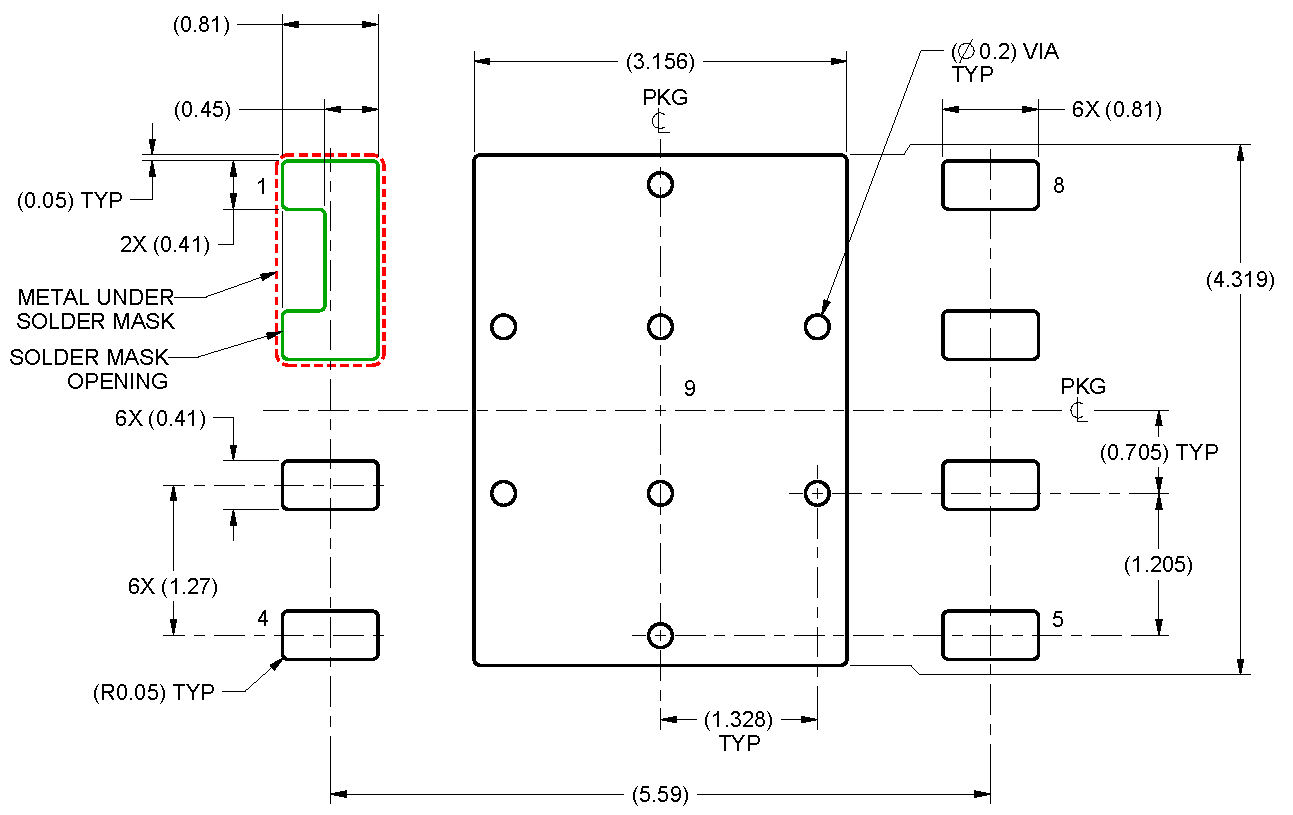

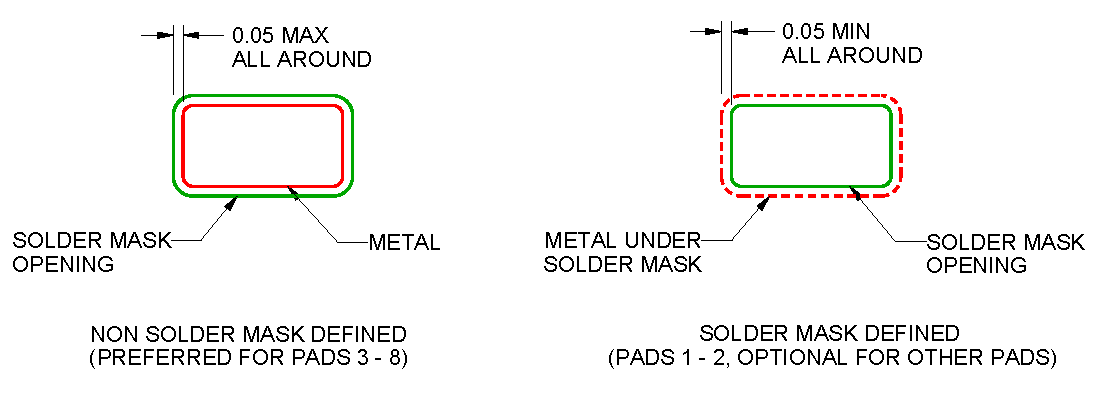

9.2 推奨ランド・パターン

- このパッケージは、基板上のサーマル・パッドにハンダ付けされるよう設計されています。詳細については、『QFN/SON PCBアタッチメント』(SLUA271)を参照してください。

- ビアはアプリケーションに応じてのオプションです。デバイスのデータシートを参照してください。一部またはすべてを実装する場合に推奨されるビアの場所が示されています。