SLAU640B April 2019 – March 2023 ADC12DJ5200SE

- Introduction

- 1Trademarks

- 2Equipment

-

3Setup Procedure

- 3.1 Install the High Speed Data Converter (HSDC) Pro Software

- 3.2 Install the Configuration GUI Software

- 3.3 Connect the EVM and TSW14J57EVM

- 3.4 Connect the Power Supplies to the Boards (Power Off)

- 3.5 Connect the Signal Generators to the EVM (RF Outputs Disabled Until Directed)

- 3.6 Turn On the TSW14J57EVM Power and Connect to the PC

- 3.7 Turn On the ADC12DJ5200RFEVM/SEEVM Power Supplies and Connect to the PC

- 3.8 Turn On the Signal Generator RF Outputs

- 3.9 Open the ADC12DJ5200RFEVM/SEEVM GUI and Program the ADC and Clocks

- 3.10 Calibrate the ADC Device on the EVM

- 3.11 Open the HSDC Software and Load the FPGA Image to the TSW14J57EVM

- 3.12 Capture Data Using the HSDC Pro Software

- 4Device Configuration

- 5Troubleshooting the ADC12DJ5200RFEVM/SEEVM

- 6References

- 7HSDC Pro Settings for Optional ADC Device Configuration

- 8Signal Routing

- A Analog Inputs

- B Jumpers and LEDs

- B Revision History

3.9 Open the ADC12DJ5200RFEVM/SEEVM GUI and Program the ADC and Clocks

The Device Configuration GUI is installed separately from the HSDC Pro installation and is a stand-alone GUI.

The max clock rate supported by ADC12DJ4000RF is 4000 MHz and only 8-bit mode are suppored by ADC08DJ5200RF. All the 12-bit and 15-bit modes are disabled on ADC08DJ5200RF.

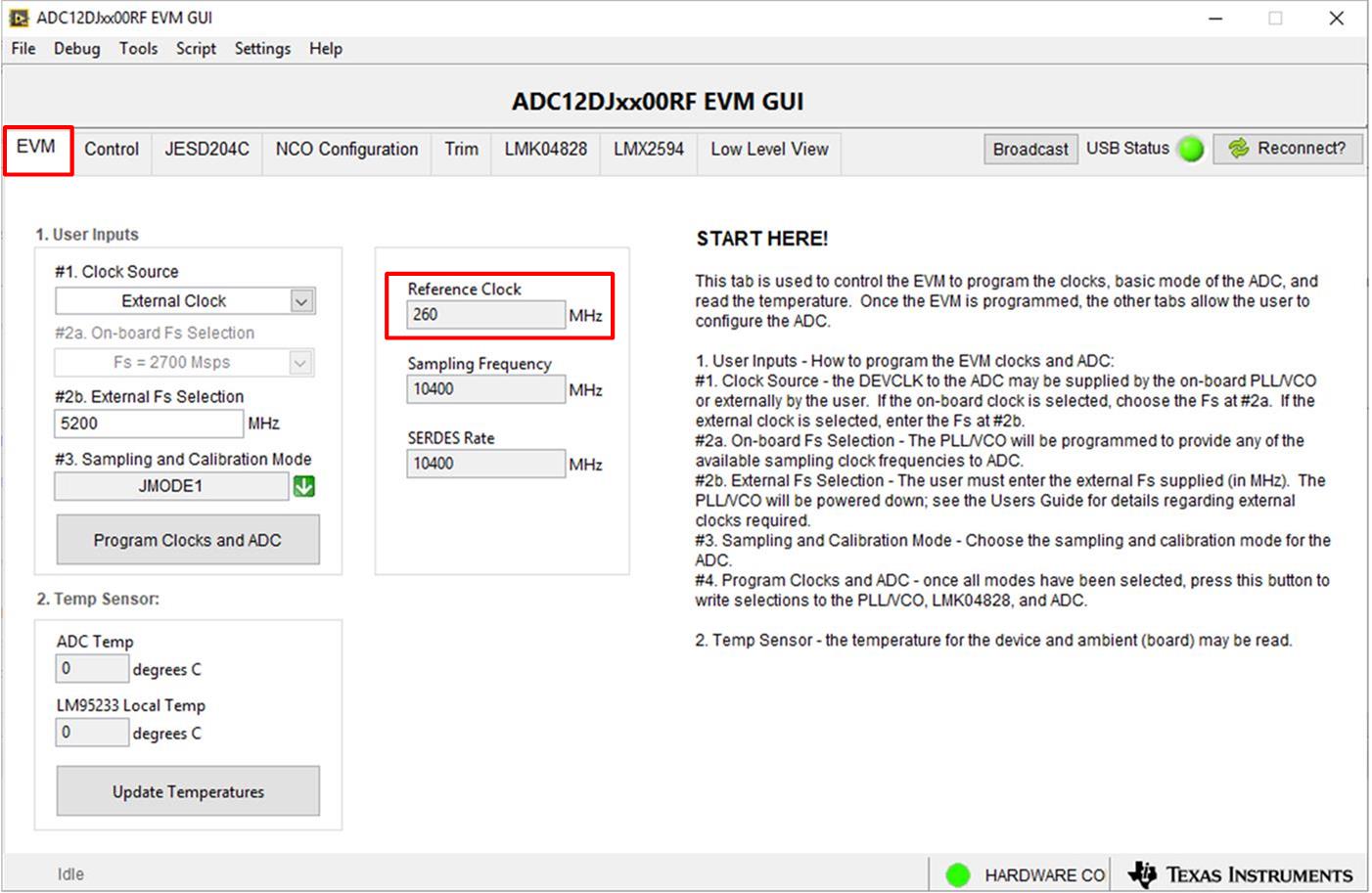

Figure 3-2 Configuration GUI EVM Tab

Figure 3-2 Configuration GUI EVM Tab#SLAU7017106 and GUID-28C10626-4F3D-49F6-B012-877D6C1523B2.html#SLAU7013197 show the GUI open to the EVM tab and Control tab respectively. Tabs at the top of the panel organize the configuration into device and EVM features with user-friendly controls and a low-level tab for directly configuring the registers. The EVM has three configurable devices, namely the ADC12DJ5200RF/SE, LMK04828, LMK61E2, and LMX2594. The register map for each device is provided in the device data sheet (ADC12DJ5200RF/SE 10.4-GSPS Single Channel or 5.2-GSPS Dual Channel, 12-bit, RF, LMK0482xB Ultra Low-Noise JESD204B Cmplnt Clck Jitter Cleaner w/ Dual Loop PLLs, and LMX2594 15-GHz Wideband PLLatinum™ RF Synthesizer, respectively).

- Open the ADC12DJ5200RFEVM GUI.

- Select the external clock as the clock source.

- Enter Fs = 5200 MHz MSPS as the external Fs selection.

- Select JMODE1 for the sampling and Calibration mode.

- Click Program Clocks and ADC (Note: This action will overwrite any previous device register settings.)

- The Reference frequency required by the EVM is shown under indicator Reference Clock.