SPRUJ10D May 2022 – September 2023

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Kit Overview

- 3Board Setup

-

4Hardware Description

- 5.1 Functional Block Diagram

- 5.2 GPIO Mapping

- 5.3 Reset

- 5.4 Clock

- 5.5 Memory Interface

- 5.6 Ethernet Interface

- 5.7 I2C

- 5.8 Industrial Application LEDs

- 5.9 SPI

- 5.10 UART

- 5.11 MCAN

- 5.12 FSI

- 5.13 JTAG

- 5.14 Test Automation Header

- 5.15 LIN

- 5.16 MMC

- 5.17 ADC and DAC

- 5.18 EQEP and SDFM

- 5.19 EPWM

- 5.20 BoosterPack Headers

- 5.21 Pinmux Mapping

- 5References

- 6Revision History

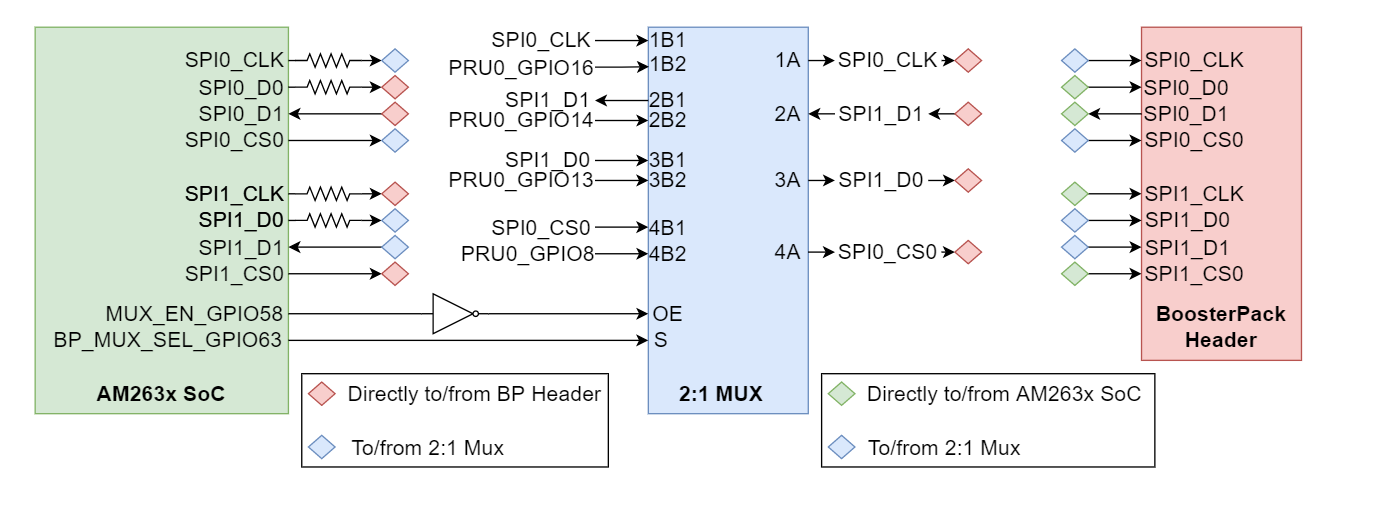

4.9 SPI

The AM263x LauncPad maps two SPI instances (SPI0,SPI1) from the AM263x SoC to the BoosterPack Headers. Series termination resistors are placed near the SoC for each SPI clock and SPI D0 signal. There is a 2:1 Mux (SN74CB3Q3257PWR) that is responsible for selecting SPI signals for proper function. The Mux is driven by two GPIO signals that are generated from the AM263x SoC.

Table 4-9 SPI MUX

| Output Enable (OE) | Select (S) | Input/Output | Function |

|---|---|---|---|

| Low | Low | A ↔ B1 | A port = B1 port |

| Low | High | A ↔ B2 | A port = B2 port |

| High | X | Hi-Z | Disconnect |

Figure 4-12 SoC SPI Interface to

BoosterPack

Figure 4-12 SoC SPI Interface to

BoosterPack