SPRUJ10D May 2022 – September 2023

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Kit Overview

- 3Board Setup

-

4Hardware Description

- 5.1 Functional Block Diagram

- 5.2 GPIO Mapping

- 5.3 Reset

- 5.4 Clock

- 5.5 Memory Interface

- 5.6 Ethernet Interface

- 5.7 I2C

- 5.8 Industrial Application LEDs

- 5.9 SPI

- 5.10 UART

- 5.11 MCAN

- 5.12 FSI

- 5.13 JTAG

- 5.14 Test Automation Header

- 5.15 LIN

- 5.16 MMC

- 5.17 ADC and DAC

- 5.18 EQEP and SDFM

- 5.19 EPWM

- 5.20 BoosterPack Headers

- 5.21 Pinmux Mapping

- 5References

- 6Revision History

4.15 LIN

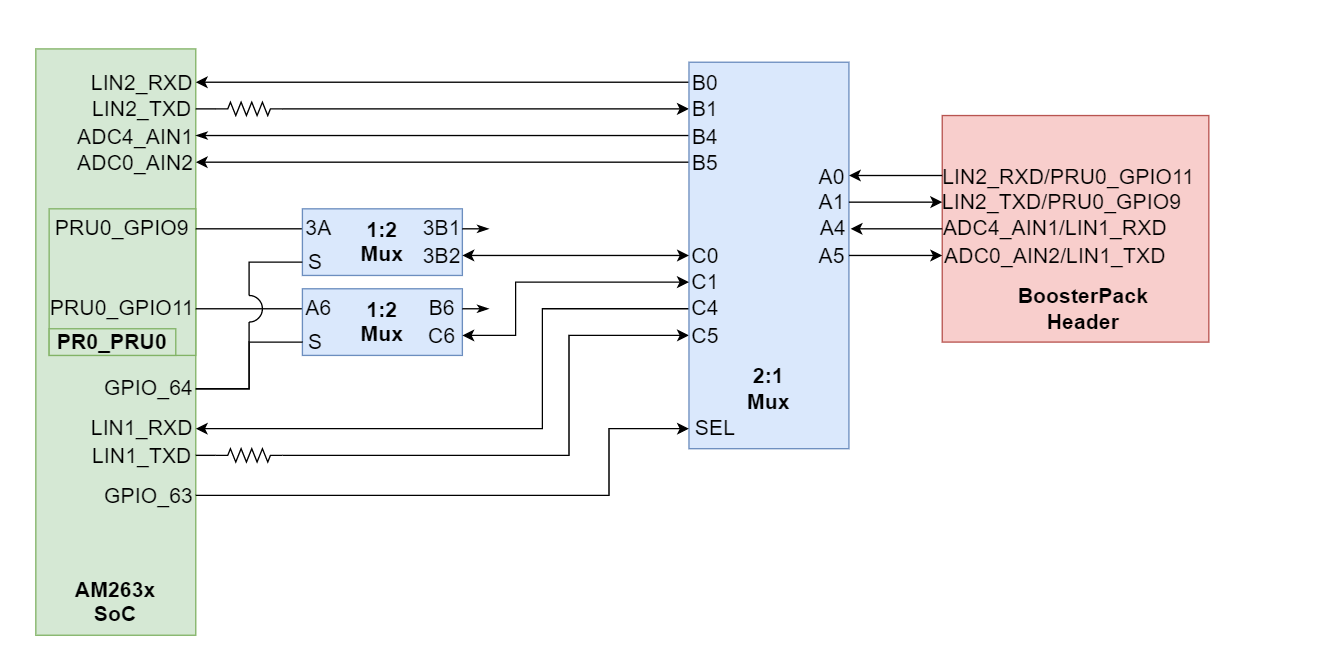

The AM263x LaunchPad supports Local Interconnect Network communication with two LIN instances mapped to the BoosterPack header.

Note: The AM263x does not have an

on-board LIN Transceiver

Figure 4-18 LIN Instances to BoosterPack

Header

Figure 4-18 LIN Instances to BoosterPack

HeaderBoth LIN instances are mapped to the alternate BoosterPack function 2:1 Mux. The alternate BoosterPack function mux also has mappings for ADC inputs and PRU0 GPIO signals.

Table 4-13 LIN 2:1 Mux

| GPIO_64 | GPIO_63 | Function of 2:1 Mux | Signals to BP Header |

|---|---|---|---|

| HIGH | LOW | Port A ↔ Port B | LIN2TX/RX, ADC4_AIN1, ADC0_AIN2 |

| HIGH | HIGH | Port A ↔ Port C | PRU GPIO11/9, LIN1TX/RX |

| LOW | LOW | Port A ↔ Port B | LIN2TX/RX, ADC4_AIN1, ADC0_AIN2 |

| LOW | HIGH | Port A ↔ Port C | NC, NC, LIN1 TX/RX |