SBAU374A May 2021 – May 2022 DAC12DL3200

- Abstract

- Trademarks

- 1Introduction

- 2Equipment

-

3Setup Procedure

- 3.1 Install the High Speed Data Converter (HSDC) Pro Software

- 3.2 Install the Configuration GUI Software

- 3.3 Connect the DAC12DL3200EVM and TSW14DL3200EVM

- 3.4 Connect the Power Supplies to the Boards (Power Off)

- 3.5 Connect the Signal Generators to the EVM (*RF Outputs Disabled Until Directed)

- 3.6 Turn On the TSW14DL3200EVM 12-V Power and Connect to the PC

- 3.7 Turn On the DAC12DL3200EVM 5-V Power Supply and Connect to the PC

- 3.8 Turn On the Signal Generator RF Outputs

- 3.9 Open the DAC12DL3200EVM GUI and Program the DAC and Clocks for Single Channel, NRZ Mode 2 Operation

- 3.10 Open the HSDC Software and Load the FPGA Image to the TSW14DL3200EVM

- 3.11 DxSTRB Timing Adjustment

- 4Other Modes of Operation

- 5Register Log File

- 6Device Configuration

- A Troubleshooting the DAC12DL3200EVM

- B DAC12DL3200EVM Onboard Clocking Configuration

1 Introduction

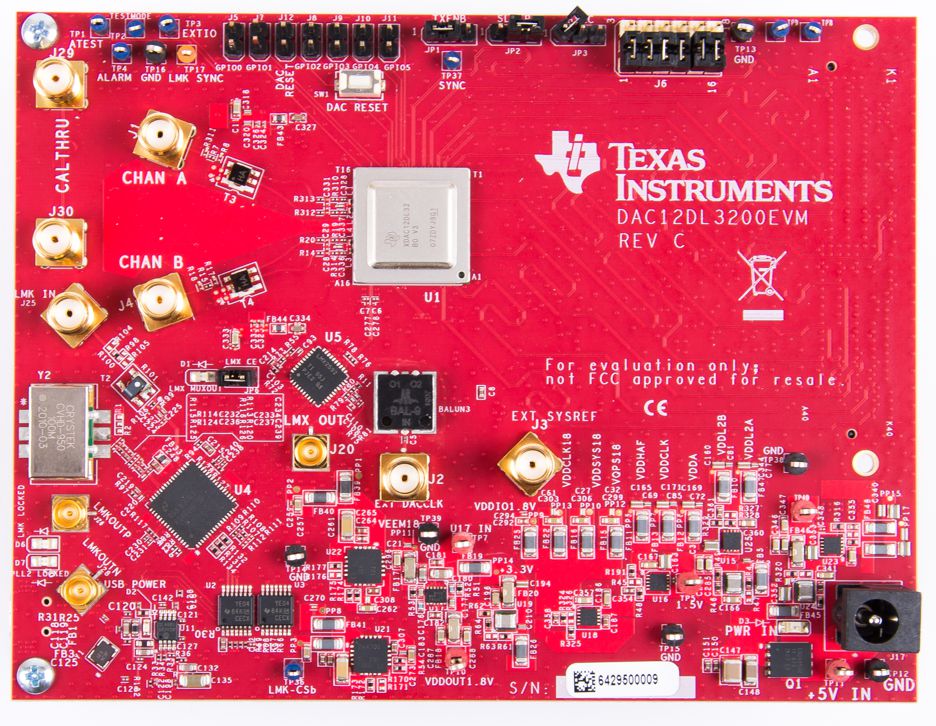

The DAC12DL3200 is a very low latency, dual-channel, 12-bit RF sampling digital-to-analog converter (DAC), capable of operating at sampling rates up to 3.2 Giga-samples per second (GSPS) in dual-channel mode, or 6.4 GSPS in single-channel mode. The DAC can transmit signal bandwidths beyond 2 GHz at carrier frequencies approaching 8 GHz when using multi-Nyquist output modes. The DAC12DL3200EVM device input data is transmitted over a high-speed LVDS interface. This evaluation board also includes the following important features:

- Transformer-coupled output allowing for a single-ended 50-Ω output signal up to 8 GHz

- The LMX2592 clock synthesizer as an option to generate the DAC sampling clock

- Transformer-coupled input clock option (board default setup) for quick setup with external clock sources

- LMK04828 clock synthesizer for DAC SYSREF and FPGA reference clock source

- Device register programming through USB connector and FTDI USB-to-SPI bus translator

- High-speed LVDS data input over a 400-pin FMC interface connector

Figure 1-1 DAC12DL3200EVM

Figure 1-1 DAC12DL3200EVMThe TI TSW14DL3200EVM pattern generator, when used with the TI High-Speed-Data-Converter (HSDC) Pro Software GUI, is used to send LVDS data test patterns to the DAC12DL3200EVM.

With proper hardware selection in the HSDC Pro software, the TSW14DL3200EVM is automatically configured to support the different modes of operation of the DAC12DL3200. The interface provides LVDS output data up to 1600 MSPS.