SBAU436A January 2024 – February 2024

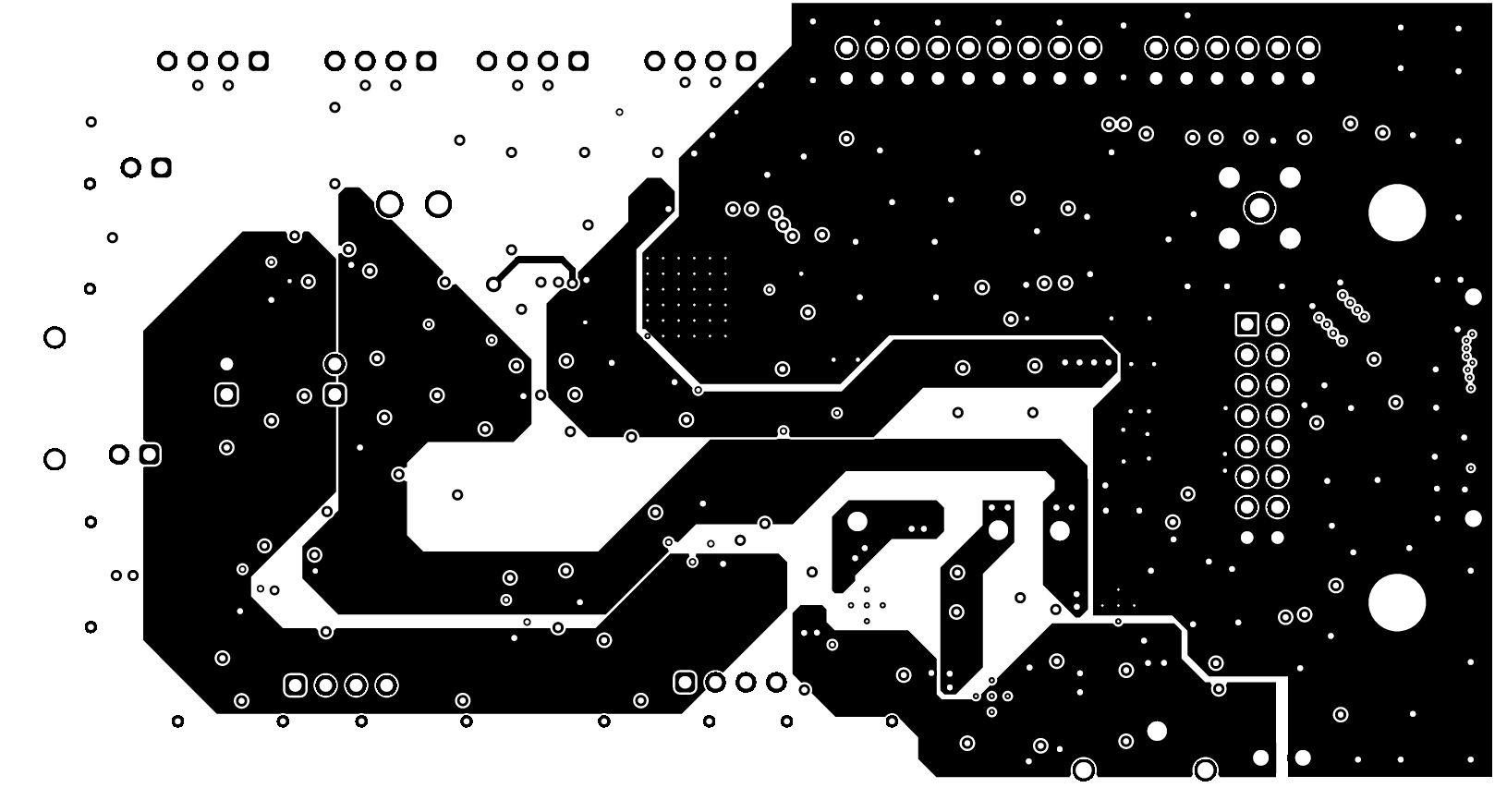

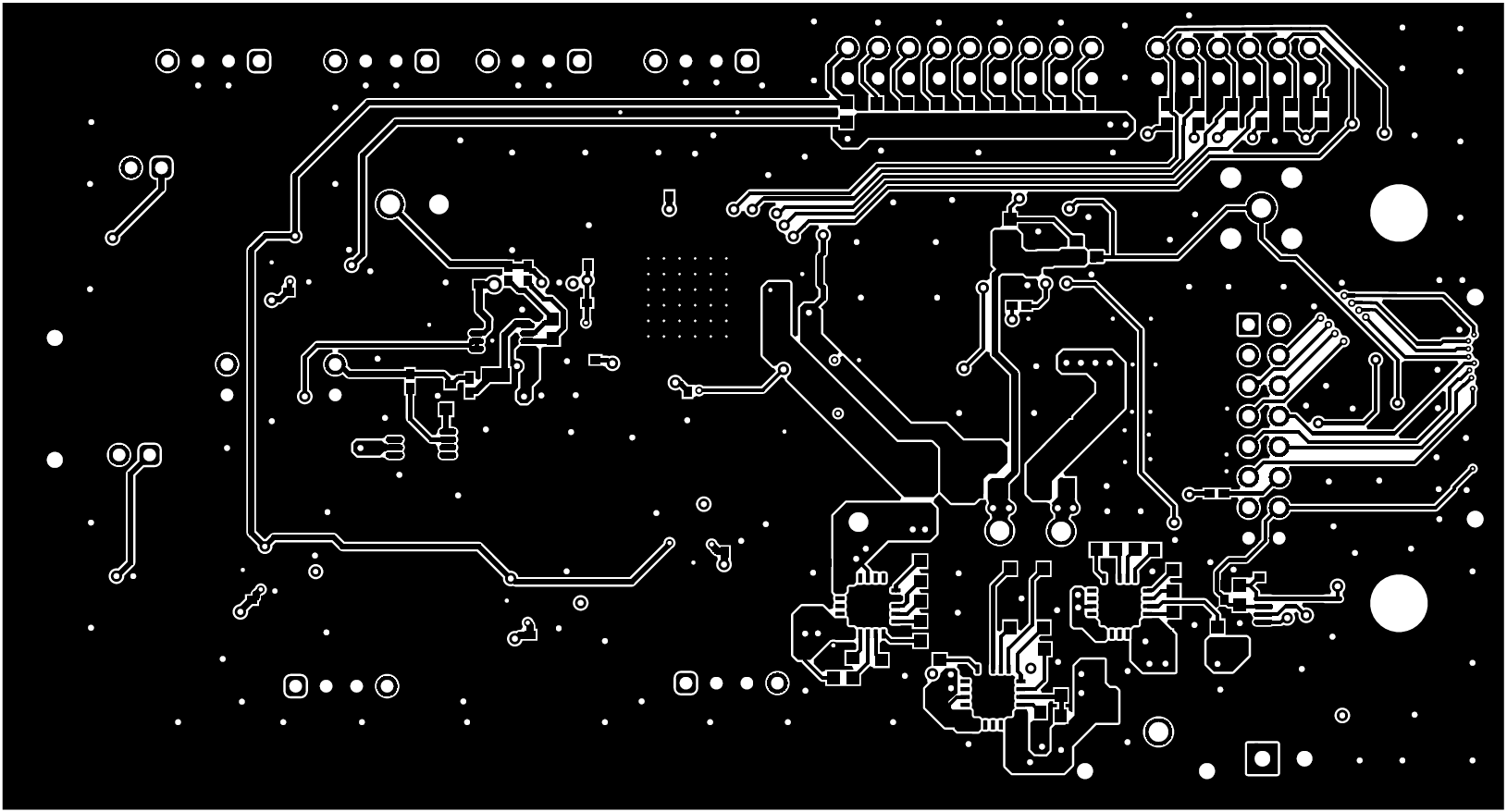

5.2 PCB Layouts

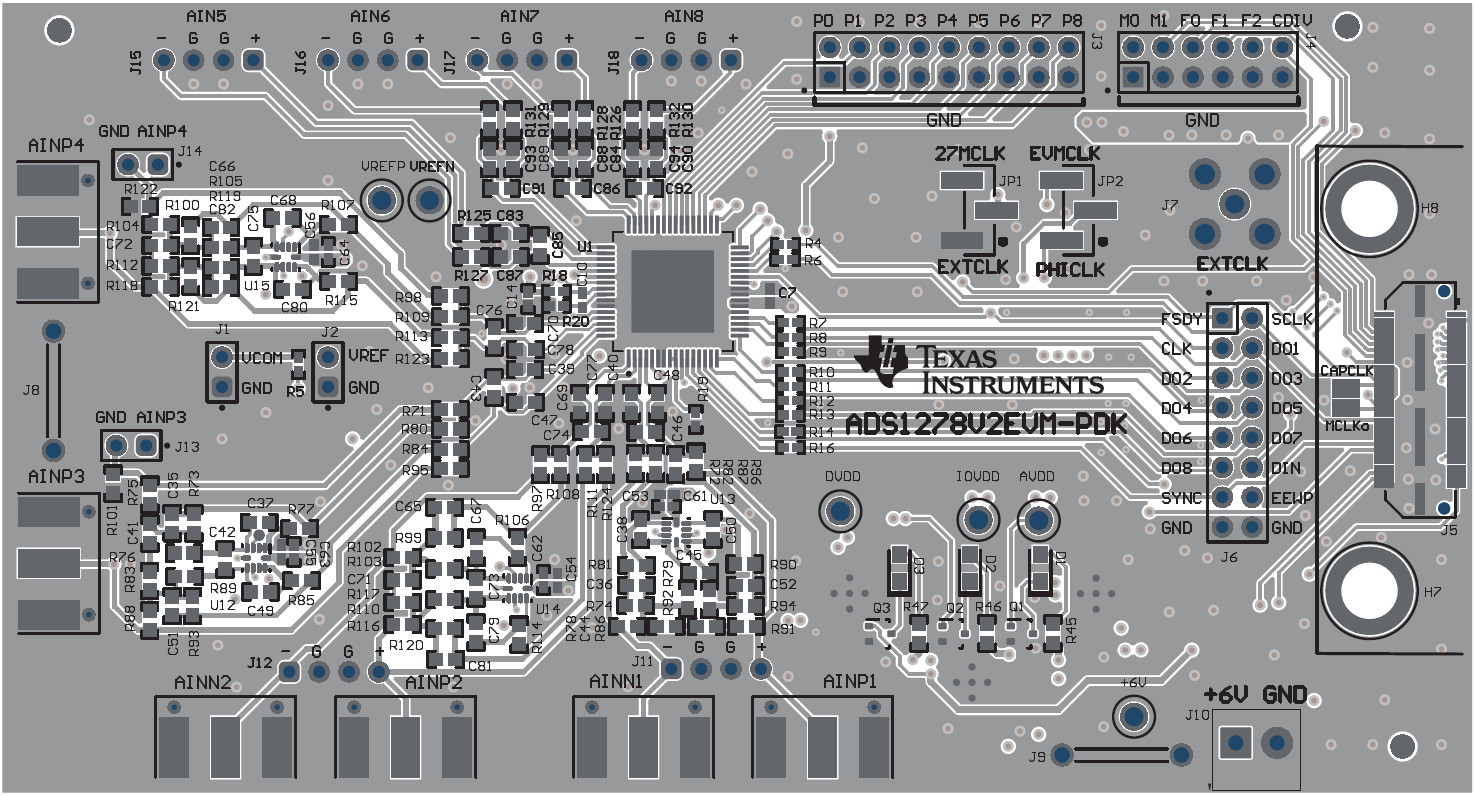

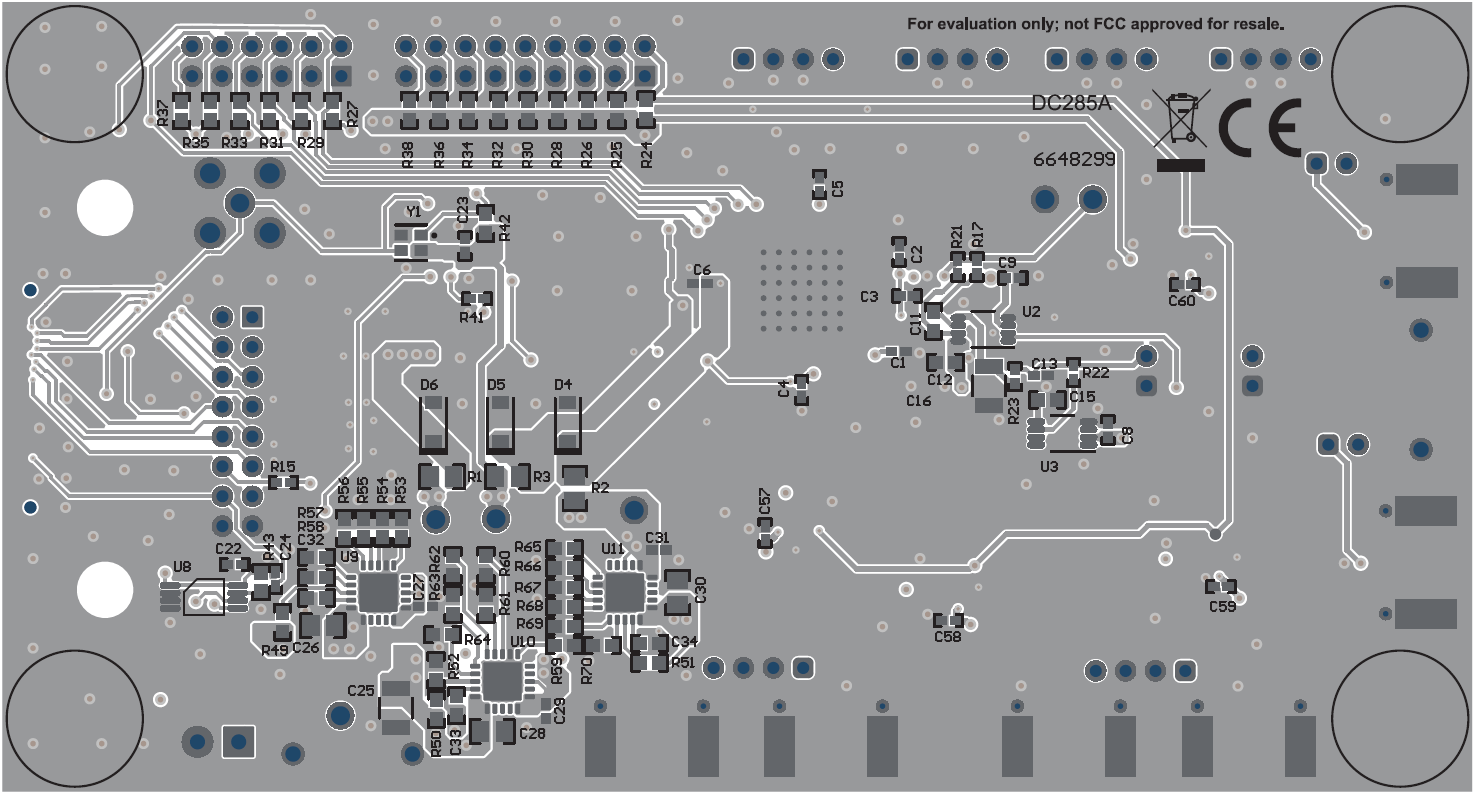

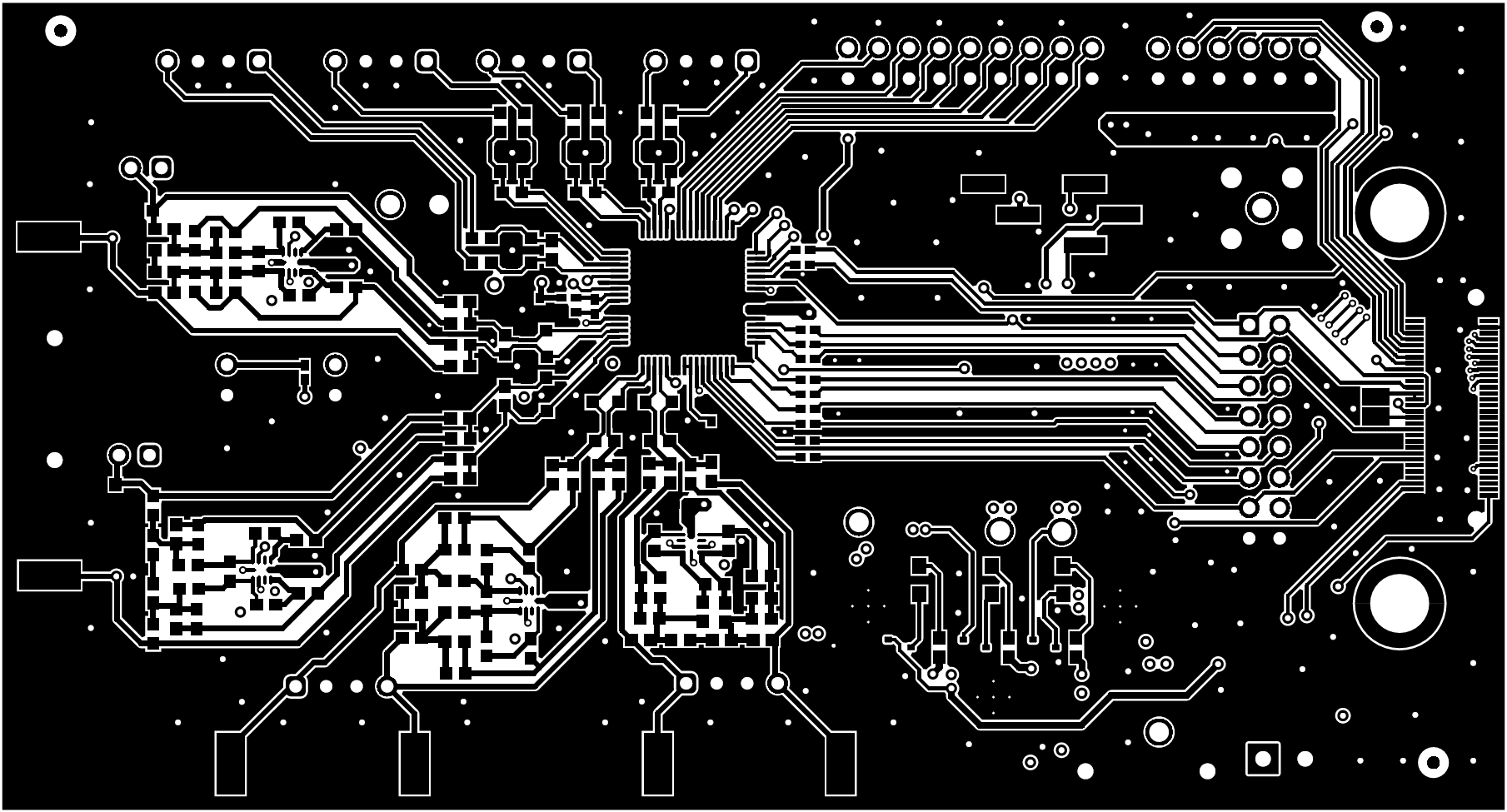

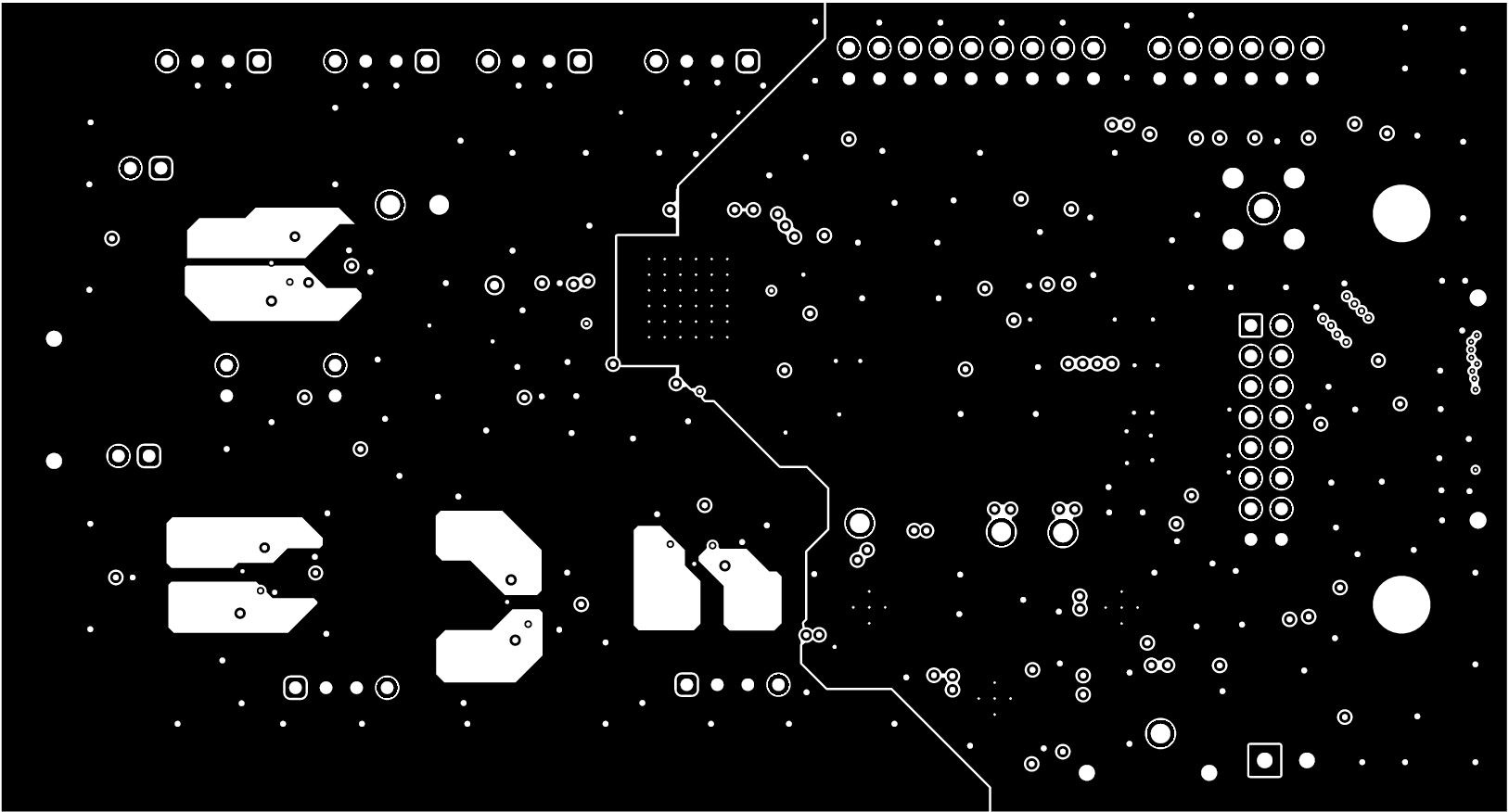

Figure 6-6 through Figure 6-11 show the PCB layouts for the ADS1278 EVM.

Figure 5-6 Top Side Composite Layout

Figure 5-6 Top Side Composite Layout Figure 5-7 Bottom Side Composite Layout

Figure 5-7 Bottom Side Composite Layout Figure 5-8 Top Signal Layer Layout

Figure 5-8 Top Signal Layer Layout Figure 5-9 Ground Layer Layout

Figure 5-9 Ground Layer Layout Figure 5-10 Power Layer Layout

Figure 5-10 Power Layer Layout Figure 5-11 Bottom Signal Layer Layout

Figure 5-11 Bottom Signal Layer Layout