SLUS900E December 2008 – August 2015

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6

Register Maps

- 7.6.1 I2C Read After Backup Mode

- 7.6.2

Normal Register Descriptions

- 7.6.2.1 SECONDS Register (address = 0x00) [reset = 0XXXXXXb]

- 7.6.2.2 MINUTES Register (address = 0x01) [reset = 1XXXXXXb]

- 7.6.2.3 CENT_HOURS Register (address = 0x02) [reset = XXXXXXXXb]

- 7.6.2.4 DAY Register (address = 0x03) [reset = 00000XXXb]

- 7.6.2.5 DATE Register (address = 0x04) [reset = 00XXXXXXb]

- 7.6.2.6 MONTH Register (address = 0x05) [reset = 000XXXXXb]

- 7.6.2.7 YEARS Register (address = 0x06) [reset = XXXXXXXXb]

- 7.6.2.8 CAL_CFG1 Register (address = 0x07) [reset = 10000000b]

- 7.6.2.9 TCH2 Register (address = 0x08) [reset = 10010000b]

- 7.6.2.10 CFG2 Register (address = 0x09) [reset = 10101010b]

- 7.6.3 Special Function Registers

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- D|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The typical application for the bq32000 is to provide precise time and date to a system. The backup power supply provides additional reliability by automatically switching over from the main supply when it drops under the voltage threshold.

8.2 Typical Application

The following design is a common application of the bq32000.

Figure 22. Typical Application Schematic

Figure 22. Typical Application Schematic

8.2.1 Design Requirements

The design requirement parameters are listed in the following table.

Table 5. Design Parameters

| DESIGN PARAMETER | REFERENCE | EXAMPLE VALUE |

|---|---|---|

| Supply Voltage | VCC | 3.3 V |

| Backup Supply | VBACK | BR1225 |

| Crystal Oscillator | XT | 32.768 kHz |

8.2.2 Detailed Design Procedure

8.2.2.1 Reading From a Register

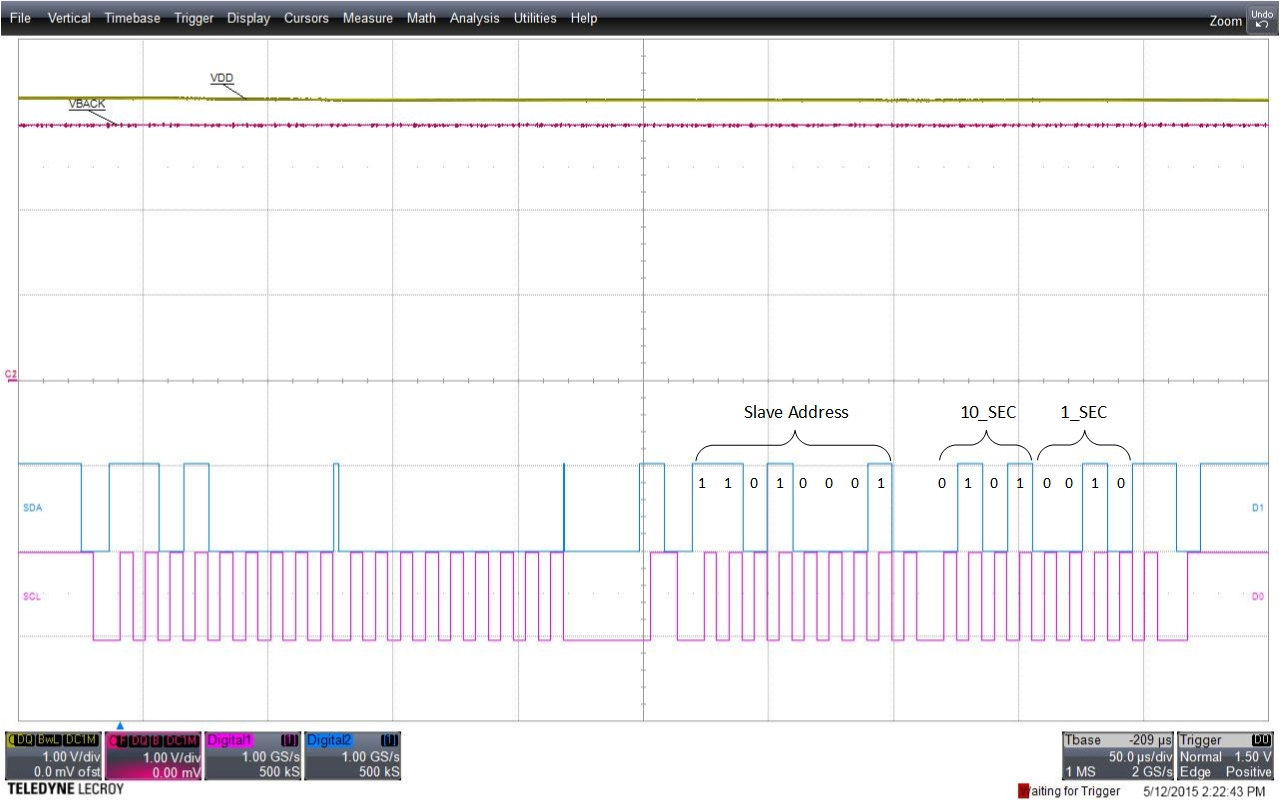

The report details the read-back of the SECONDS register. Figure 23 depicts the first condition that will be used as a benchmark to compare the values taken from the SECONDS register in the bq32000, to the oscilloscope’s internal PC time. In this example two modes of operation are demonstrated.

Condition 1. The main power supply, VCC, is greater than the backup power supply, VBACK, and the internal reference voltage, VREF. In this mode, the device's internal registers are fully operational with READ and WRITE access. Analyzing Figure 23, the known register values are compared to the system clock; in this case, the PC clock which is shown at the bottom of the screen capture.

The bq32000 during this condition is reading back [101][0010]= [5][2], which corresponds to 52 seconds at PC time of 2:22:43 PM.

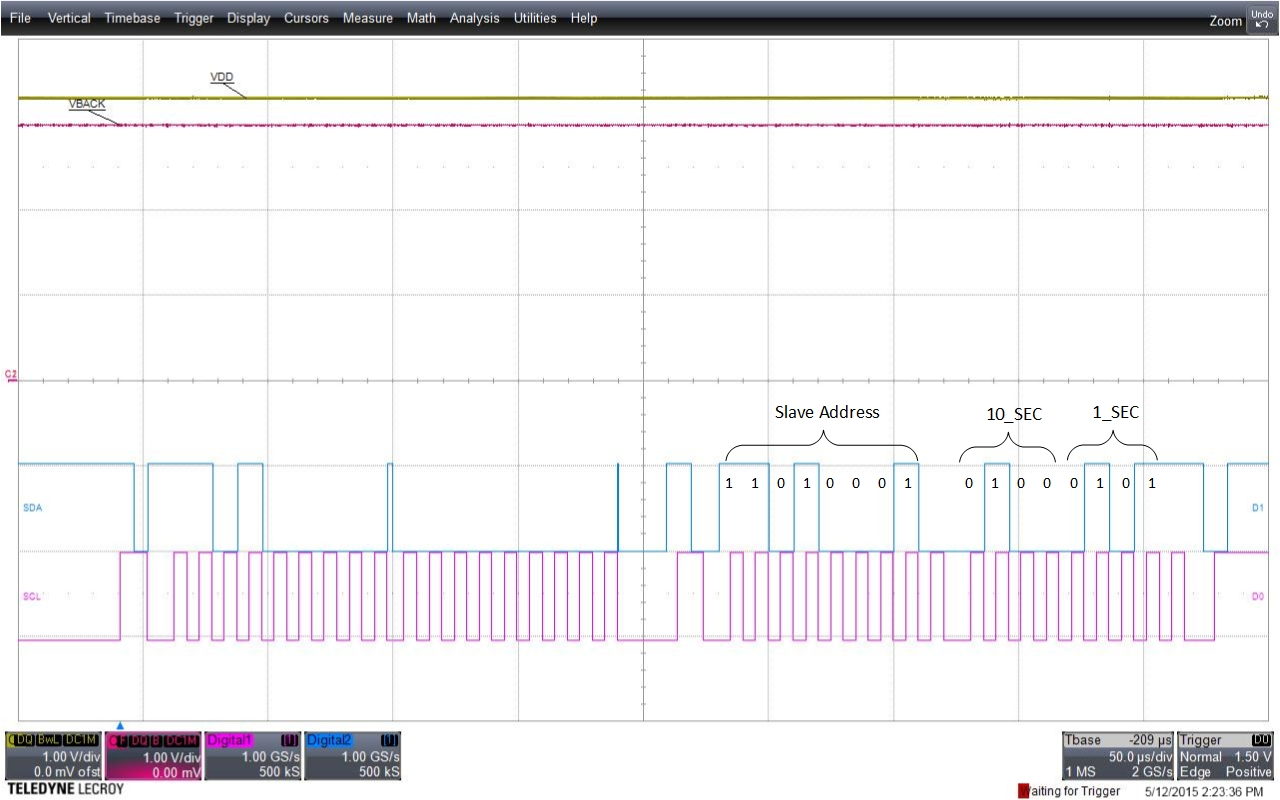

Condition 2. VCC is now lowered to 2 V (VBACK > VCC). In this mode, the I2C communications are halted. However, the internal time keeping registers maintain full functional operation and accuracy which will be available to be reliably read by the controller 1 second after the RTC switches from VBACK to VCC supply.

Condition 3. During this final test condition, the RTC is restored to operate from the main power supply and I2C communications are now fully functional.

Figure 24 demonstrates a read-back value from the SECONDS register of [100][0101]= [4][5], or 45 seconds at PC time of 2:23:36 PM. This proves that the bq32000 managed to accurately maintain the time keeping registers functional while the VCC dropped below VBACK.

8.2.2.2 Leap Year Compensation

The BQ32000 classifies a leap year as any year that is evenly divisible by 4. Using this rule allows for reliable leap year compensation until 2100. Years that fall outside this rule will need to be compensated for by the external controller.

8.2.2.3 Utilizing the Backup Supply

In order for the bq32000 to achieve a low backup supply current as specified in the Electrical Characteristics, the VCC pin must be initialized after every total power loss situation. Initialization Is achieved by powering on VCC with a voltage between 3 to 3.6 V for at least 1 ms immediately after the backup supply is connected. If the VCC is not powered on while connecting the backup supply, then the expected leakage current from VBACK will be much greater than specified.

8.2.3 Application Curves

Figure 23. Master and Slave I2C Communication for the SECONDS Register

Figure 23. Master and Slave I2C Communication for the SECONDS Register

Figure 24. Master and Slave I2C Communication for the SECONDS Register After Recovering From the Backup Supply

Figure 24. Master and Slave I2C Communication for the SECONDS Register After Recovering From the Backup Supply