SLLSEA8A January 2012 – March 2016 SN65LVCP114

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6

Register Maps

- 9.6.1

SN65LVCP114 Register Mapping Information

- 9.6.1.1 Register 0x00

- 9.6.1.2 Register 0x01

- 9.6.1.3 Register 0x02

- 9.6.1.4 Register 0x03

- 9.6.1.5 Register 0x04

- 9.6.1.6 Register 0x06

- 9.6.1.7 Register 0x07

- 9.6.1.8 Register 0x08

- 9.6.1.9 Register 0x0A

- 9.6.1.10 Register 0x0B

- 9.6.1.11 Register 0x0C

- 9.6.1.12 Register 0x0D

- 9.6.1.13 Register 0x0F

- 9.6.1.14 Register 0x10

- 9.6.1.15 Register 0x11

- 9.6.1.16 Register 0x12

- 9.6.1.17 Register Descriptions

- 9.6.1

SN65LVCP114 Register Mapping Information

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZJA|167

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9 Detailed Description

9.1 Overview

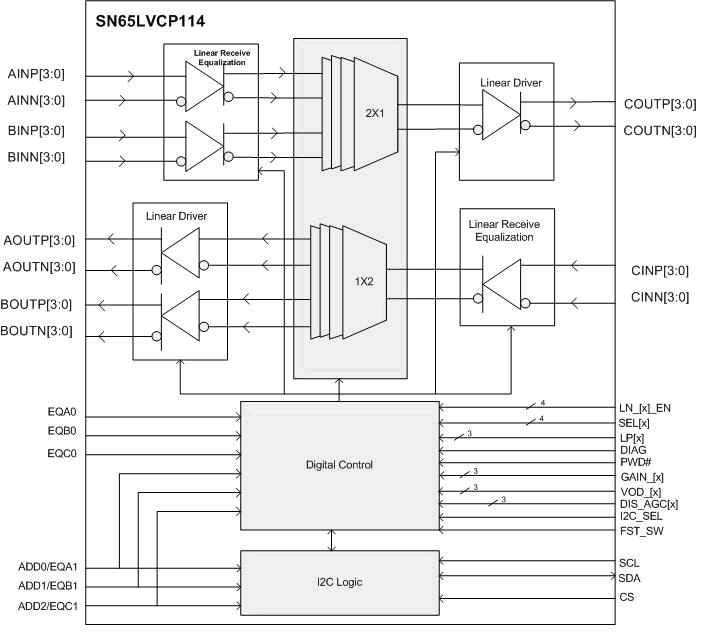

The SN65LVCP114 device is an asynchronous, protocol-agnostic, low-latency QUAD mux, linear-redriver optimized for use in systems operating at up to 14.2 Gbps. The device linearly compensates for channel loss in backplane and active-cable applications. The architecture of SN65LVCP114 linear-redriver is designed to work effectively with ASIC or FPGA products implementing digital equalization using decision feedback equalizer (DFE) technology. The SN65LVCP114 mux, linear-redriver preserves the integrity of the received signal, ensuring optimum DFE and system performance. The SN65LVCP114 device provides a low-power mux-demux, linear-redriver solution while at the same time extending the effectiveness of DFE. The SN65LVCP114 device supports 2:1 MUX and 1:2 DEMUX with independent lane switching. For each receiver port, equalization can be independent. All ports support loop-back configuration. Configuration can be done through GPIO or an I2C interface.

9.2 Functional Block Diagram

9.3 Feature Description

9.3.1 Power Down

Use a 5-kΩ pullup for normal operation. To power down the SN65LVCP114, tie this pin to GND. In power-down mode, Inputs are off, outputs are disabled, and I2C is reset. Power-down mode can be set, writing a 1 to register 0x00 bit 6.

9.3.2 Lane Enable

Each lane can be enabled individually using pin LN_x_EN or register 0x12[3:0]. This enables lane x for all ports.

Table 4. Lane Enable

| LN_x_EN/REGISTER 0x12[3:0] | FUNCTION |

|---|---|

| 0 | Lane disabled |

| 1 | Lane enabled |

9.3.3 Gain and Equalization

Equalization can be configured using EQx[1:0] pins or registers 0x03[3:0], 0x07[3:0], and 0x0B[3:0]. The SN65LVCP114 device includes several possible equalizations to select the optimum value. Also, the GAINx pin or registers 0x04[1:0], 0x08[1:0], and 0x0C[1:0] can be used to attenuate the input signal.

If input swing is larger than 600 mVpp, set gain to 0.5. Otherwise, set gain to 1.

Table 5. EQ Settings

| EQx[1:0] | REGISTER 0x03[3:0], 0x07[3:0], 0x0B[3:0] | PEAKING (dB) |

|---|---|---|

| 0b00 | 0b0XXX | 1.3 |

| 0b0Z | 0b1000 | 2 |

| 0b01 | 0b1001 | 3.6 |

| 0bZ0 | 0b1010 | 5 |

| 0bZZ | 0b1011 | 6.5 |

| 0bZ1 | 0b1100 | 8.3 |

| 0b10 | 0b1101 | 10 |

| 0b1Z | 0b1110 | 11.9 |

| 0b11 | 0b111 | 13.9 |

Table 6. RX DC Gain

| GAINx | REGISTERS 0x04[1:0], 0x08[1:0], 0x0C[1:0] | GAIN |

|---|---|---|

| 0 | 0bX0 | 0.5 (–6 dB) |

| 1 | 0bX1 | 1 (0 dB) |

9.3.4 VOD

Output swing can be selected between two ranges with an associated gain. Notice the range sets a maximum value not a constant value.

Table 7. Output Swing

| VOD_x | REGISTERS 0x04[5:4], 0x08[5:4], 0x0C[5:4] | MAXIMUM VALUE | GAIN |

|---|---|---|---|

| 0 | 0b01 | 0.6 V | 1.1 (1 dB) |

| 1 | 0b00, 0b10, 0b11 | 1.2 V | 2.2 (6.8 dB) |

9.3.5 AGC

When AGC is enabled, the part-to-part gain variation can be reduced. AGC can be disabled for each port through DIS_AGCx or registers 0x02[0], 0x06[0], and 0x0A[0].

Table 8. AGC Enable

| DIS_AGCx/REGISTERS 0x02[0], 0x06[0], 0x0A[0] | FUNCTION |

|---|---|

| 0 | AGC loop enabled |

| 1 | AGC loop disabled |

9.3.6 GPIO or I2C Configuration

To configure this device using GPIO, set I2C_SEL = LOW. Using GIO, you have access to the most of the configuration, to power down the device, control equalization, select port, select VOD range, set loop-back mode, set diagnostic mode, enable lanes, enable AGC, select gain, and enable fast switching.

To configure this device using I2C set I2C_SEL = HIGH. Besides the configuration you have with GPIO, using I2C allows you to disable outputs, power-down inputs and switch polarity of outputs. In this mode, use pins ADDx to set I2C address. See Programming for a detailed explanation.

9.3.7 Fast Switching

Idle outputs can be disabled or squelched. When outputs are squelched, switching is faster; when outputs are disabled, power is saved. This configuration is done with the FST_SW pin or registers 0x02[3], 0x06[3], and 0x0A[3].

Table 9. Fast Switching

| FST_SW/REGISTER 0x02[3], 0x06[3], 0x0A[3] | FUNCTION |

|---|---|

| 0 | Disable idle outputs |

| 1 | Squelch idle outputs |

9.3.8 Power-Down Input Stages

Each port can power down its input stages to save power when not used. Power down affects all the lanes of the port; to configure it, use registers 0x03[7], 0x07[7], and 0x08[7] for port A, B, and C respectively.

Table 10. Power Down

| REGISTERS 0x03[7], 0x07[7], 0x08[7] | FUNCTION |

|---|---|

| 0 | Normal |

| 1 | Power down |

9.3.9 Disable Output Lanes

The SN65LVCP114 device can disable every output lane independently. Use register 0x02[7:4] to disable output lanes of port A, register 0x06[7:4] to disable output lanes of port B, and register 0x0A[7:4] to disable output lanes of port C.

Table 11. Disable Output Lanes

| REGISTERS 0x03[7], 0x07[7], 0x08[7] | FUNCTION |

|---|---|

| 0 | Enabled |

| 1 | Disabled |

9.3.10 Polarity Switch

Every lane can switch its polarity independently. Port A is configured through register 0x10[3:0], port B is configured through register 0x10[7:4], and port C is configured through register 0x11[3:0]. See Table 16 for a detailed explanation.

9.4 Device Functional Modes

The SN65LVCP114 device has three modes of operation: Normal mode, loopback mode, and diagnostic mode. For all possible combinations of these modes, see Table 2.

9.4.1 Normal Mode

In this mode, the SN65LVCP114 functions like a switch. C port will connect to A or B port depending on values of SELx or register 0x01[3:0], each lane is configured independently.

Table 12. Port Select

| SELx/REGISTER 0x01[3:0] | PORT CONNECTED TO C |

|---|---|

| 0 | A |

| 1 | B |

9.4.2 Loopback

In loopback mode, the selected port transmits on its output what it is receiving on its input. Each port has independent loopback configuration. This configuration can be selected using the LPx pins or register 0x01[6:4]. See Figure 14 for a graphical representation.

Table 13. Loopback Mode

| LPx/REGISTER 0x01[6:4] | FUNCTION |

|---|---|

| 0 | Loop disabled |

| 1 | Loop enabled |

9.4.3 Diagnostic

When in diagnostic mode, data incoming on port C is reflected in both A and B ports. Data outgoing on port C depends on the value of SELx. This mode can be selected using DIAG pin or register 0x01[7]. See Figure 15 for a graphical representation.

Table 14. Diagnostic Mode

| DIAG/REGISTER 0x01[7] | FUNCTION |

|---|---|

| 0 | Diagnostic disabled |

| 1 | Diagnostic enabled |

9.5 Programming

9.5.1 Two-Wire Serial Interface and Control Logic

The SN65LVCP114 device uses a 2-wire serial interface for digital control. The two circuit inputs, SDA and SCL, are driven, respectively, by the serial data and serial clock from a microprocessor, for example. The SDA and SCL pins require external 10-kΩ pullups to VCC.

The 2-wire interface allows write access to the internal memory map to modify control registers and read access to read out the control signals. The SN65LVCP114 device is a slave device only, which means that it cannot initiate a transmission itself; it always relies on the availability of the SCL signal for the duration of the transmission. The master device provides the clock signal as well as the START and STOP commands. The protocol for a data transmission is as follows:

- START command

- 7-bit slave address (0000ADD[2:0]) followed by an 8th bit which is the data direction bit (R/W). A zero indicates a WRITE and a 1 indicates a READ. The ADD[2:0] address bits change with the status of the ADD2, ADD1, and ADD0 device pins, respectively. If the pins are left floating or pulled down, the 7-bit slave address is 0000000.

- 8-bit register address

- 8-bit register data word

- STOP command

Regarding timing, the SN65LVCP114 device is I2C compatible. Figure 16 shows the typical timing, and Figure 17 shows the data transfer. Table 15 defines the parameters forFigure 16.

Bus Idle: Both SDA and SCL lines remain HIGH

Start data transfer: A change in the state of the SDA line, from HIGH to LOW, while the SCL line is HIGH, defines a START condition (S). Each data transfer is initiated with a START condition.

Stop Data Transfer:A change in the state of the SDA line from LOW to HIGH while the SCL line is HIGH defines a STOP condition (P). Each data transfer is terminated with a STOP condition; however, if the master still must communicate on the bus, it can generate a repeated START condition and address another slave without first generating a STOP condition.

Data Transfer: The number of data bytes transferred between a START and a STOP condition is not limited and is determined by the master device. The receiver acknowledges the transfer of data.

Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge bit. The transmitter releases the SDA line, and a device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse. Setup and hold times must be considered. When a slave-receiver does not acknowledge the slave address, the data line must be left HIGH by the slave. The master can then generate a STOP condition to abort the transfer. If the slave-receiver does acknowledge the slave address but some time later in the transfer cannot receive any more data bytes, the master must abort the transfer. This is indicated by the slave generating the not acknowledge on the first byte to follow. The slave leaves the data line HIGH and the master generates the STOP condition.

Figure 16. Two-Wire Serial Interface Timing Diagram

Figure 16. Two-Wire Serial Interface Timing Diagram

Table 15. Two-Wire Serial Interface Timing Diagram Definitions

| PARAMETER | MIN | MAX | UNIT | |

|---|---|---|---|---|

| fSCL | SCL clock frequency | 400 | kHz | |

| tBUF | Bus free time between START and STOP conditions | 1.3 | μs | |

| tHDSTA | Hold time after repeated START condition. After this period, the first clock pulse is generated. | 0.6 | μs | |

| tLOW | Low period of the SCL clock | 1.3 | μs | |

| tHIGH | High period of the SCL clock | 0.6 | μs | |

| tSUSTA | Setup time for a repeated START condition | 0.6 | μs | |

| tHDDAT | Data hold time | 0 | μs | |

| tSUDAT | Data setup time | 100 | ns | |

| tR | Rise time of both SDA and SCL signals | 300 | ns | |

| tF | Fall time of both SDA and SCL signals | 300 | ns | |

| tSUSTO | Setup time for STOP condition | 0.6 | μs | |

Figure 17. Two-Wire Serial Interface Data Transfer

Figure 17. Two-Wire Serial Interface Data Transfer

9.6 Register Maps

9.6.1 SN65LVCP114 Register Mapping Information

9.6.1.1 Register 0x00

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| SW_GPIO | PWRDOWN | RSVD |

9.6.1.2 Register 0x01

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| DIAG | LOOP[C] | LOOP[B] | LOOP[A] | SEL[3] | SEL[2] | SEL[1] | SEL[0] |

9.6.1.3 Register 0x02

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| OUT_DIS_0 | OUT_DIS_1 | OUT_DIS_2 | OUT_DIS_3 | FAST_SW | RSVD | DIS_AGC |

9.6.1.4 Register 0x03

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| INOFF | RSVD | RSVD | RSVD | EQ3 | EQ2 | EQ1 | EQ0 |

9.6.1.5 Register 0x04

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| VOD1 | VOD0 | GAIN1 | GAIN0 |

9.6.1.6 Register 0x06

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| OUT_DIS_0 | OUT_DIS_1 | OUT_DIS_2 | OUT_DIS_3 | FAST_SW | RSVD | DIS_AGC |

9.6.1.7 Register 0x07

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| INOFF | RSVD | RSVD | RSVD | EQ3 | EQ2 | EQ1 | EQ0 |

9.6.1.8 Register 0x08

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| VOD1 | VOD0 | GAIN1 | GAIN0 |

9.6.1.9 Register 0x0A

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| OUT_DIS_0 | OUT_DIS_1 | OUT_DIS_2 | OUT_DIS_3 | FAST_SW | RSVD | DIS_AGC |

9.6.1.10 Register 0x0B

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| INOFF | RSVD | RSVD | RSVD | EQ3 | EQ2 | EQ1 | EQ0 |

9.6.1.11 Register 0x0C

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| VOD1 | VOD0 | GAIN1 | GAIN0 |

9.6.1.12 Register 0x0D

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD |

9.6.1.13 Register 0x0F

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD |

9.6.1.14 Register 0x10

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| POL_B[3] | POL_B[2] | POL_B[1] | POL_B[0] | POL_A[3] | POL_A[2] | POL_A[1] | POL_A[0] |

9.6.1.15 Register 0x11

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| POL_C[3] | POL_C[2] | POL_C[1] | POL_C[0] |

9.6.1.16 Register 0x12

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|---|---|---|---|---|---|---|

| LN_EN[3] | LN_EN[2] | LN_EN[1] | LN_EN[0] |

9.6.1.17 Register Descriptions

Table 16. SN65LVCP114 Register Descriptions

| REGISTER | BIT | SYMBOL | FUNCTION | DEFAULT | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 0x00 | 7 | SW_GPIO | Switching logic is controlled by GPIO or I2C: 1 = GPIO control 0 = I2C control |

00000000 | ||||||

| 6 | PWRDOWN | Power down the device: 0 = Normal operation 1 = Power down |

||||||||

| 5 | ||||||||||

| 4 | ||||||||||

| 3 | ||||||||||

| 2 | ||||||||||

| 1 | ||||||||||

| 0 | RSVD | For TI use only | ||||||||

| 0x01 | 7 | DIAG | Enables Diag Mode: 0 = Disable 1 = Enable |

00000000 | ||||||

| 6 | LOOP[C] | Enables port C loopback: 0 = Disable 1 = Enable |

||||||||

| 5 | LOOP[B] | Enables port B loopback: 0 = Disable 1 = Enable |

||||||||

| 4 | LOOP[A] | Enables port A loopback: 0 = Disable 1 = Enable |

||||||||

| 3 | SEL[3] | Lane 3, port A or port B switch control: 0 = Port A selected 1 = Port B selected |

||||||||

| 2 | SEL[2] | Lane 2, port A or port B switch control: 0 = Port A selected 1 = Port B selected |

||||||||

| 1 | SEL[1] | Lane 1, port A or port B switch control: 0 = Port A selected 1 = Port B selected |

||||||||

| 0 | SEL[0] | Lane 0, port A or port B switch control: 0 = Port A selected 1 = Port B selected |

||||||||

| 0x02 0x06 0x0A |

7 | OUT_DIS0 | Disables output lane 0: 0 = Enable 1 = Disable |

00001100 | ||||||

| 6 | OUT_DIS1 | Disables output lane 1: 0 = Enable 1 = Disable |

||||||||

| 5 | OUT_DIS2 | Disables output lane 2: 0 = Enable 1 = Disable |

||||||||

| 4 | OUT_DIS3 | Disables output lane 3: 0 = Enable 1 = Disable |

||||||||

| 3 | FAST_SW | Fast switch: 0 = Idle outputs are disabled (save power) 1 = Idle outputs are squelched (fast switch time) |

||||||||

| 2 | RSVD | For TI use only | ||||||||

| 1 | ||||||||||

| 0 | DIS_AGC | AGC loop: 0 = Enable 1 = Disable |

||||||||

| 0x03 0x07 0x0B |

7 | IN_OFF | Power down input stages: 0 = Normal 1 = Power down |

00000000 | ||||||

| 6 | RSVD | For TI use only | ||||||||

| 5 | RSVD | For TI use only | ||||||||

| 4 | RSVD | For TI use only | ||||||||

| 3 | EQ3 | Selects peaking equalization. Register 0x03 configures PortA, 0x07 configures port B and 0x0B configures port C. Refer to table x in feature description for detailed information. | ||||||||

| 0x04 0x08 0x0C |

7 | 00000000 | ||||||||

| 6 | ||||||||||

| 5 | VOD1 | VOD control [VOD1:VOD0]: 00 = 1200 mV maximum 01 = 600 mV maximum 10 = 1200 mV maximum 11 = 1200 mV maximum |

||||||||

| 4 | VOD0 | |||||||||

| 3 | ||||||||||

| 2 | ||||||||||

| 1 | GAIN1 | GAIN control [GAIN1:GAIN0]: 00 = 0.5 01 = 1 10 = 0.5 11 = 1 |

||||||||

| 0 | GAIN0 | |||||||||

| 0x05 0x09 0x0E |

7 | 00000000 | ||||||||

| 6 | ||||||||||

| 5 | ||||||||||

| 4 | ||||||||||

| 3 | ||||||||||

| 2 | ||||||||||

| 1 | ||||||||||

| 0 | ||||||||||

| 0x0D | 7 | RSVD | For TI use only | 00000000 | ||||||

| 6 | RSVD | For TI use only | ||||||||

| 5 | RSVD | For TI use only | ||||||||

| 4 | RSVD | For TI use only | ||||||||

| 3 | RSVD | For TI use only | ||||||||

| 2 | RSVD | For TI use only | ||||||||

| 1 | RSVD | For TI use only | ||||||||

| 0 | RSVD | For TI use only | ||||||||

| 0x0F | 7 | RSVD | For TI use only | 00010001 | ||||||

| 6 | RSVD | For TI use only | ||||||||

| 5 | RSVD | For TI use only | ||||||||

| 4 | RSVD | For TI use only | ||||||||

| 3 | RSVD | For TI use only | ||||||||

| 2 | RSVD | For TI use only | ||||||||

| 1 | RSVD | For TI use only | ||||||||

| 0 | RSVD | For TI use only | ||||||||

| 0x10 | 7 | POL_B[3] | Polarity switch of output lane 3 of port B: 0 = Normal 1 = Switched |

00000000 | ||||||

| 6 | POL_B[2] | Polarity switch of output lane 2 of port B: 0 = Normal 1 = Switched |

||||||||

| 5 | POL_B[1] | Polarity switch of output lane 1 of port B: 0 = Normal 1 = Switched |

||||||||

| 4 | POL_B[0] | Polarity switch of output lane 0 of port B 0 = Normal 1 = Switched |

||||||||

| 3 | POL_A[3] | Polarity switch of output lane 3 of port A: 0 = Normal 1 = Switched |

||||||||

| 2 | POL_A[2] | Polarity switch of output lane 2 of port A: 0 = Normal 1 = Switched |

||||||||

| 1 | POL_A[1] | Polarity switch of output lane 1 of port A: 0 = Normal 1 = Switched |

||||||||

| 0 | POL_A[0] | Polarity switch of output lane 0 of port A: 0 = Normal 1 = Switched |

||||||||

| 0x11 | 7 | 00000000 | ||||||||

| 6 | ||||||||||

| 5 | ||||||||||

| 4 | ||||||||||

| 3 | POL_C[3] | Polarity switch of output lane 3 of port C: 0 = Normal 1 = Switched |

||||||||

| 2 | POL_C[2] | Polarity switch of output lane 2 of port C: 0 = Normal 1 = Switched |

||||||||

| 1 | POL_C[1] | Polarity switch of output lane 1 of port C: 0 = Normal 1 = Switched |

||||||||

| 0 | POL_C[0] | Polarity switch of output lane 0 of port C: 0 = Normal 1 = Switched |

||||||||

| 0x12 | 7 | 00001111 | ||||||||

| 6 | ||||||||||

| 5 | ||||||||||

| 4 | ||||||||||

| 3 | LN_EN_3 | Lane 3 of ports A, B, and C: 0 = Disable 1 = Enable |

||||||||

| 2 | LN_EN_2 | Lane 2 of ports A, B, and C: 0 = Disable 1 = Enable |

||||||||

| 1 | LN_EN_1 | Lane 1 of ports A, B, and C: 0 = Disable 1 = Enable |

||||||||

| 0 | LN_EN_0 | Lane 0 of ports A, B, and C: 0 = Disable 1 = Enable |

||||||||