SNAS854 February 2023 TDC1000-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PW|28

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6.8 Typical Characteristics

At TA = 25°C, unless otherwise noted.

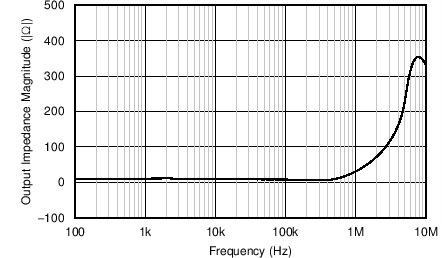

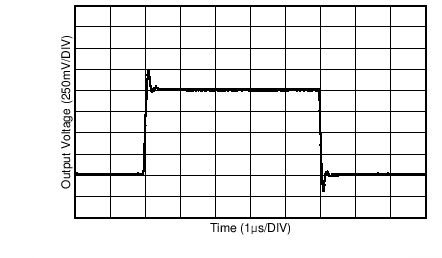

| VDD = VIO = 3.7 V | Capacitive Feedback Mode | RL = 1 kΩ |

| VDD = VIO = 3.1 V | Capacitive Feedback Mode | RL = ∞ |

| VDD = VIO = 3.7 V | Resistive Feedback Mode | RL = 1 kΩ |

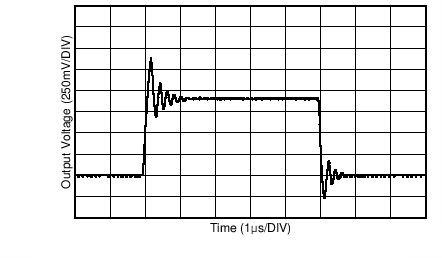

| VIN = 100 mV | fIN = 100 kHz | |

| VDD = VIO = 3.7 V | Capacitive Feedback Mode | RL = 100 kΩ |

| CIN = 300 pF |

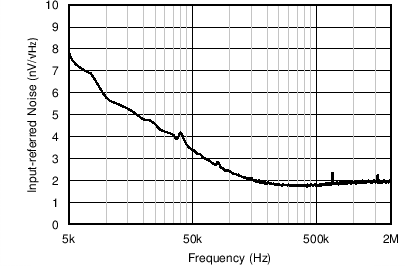

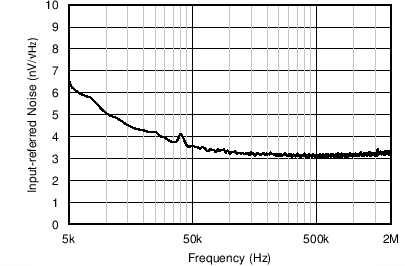

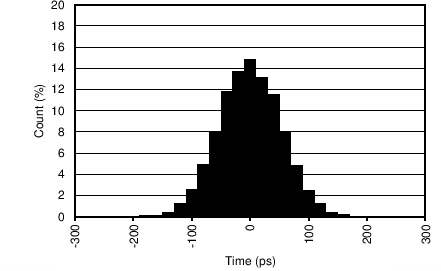

| VDD = VIO = 5 V | LNA Capacitive Feedback Mode | PGA Gain of 6 dB |

| VIN = 100 mV | fIN = 1 MHz | |

| (See GUID-72D520D8-3AB2-4ABC-B20F-282E41D31FC0.html#SNAS6485768) | Count ≥ 10000 |

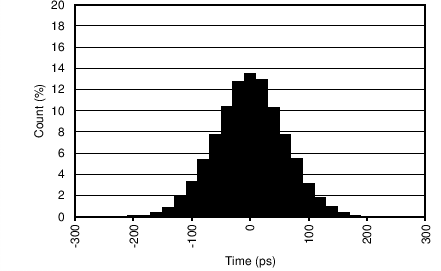

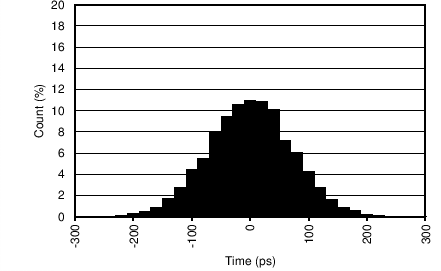

| VDD = VIO = 3.7 V | LNA Capacitive Feedback Mode | PGA Gain of 6 dB |

| VIN = 100 mV | fIN = 1 MHz | |

| TA = –40°C | (See GUID-72D520D8-3AB2-4ABC-B20F-282E41D31FC0.html#SNAS6485768) | Count ≥ 10000 |

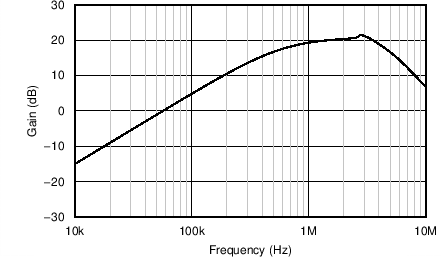

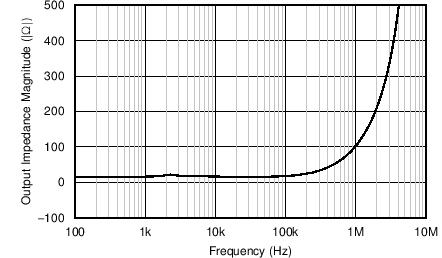

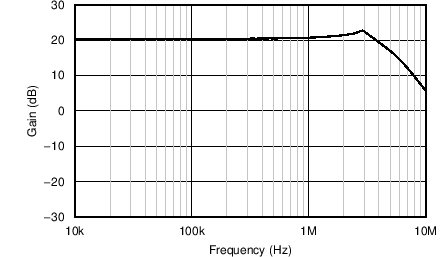

| VDD = VIO = 3.7 V | Gain of 21 dB | RL = 1 kΩ |

| VDD = VIO = 3.7 V | Gain of 21 dB | RL = ∞ |

| VDD = VIO = 3.7 V | Gain of 21 dB | RL = 100 kΩ |

| VIN = 100 mV | fIN = 100 kHz | |

| VDD = VIO = 3.7 V | Gain of 21 dB | RL = 100 kΩ |

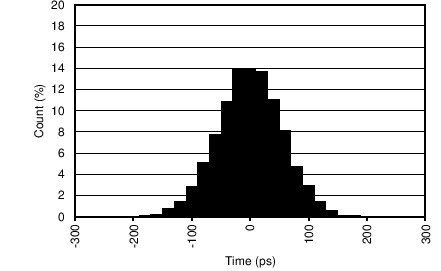

| VDD = VIO = 3.7 V | LNA Capacitive Feedback Mode | PGA Gain of 6 dB |

| VIN = 100 mV | fIN = 1 MHz | |

| TA = 25°C | (See GUID-72D520D8-3AB2-4ABC-B20F-282E41D31FC0.html#SNAS6485768) | Count ≥ 10000 |

| VDD = VIO = 3.7 V | LNA Capacitive Feedback Mode | PGA Gain of 6 dB |

| VIN = 100 mV | fIN = 1 MHz | |

| TA = 125°C | (See GUID-72D520D8-3AB2-4ABC-B20F-282E41D31FC0.html#SNAS6485768) | Count ≥ 10000 |