SBOS784C November 2016 – January 2019 TLV172 , TLV2172 , TLV4172

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9.2.3 Application Curve

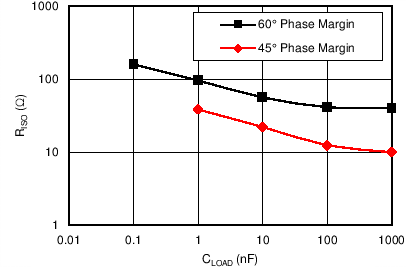

The values of RISO that yield phase margins of 45º and 60º for various capacitive loads are determined using the described methodology. Figure 31 shows the results.

Figure 31. Isolation Resistor Required for Various Capacitive Loads to Achieve a Target Phase Margin

Figure 31. Isolation Resistor Required for Various Capacitive Loads to Achieve a Target Phase Margin