SLAS520E February 2007 – December 2014 TLV320AIC3101

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Simplified Diagram

- 5 Revision History

- 6 Description (continued)

- 7 Device Comparison Table

- 8 Pin Configuration and Functions

- 9 Specifications

- 10Parameter Measurement Information

-

11Detailed Description

- 11.1 Overview

- 11.2 Functional Block Diagram

- 11.3

Feature Description

- 11.3.1 Hardware Reset

- 11.3.2 Digital Audio Data Serial Interface

- 11.3.3 Audio Data Converters

- 11.3.4 Audio Analog Inputs

- 11.3.5 Analog Fully Differential Line Output Drivers

- 11.3.6 Analog High-Power Output Drivers

- 11.3.7 Input Impedance and VCM Control

- 11.3.8 MICBIAS Generation

- 11.3.9 Short-Circuit Output Protection

- 11.3.10 Jack/Headset Detection

- 11.4 Device Functional Modes

- 11.5 Programming

- 11.6 Register Maps

- 11.7 Output Stage Volume Controls

- 12Application and Implementation

- 13Power Supply Recommendations

- 14Layout

- 15Device and Documentation Support

- 16Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RHB|32

Thermal pad, mechanical data (Package|Pins)

- RHB|32

Orderable Information

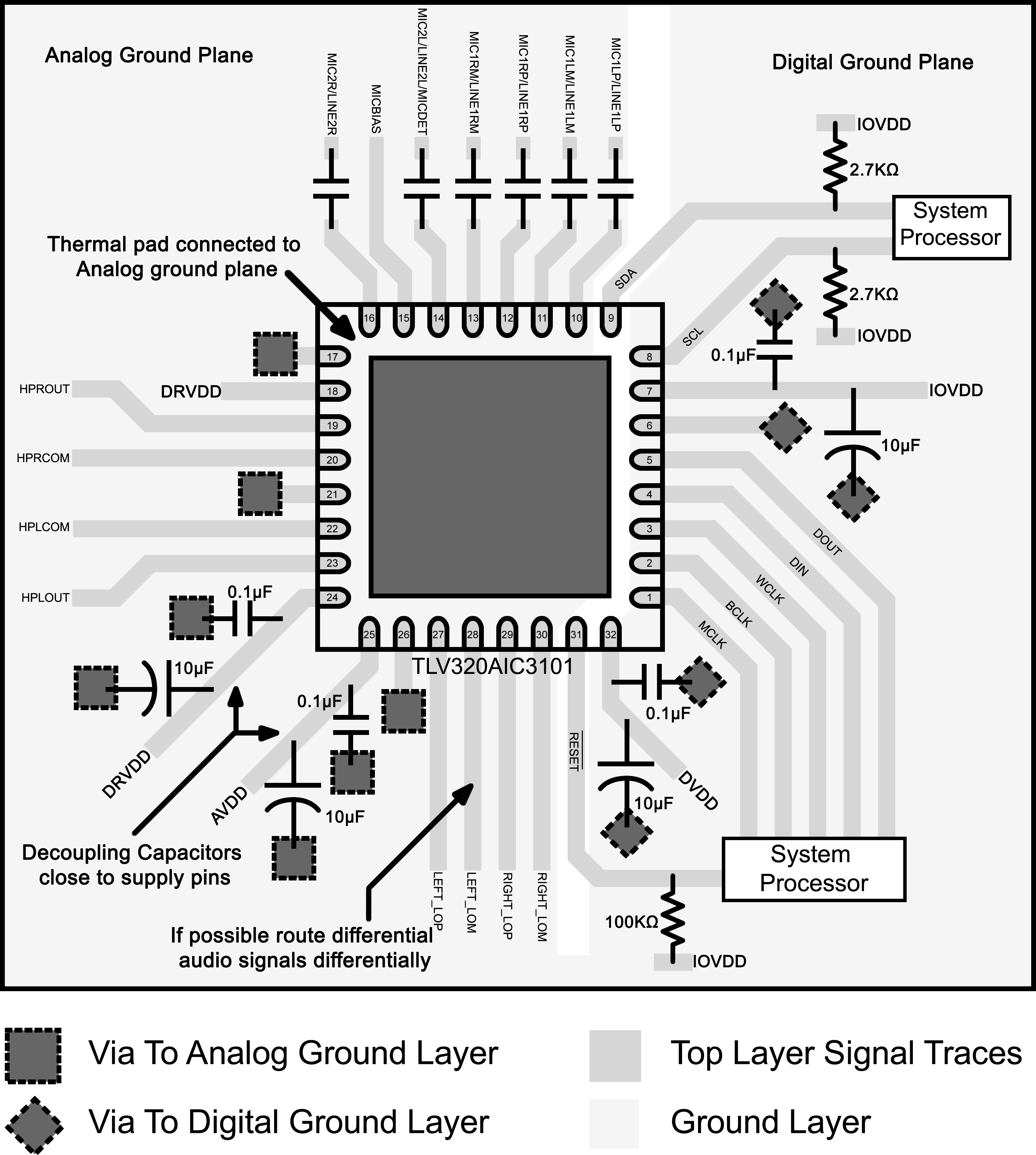

14 Layout

14.1 Layout Guidelines

PCB design is made considering the application, and the review is specific for each system requirements. However, general considerations can optimize the system performance.

- The TLV320AIC3101 thermal pad should be connected to analog output driver ground using multiple VIAS to minimize impedance between the device and ground.

- Analog and digital grounds should be separated to prevent possible digital noise from affecting the analog performance of the board.

- The TLV320AIC3101 requires the decoupling capacitors to be placed as close as possible to the device power supply terminals.

- If possible, route the differential audio signals differentially on the PCB. This is recommended to get better noise immunity.

14.2 Layout Example

Figure 39. Layout Schematic

Figure 39. Layout Schematic