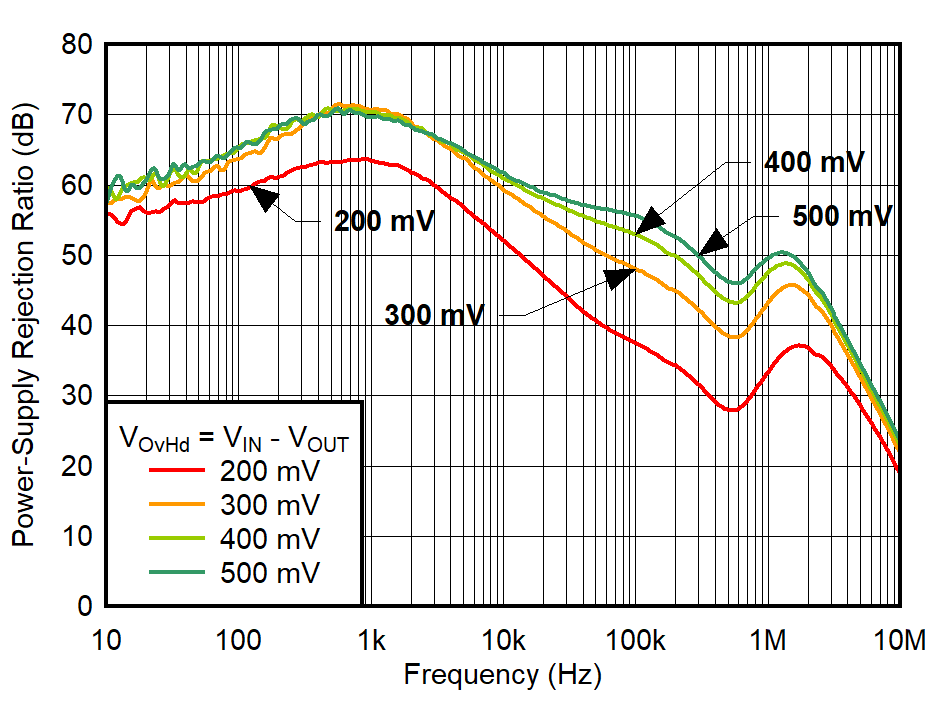

at TJ = 25°C, VIN =

VOUT(nom) + 0.3 V, VBIAS = 5 V, VEN =

VIN, CIN = 10 μF, CBIAS = 1 μF, and

COUT = 10 μF (unless otherwise noted)

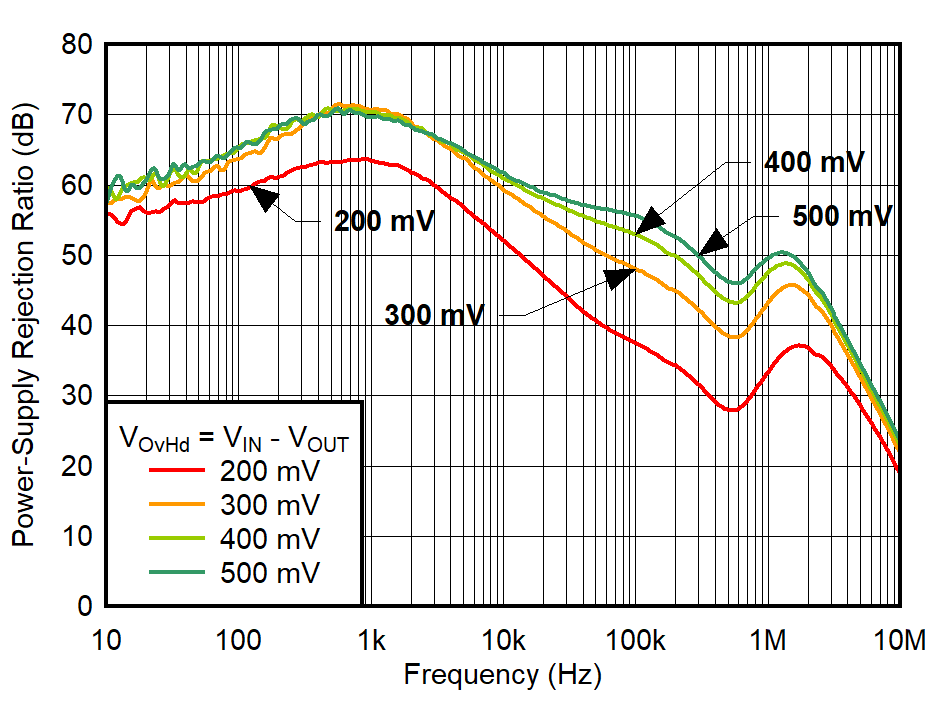

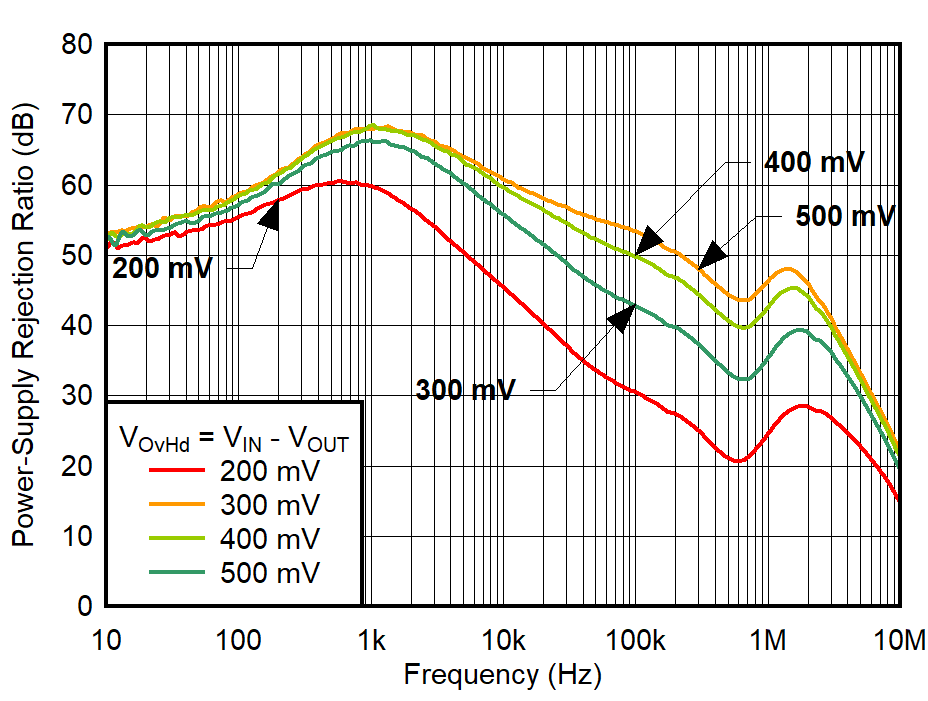

| CIN = 0 μF, COUT = 10 μF,

CBIAS = 1 μF |

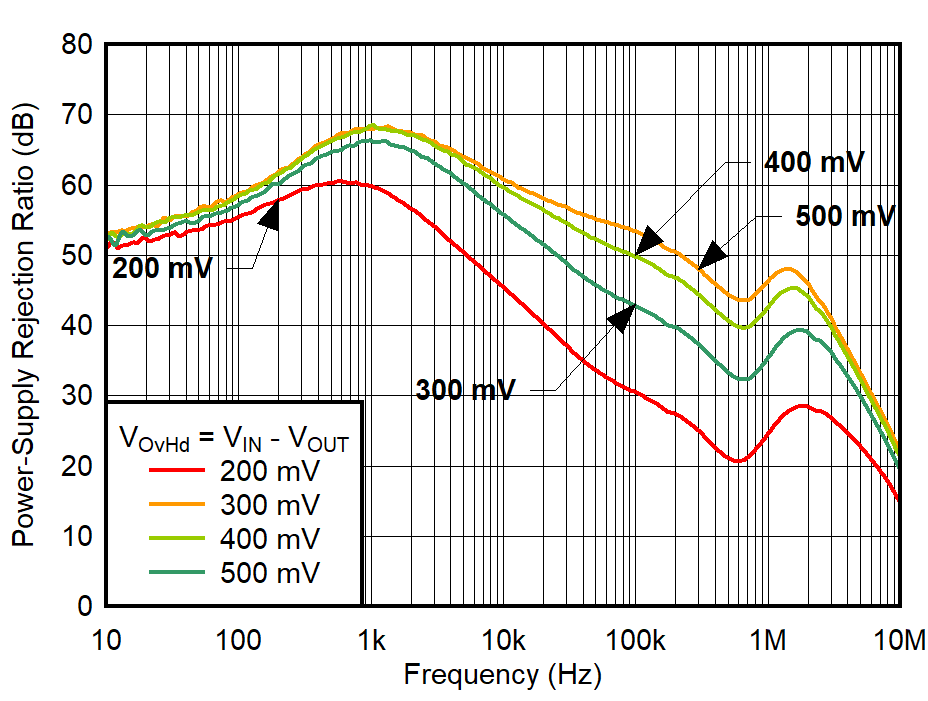

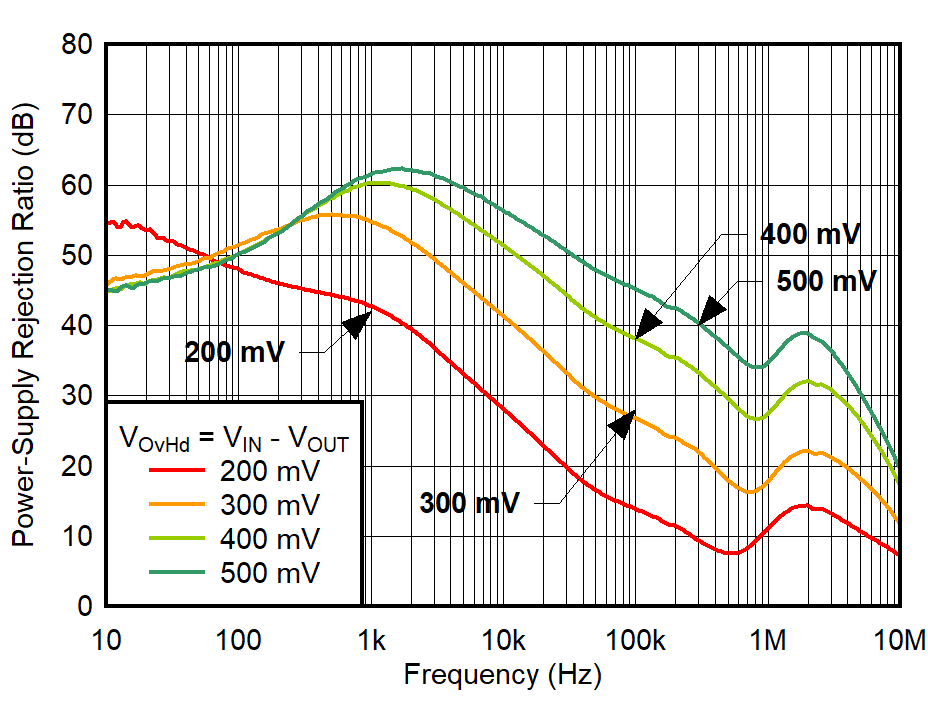

Figure 6-1 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 400 mA,

VOUT = 1.8 V

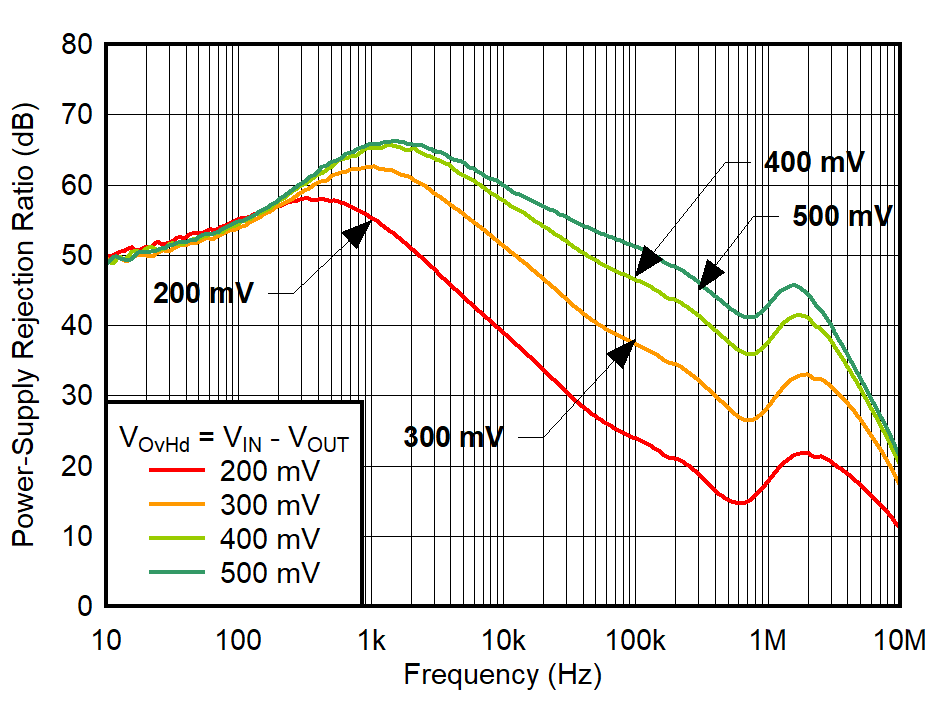

| CIN = 0 μF, COUT = 10 μF,

CBIAS = 1 μF |

Figure 6-3 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 1.1 A,

VOUT = 1.8 V

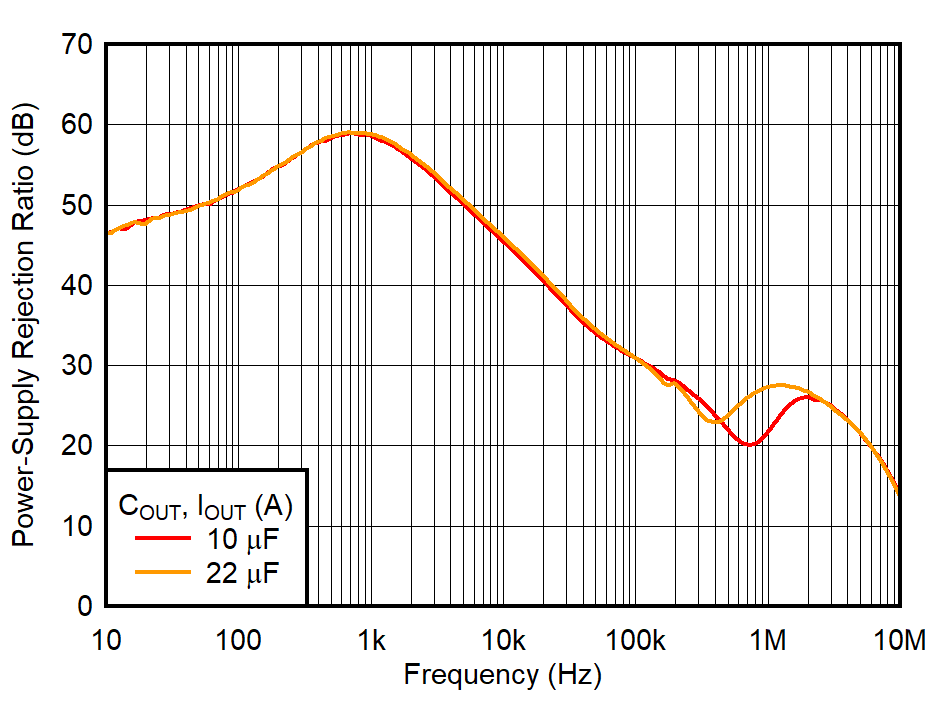

| CIN = 0 μF, COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5

A |

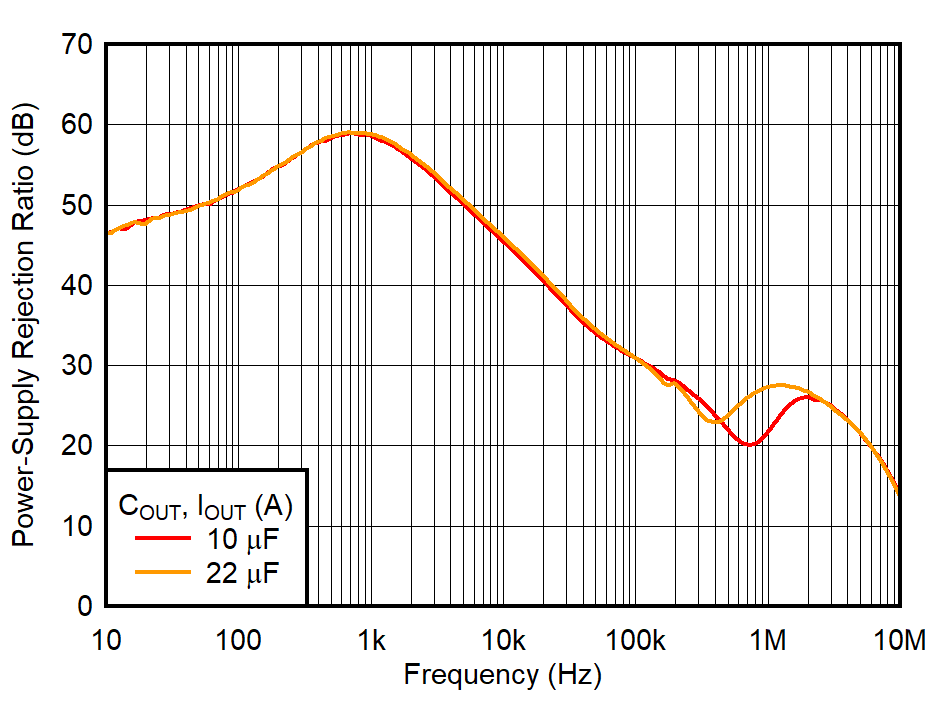

Figure 6-5 PSRR

vs Frequency and COUT for VOUT = 1.8 V

VIN = VOUT + 0.3 V,

CBIAS = 0 μF, CIN =

COUT = 10 μF,

CBIAS = 1

μF |

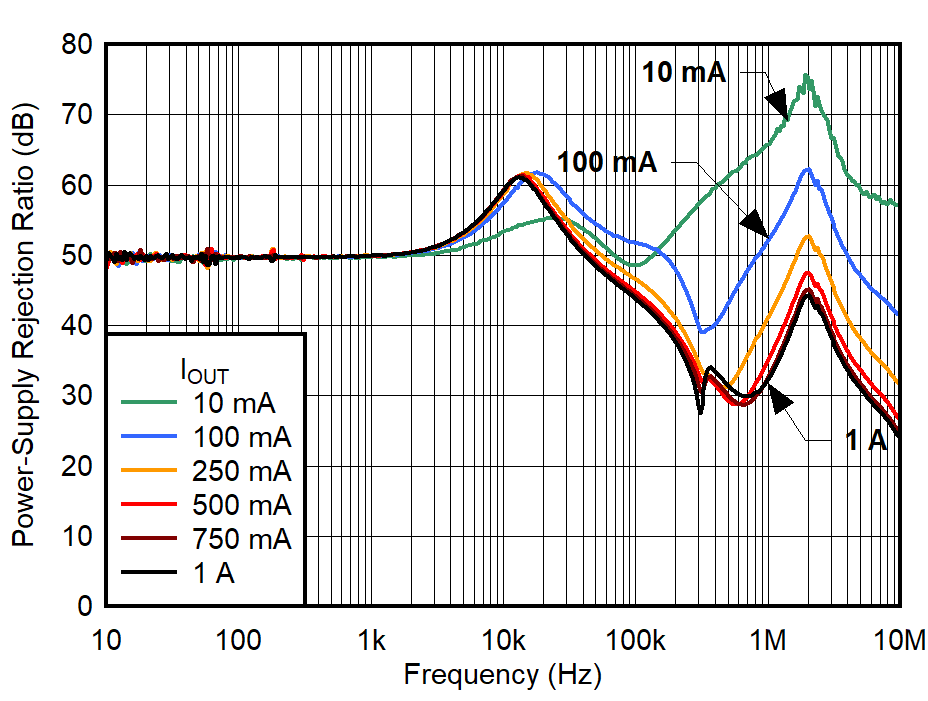

Figure 6-7 Bias

Rail PSRR vs Frequency and IOUT

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

| |

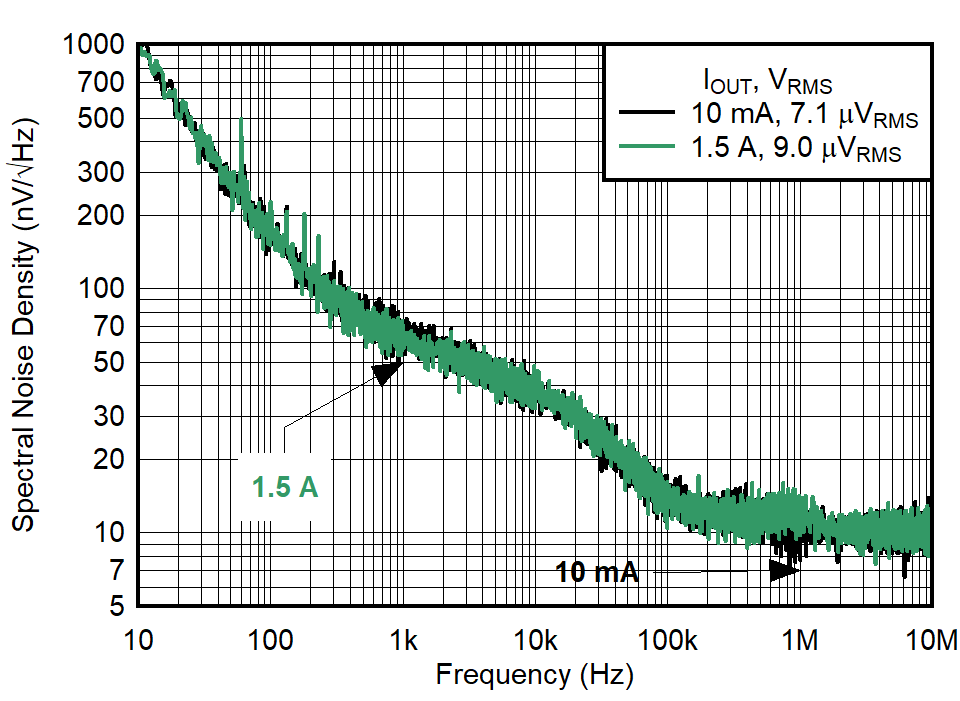

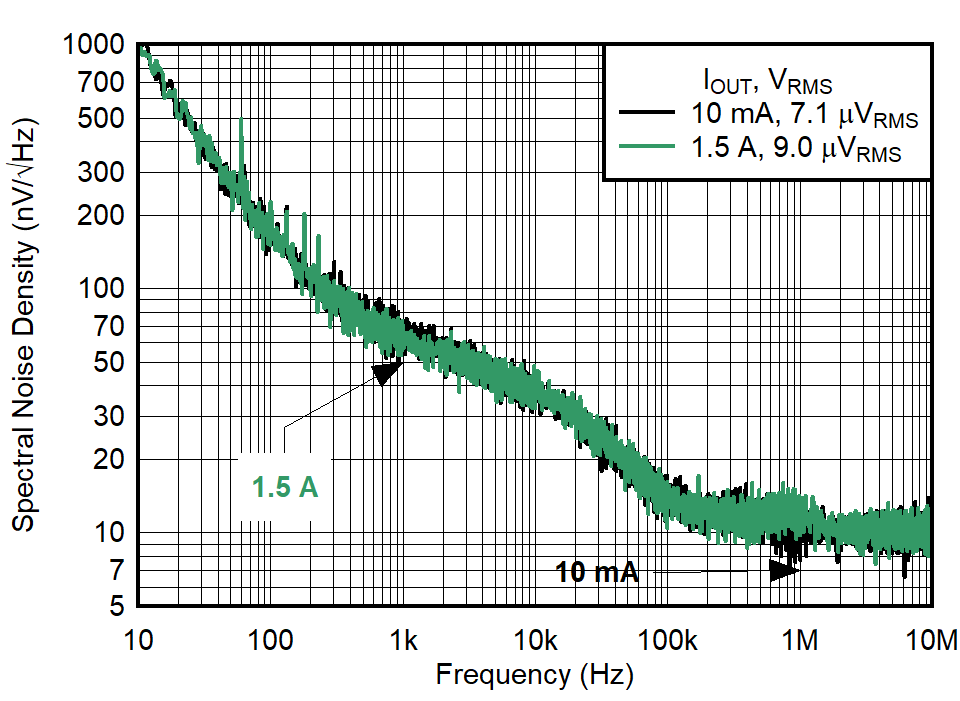

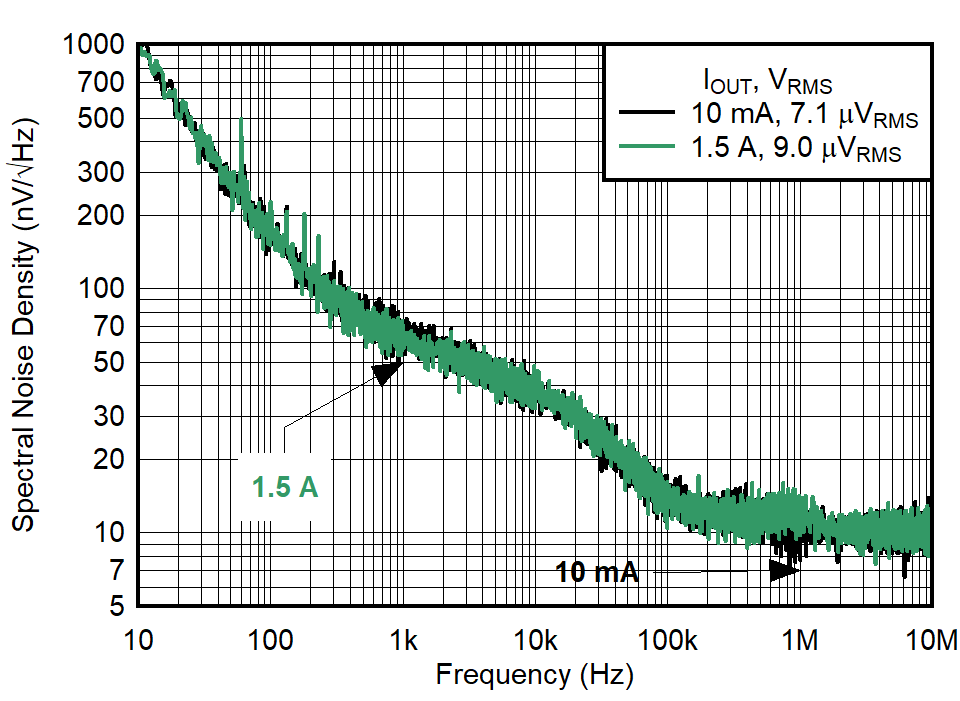

Figure 6-9 Noise

vs Frequency and IOUT for VOUT = 3.3 V

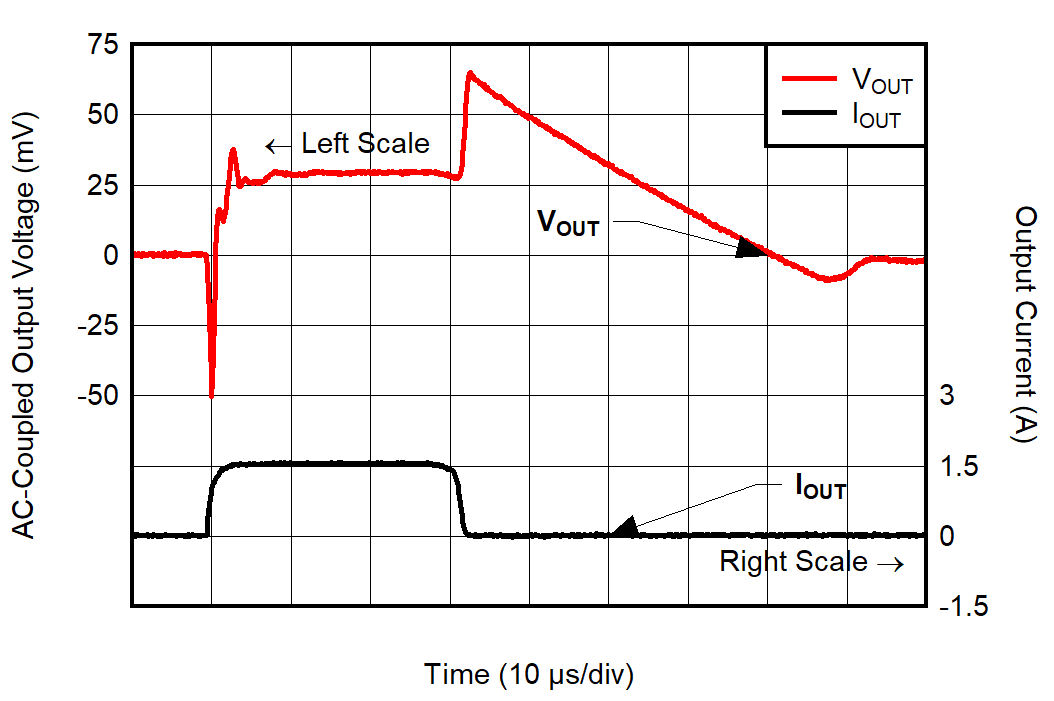

CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 10 mA to

1.5 A to

10 mA at 1

A/μs |

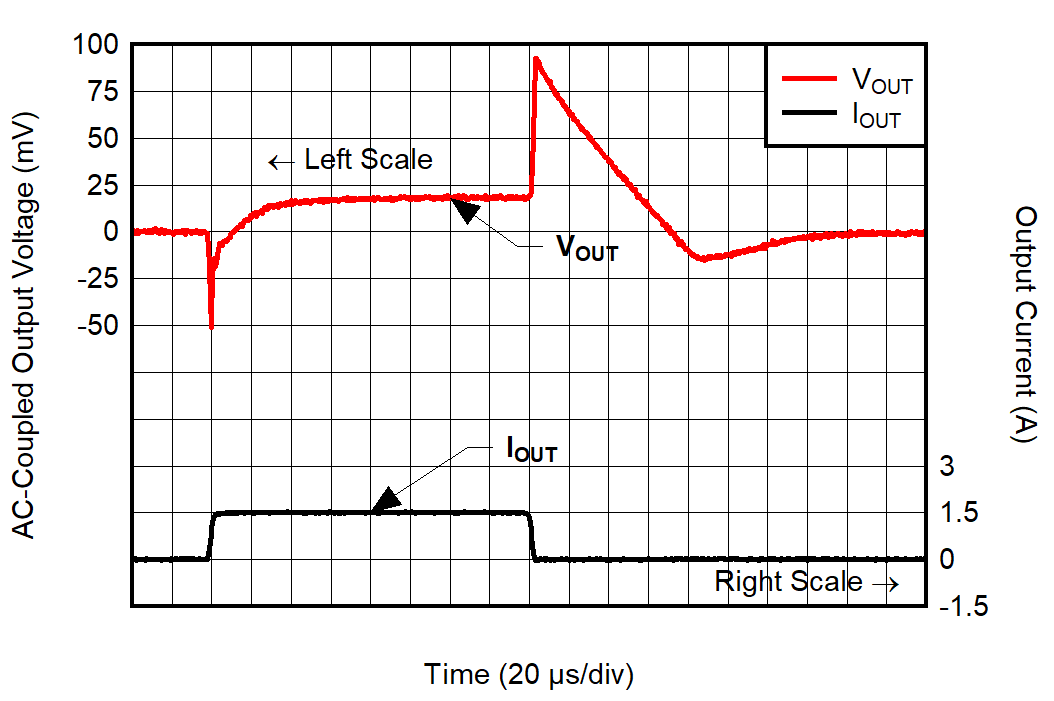

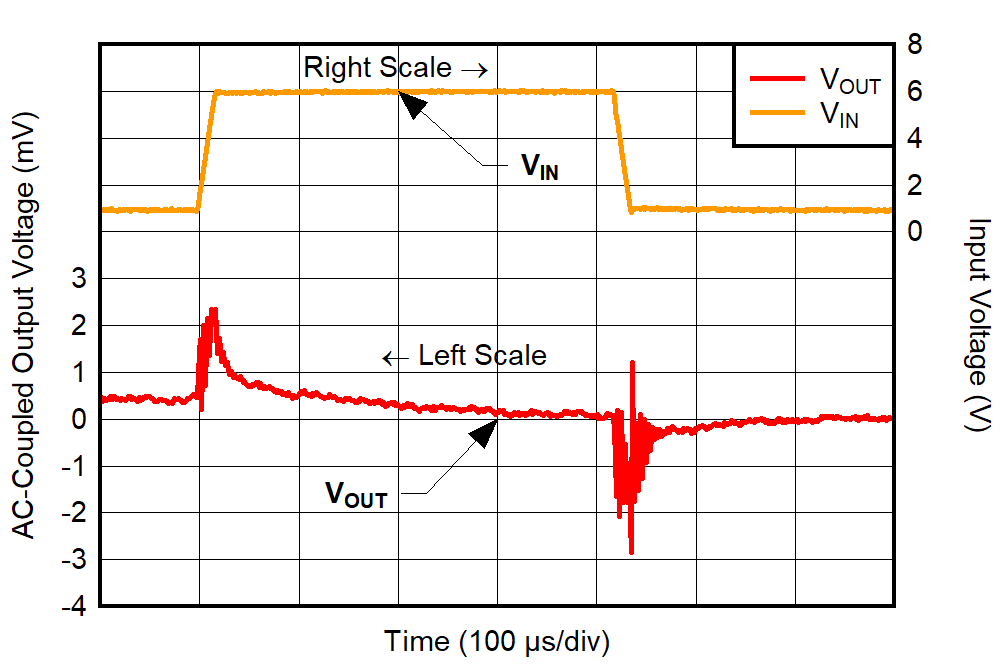

Figure 6-11 Load

Transient for VOUT = 3.3 V

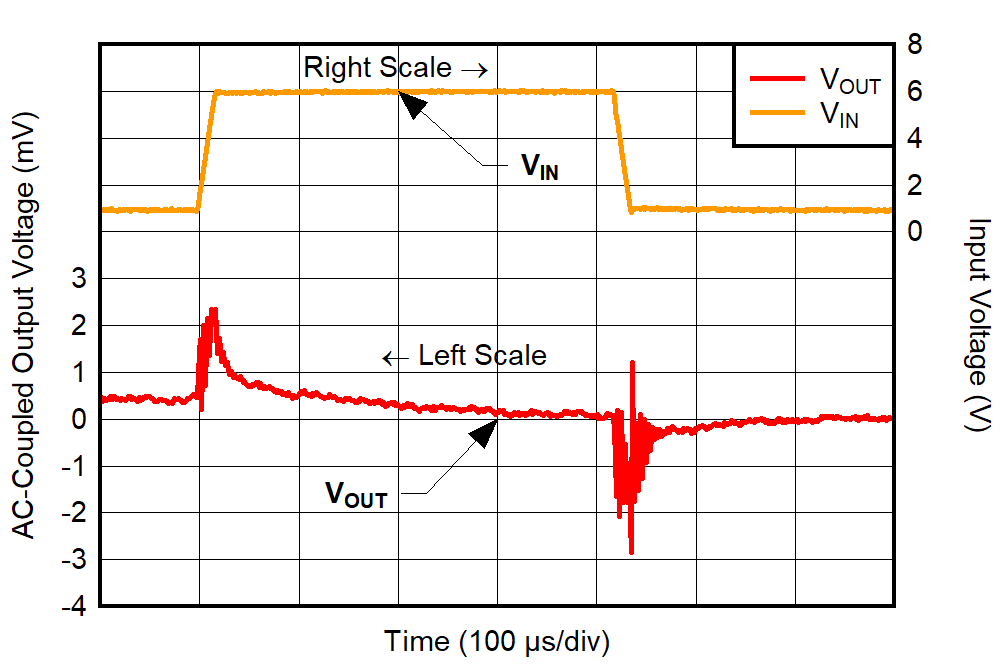

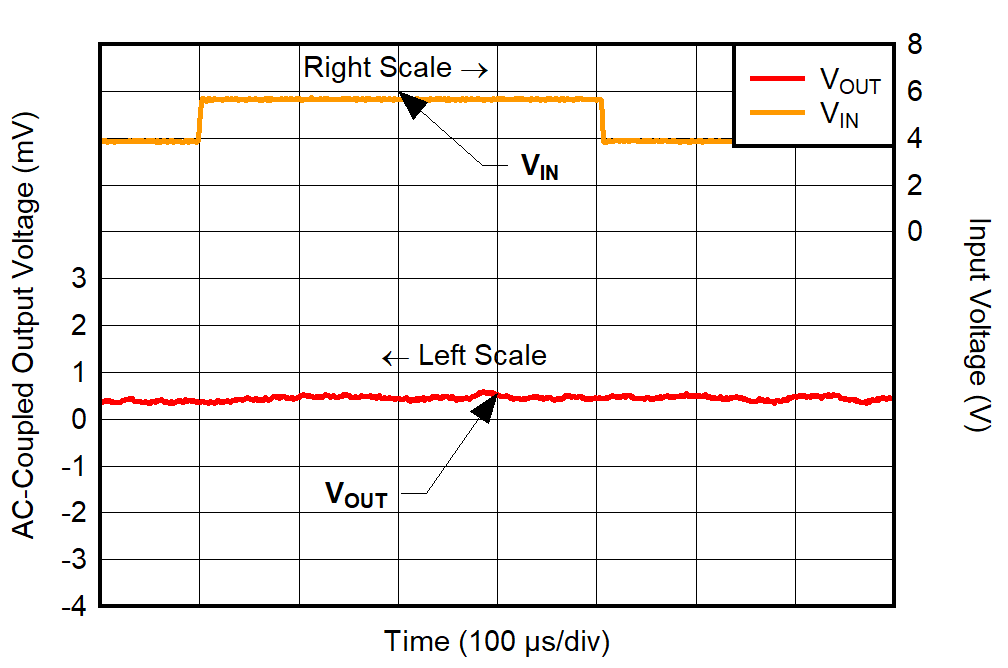

CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

VIN = 3.9 V

to 5.8 V to 3.9 V at 1 V/μs |

Figure 6-13 Line

Transient for VOUT = 3.3 V

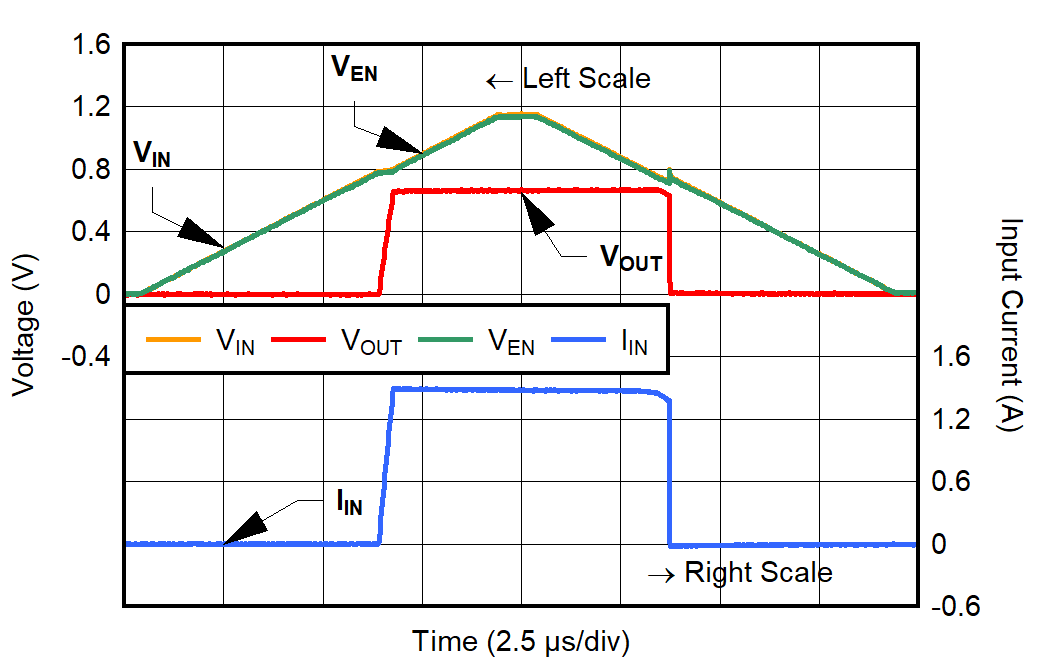

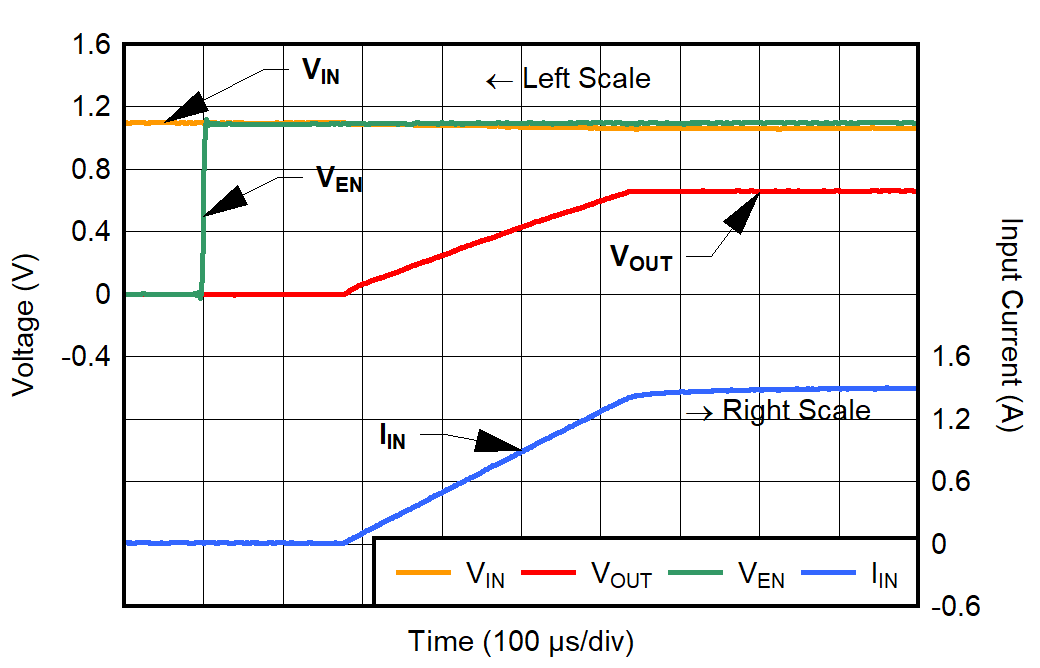

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

VIN = 1.1 V, VBIAS = 5

V |

Figure 6-15 Input

Ramp With Fast Soft-Start

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V, VEN = 1.1

V |

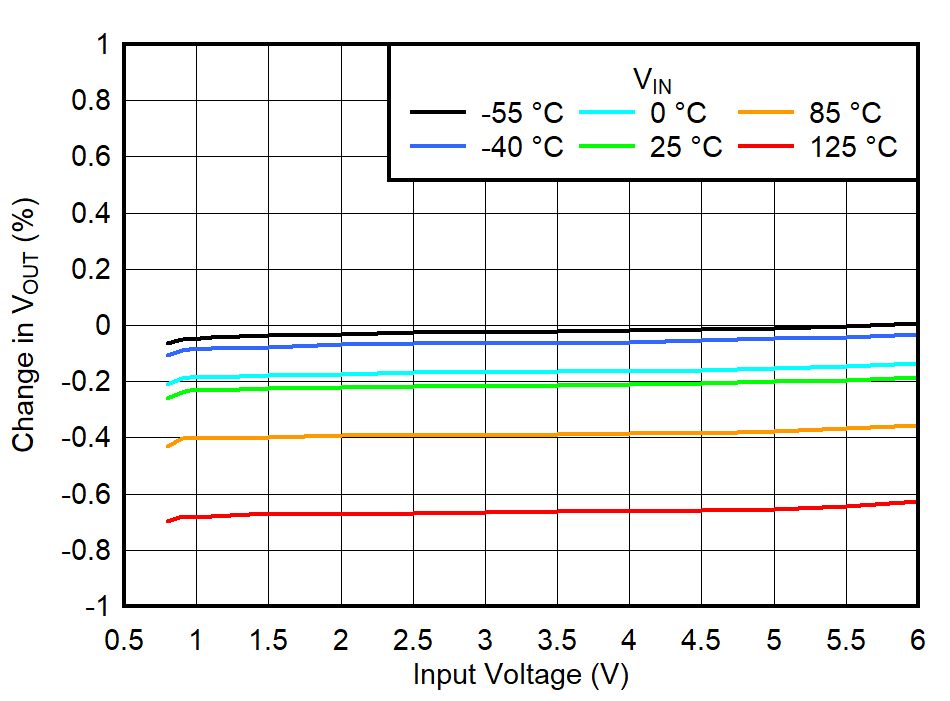

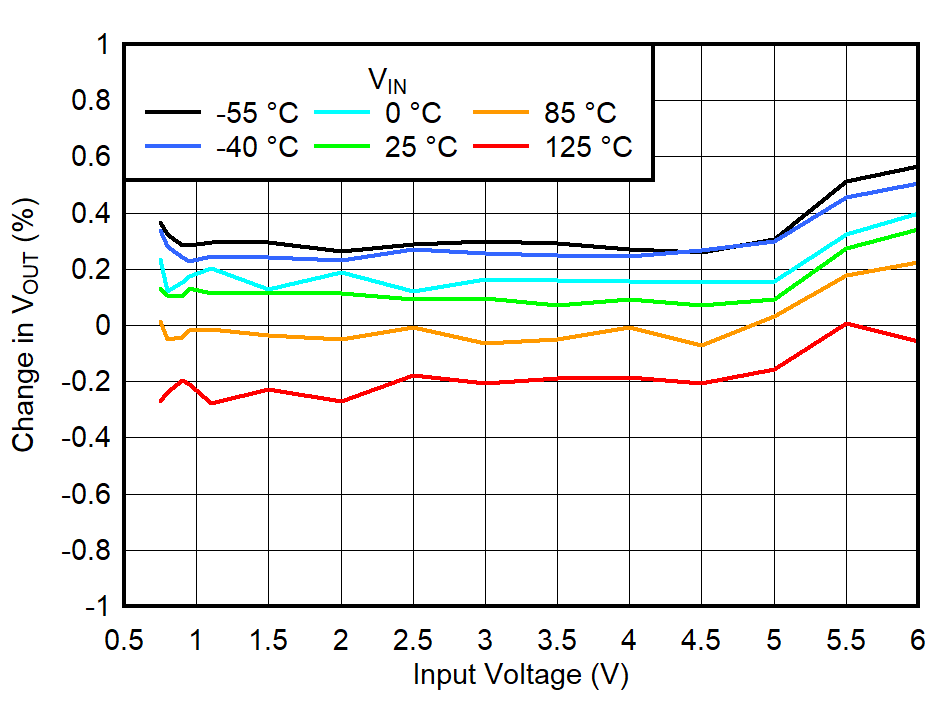

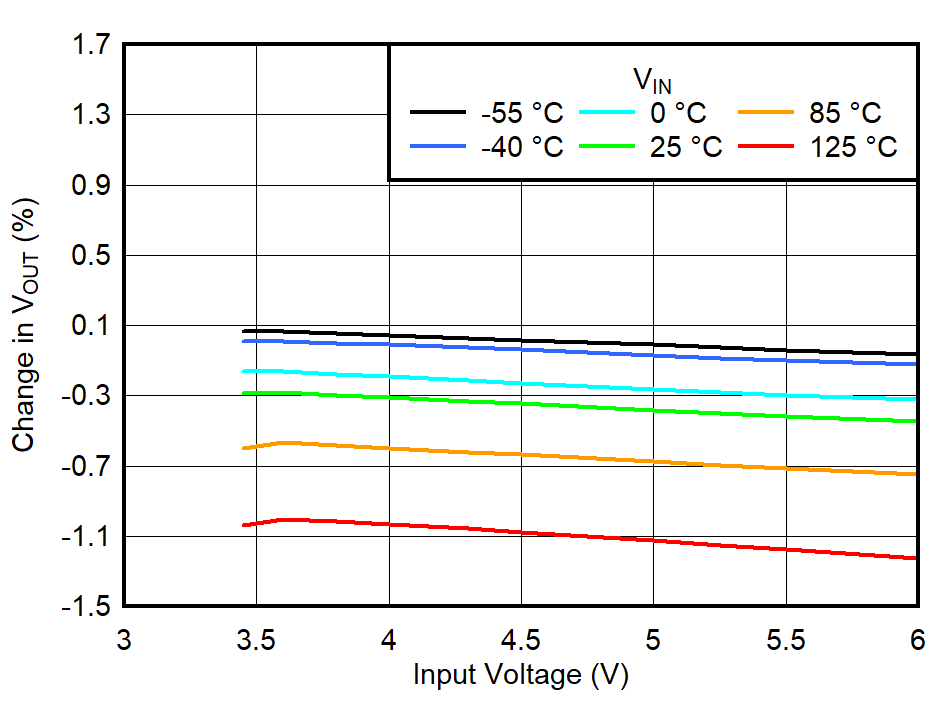

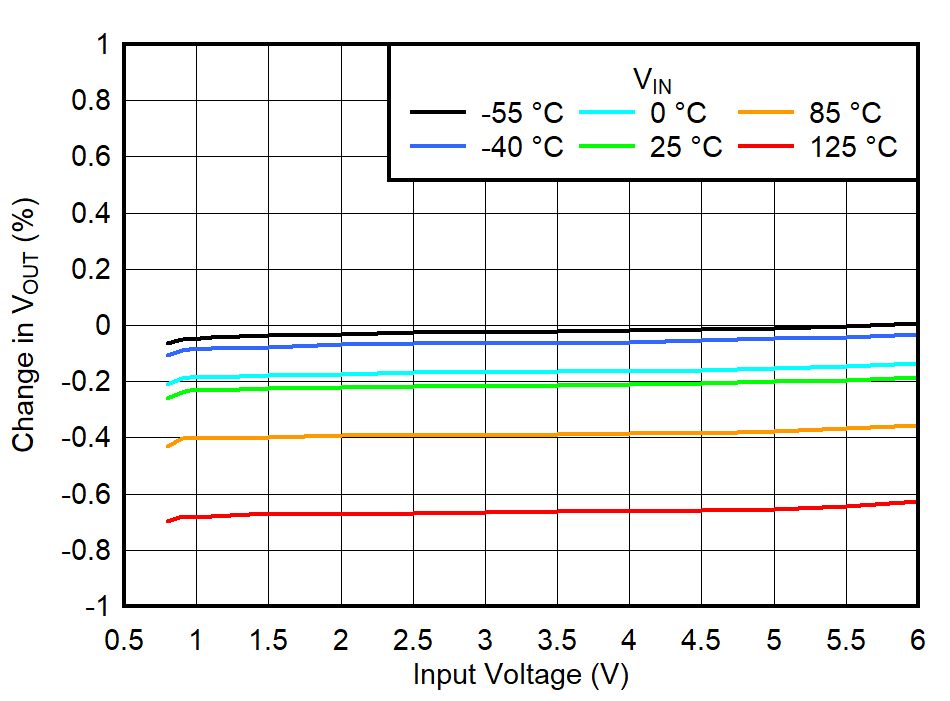

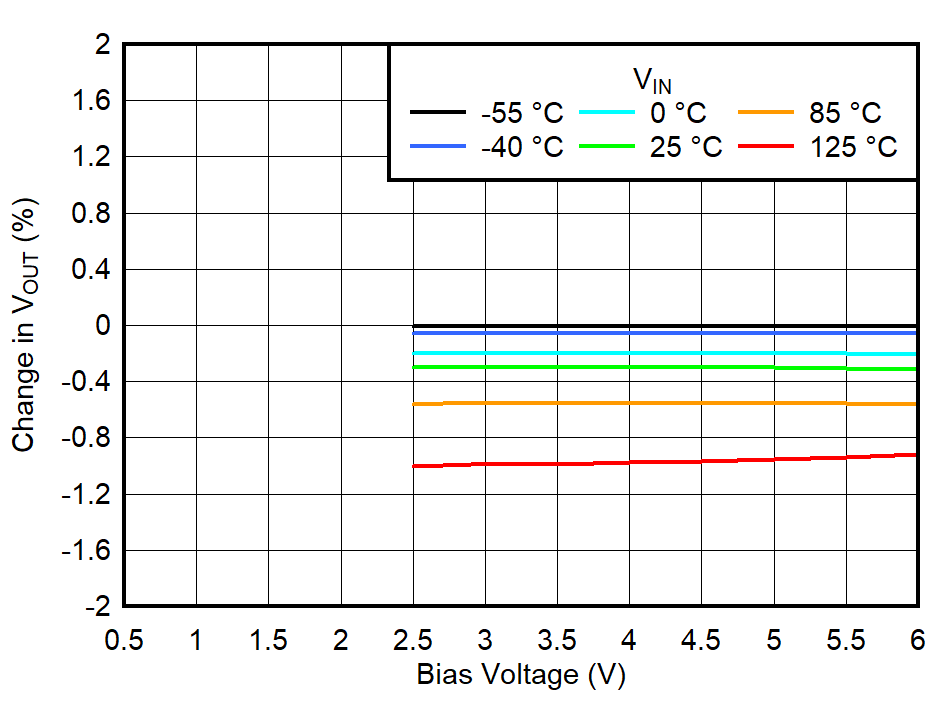

Figure 6-17 IN

Line Regulation for VOUT = 0.65 V, IOUT = 10

mA

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, VEN = 1.1

V |

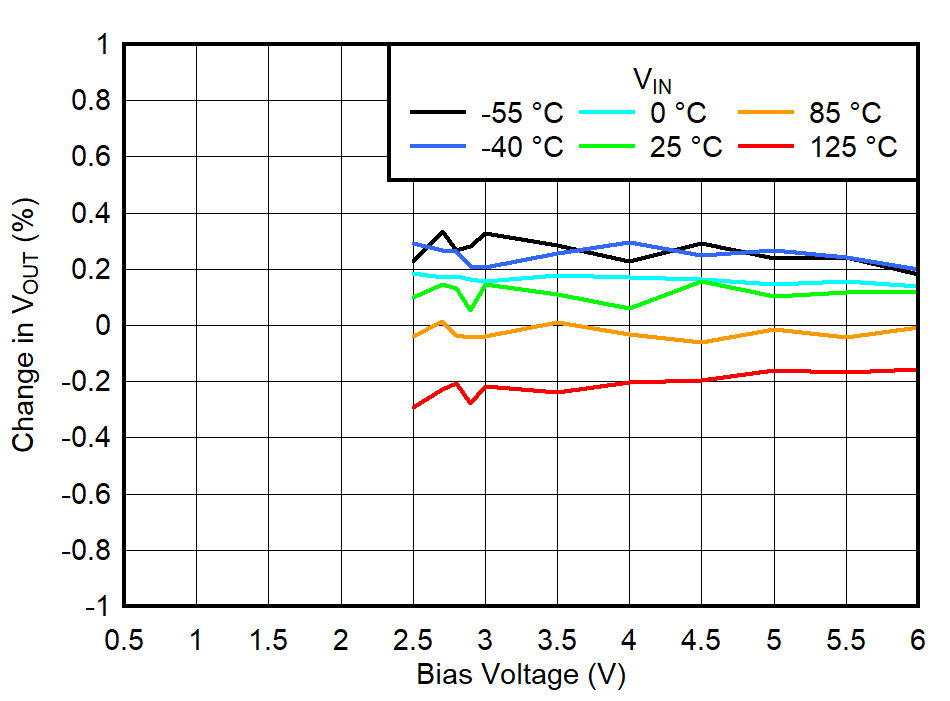

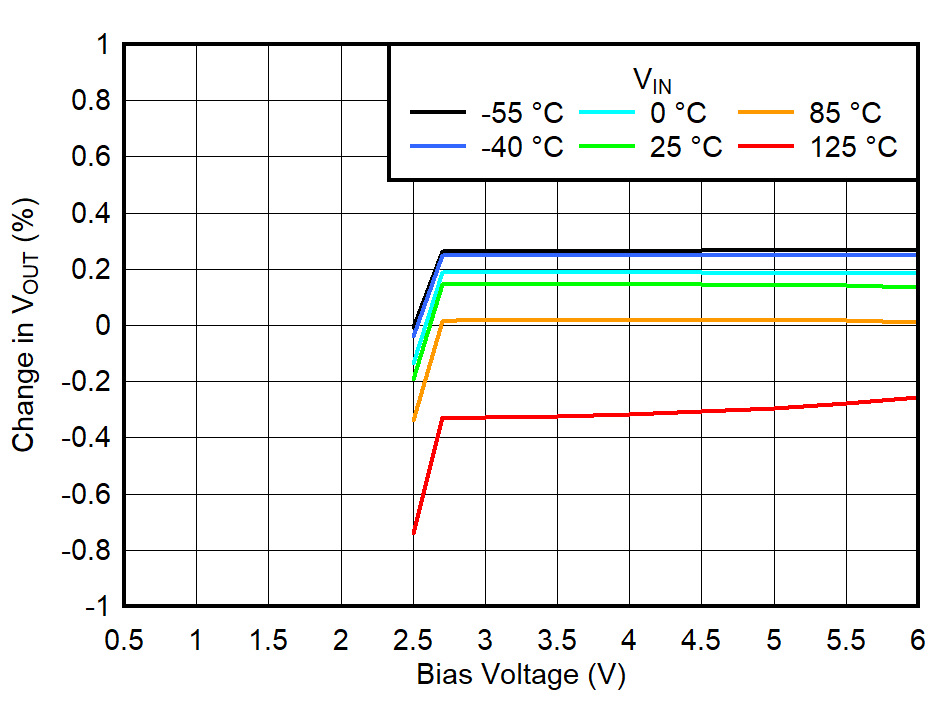

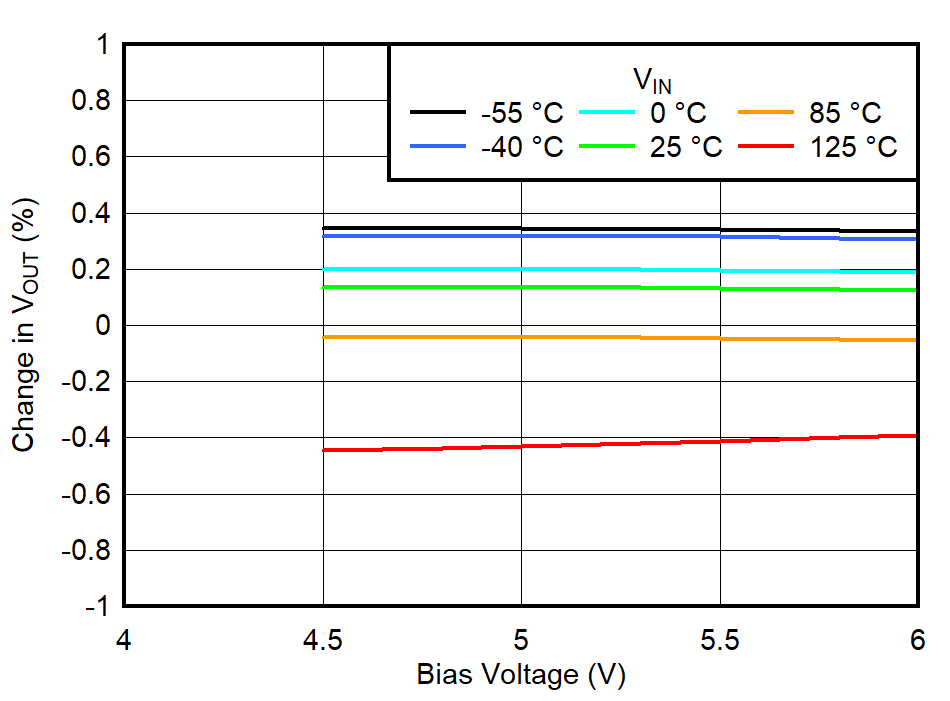

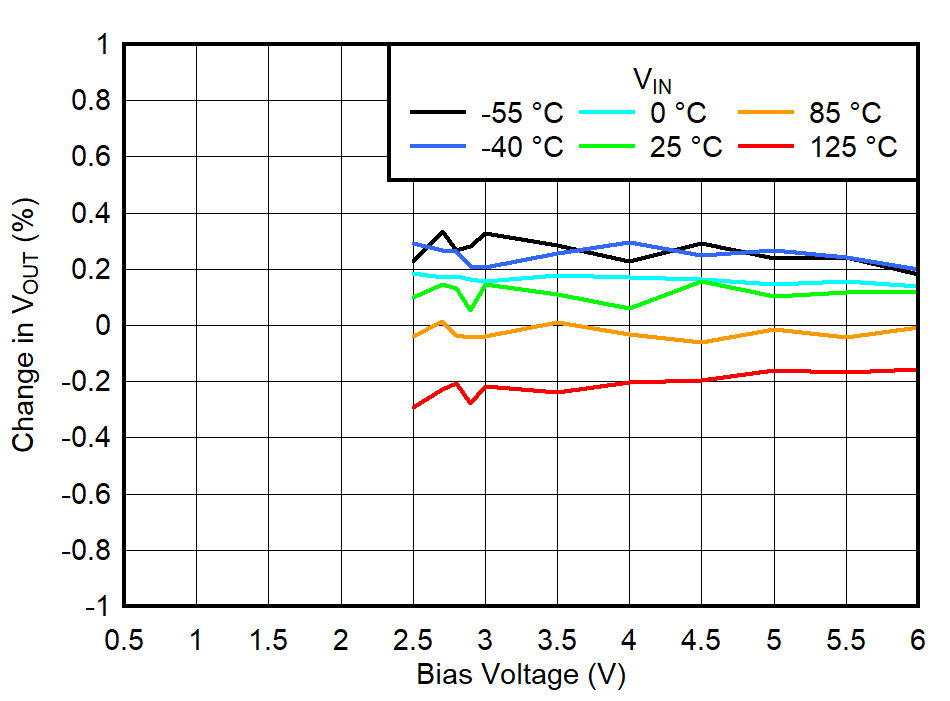

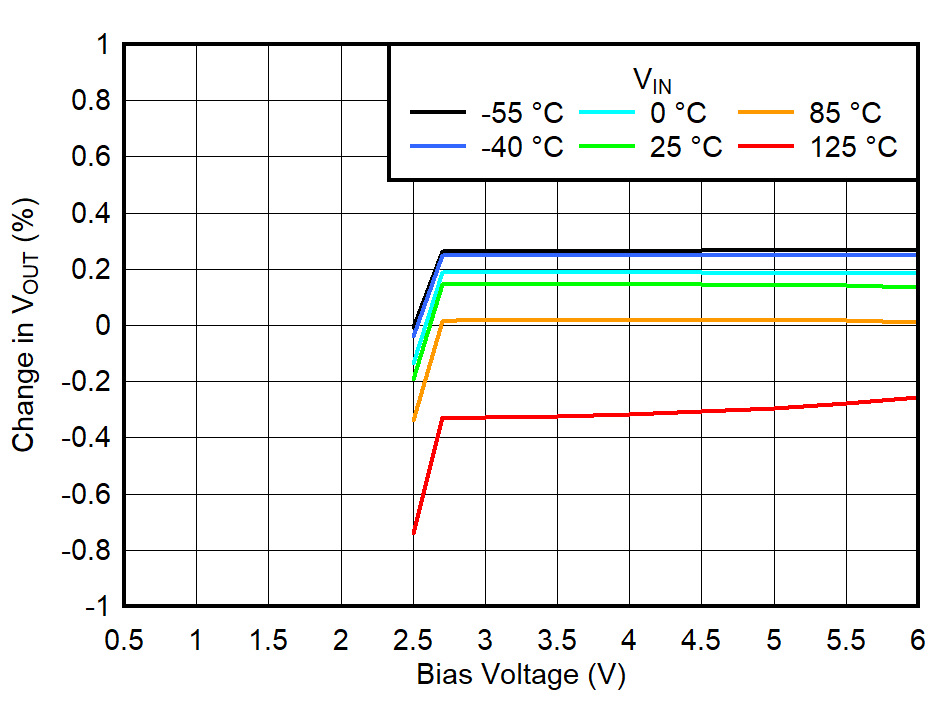

Figure 6-19 BIAS

Line Regulation for VOUT = 0.65 V, IOUT = 0 A

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, VEN = 1.1

V |

Figure 6-21 BIAS

Line Regulation for VOUT = 0.65 V, IOUT = 1.5

A

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V, VEN = 1.1

V |

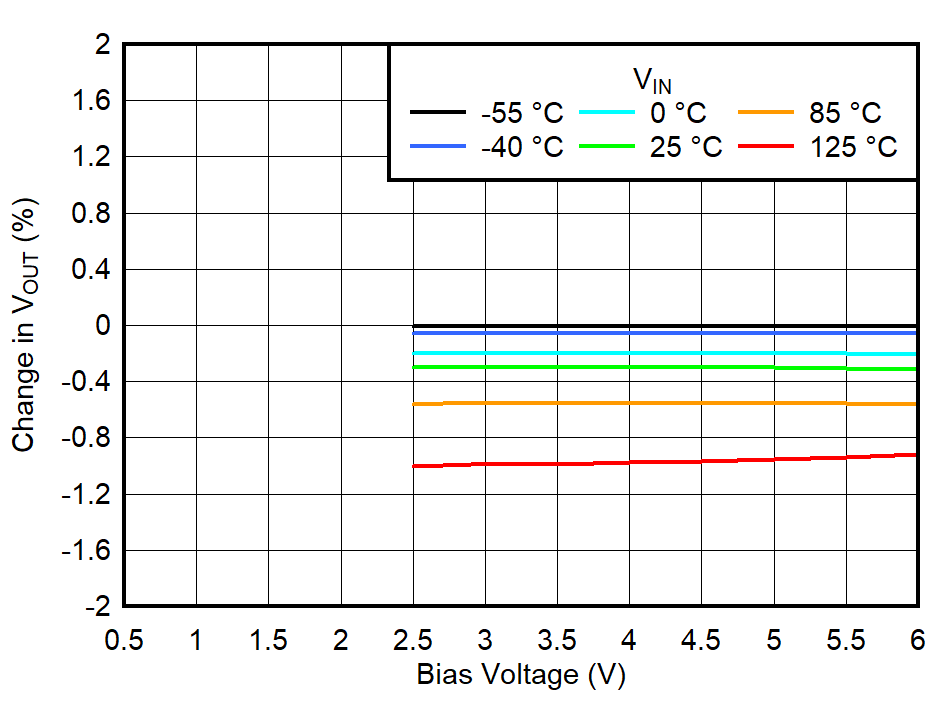

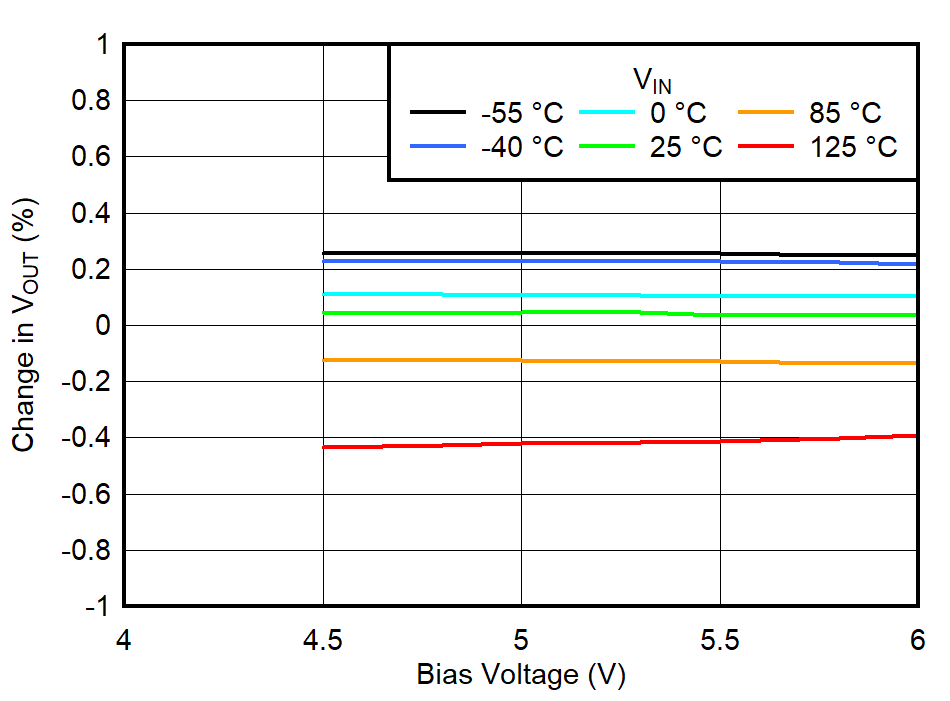

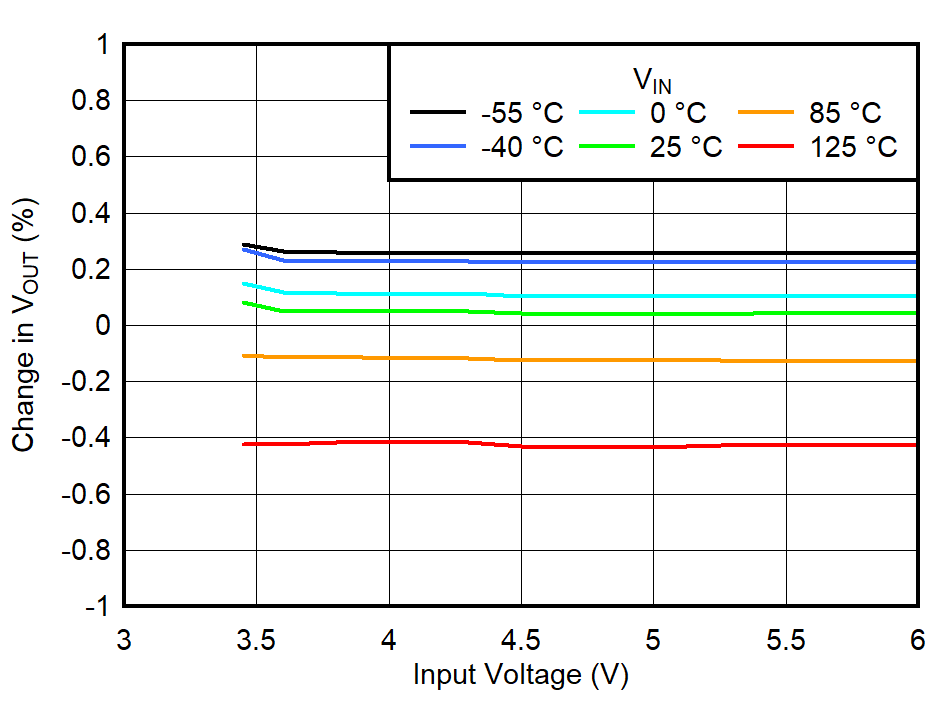

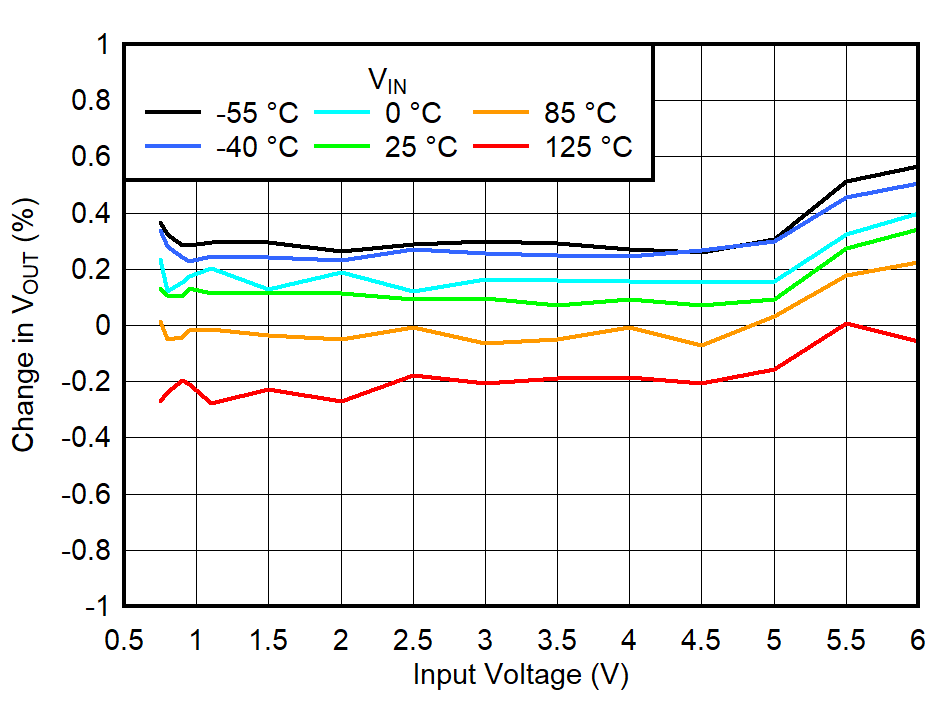

Figure 6-23 IN

Line Regulation for VOUT = 3.3 V, IOUT = 10 mA

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

3.6 V ≤ VIN ≤ 6

V, VEN = 1.1 V |

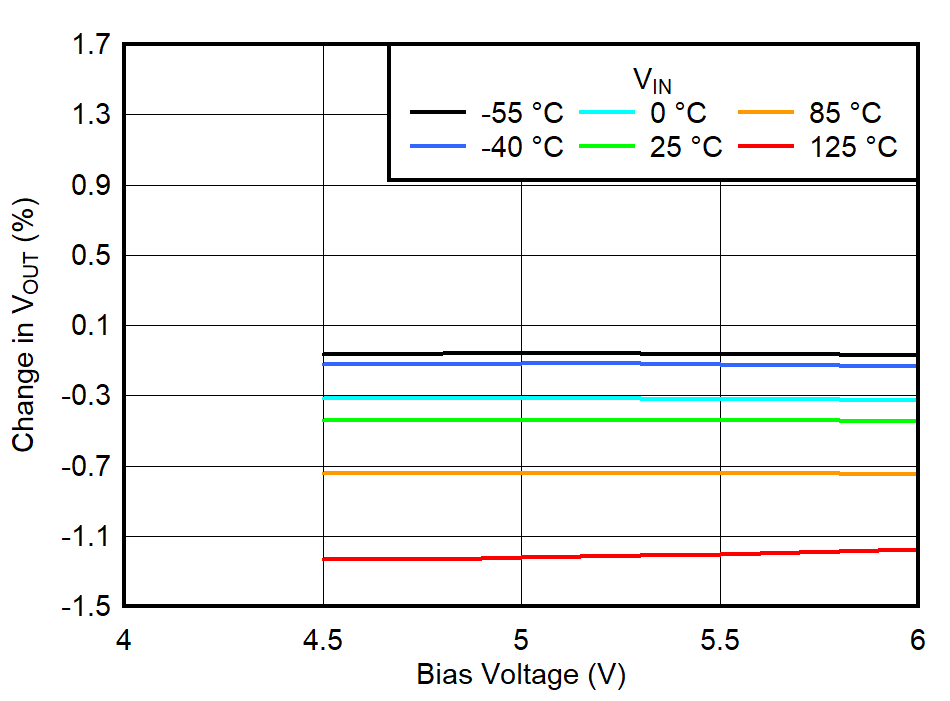

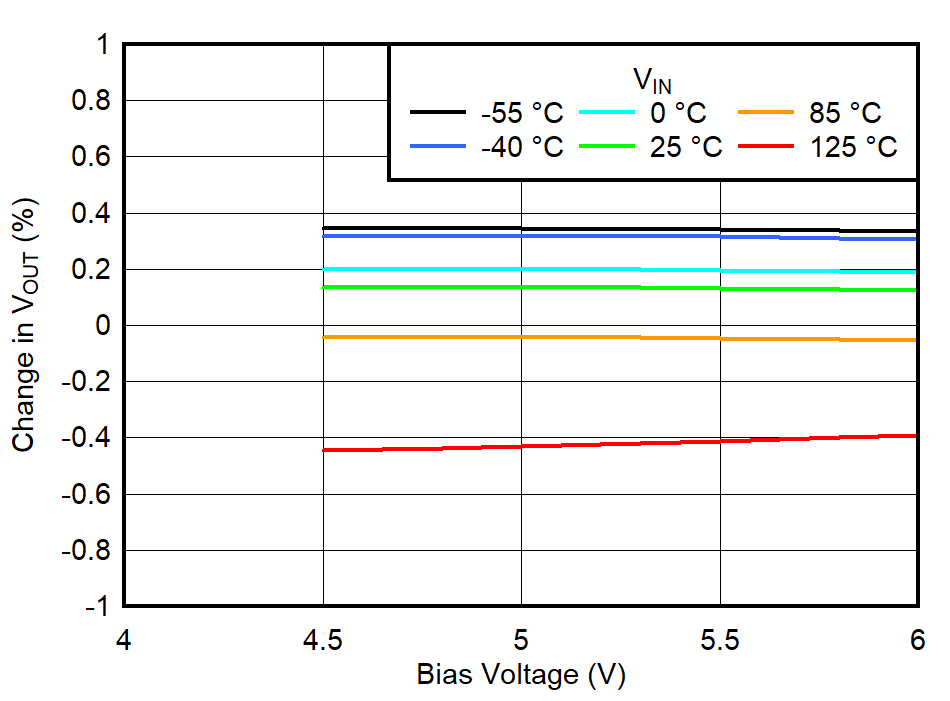

Figure 6-25 BIAS

Line Regulation for VOUT = 3.3 V, IOUT = 0 A

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

3.6 V ≤ VIN ≤ 6

V, VEN = 1.1 V |

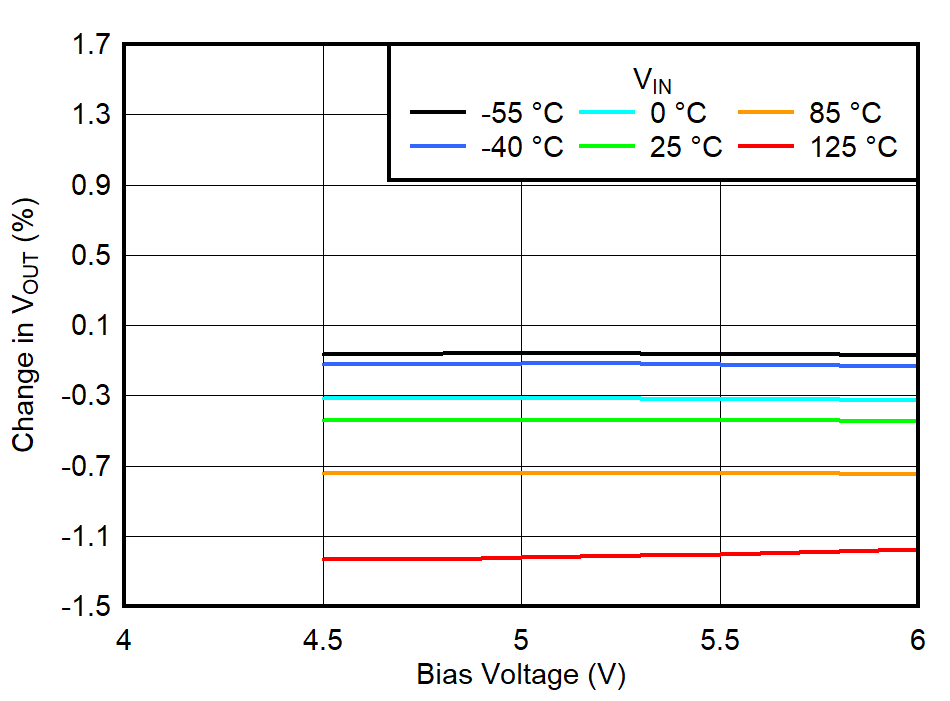

Figure 6-27 BIAS

Line Regulation for VOUT = 3.3 V, IOUT = 1.5 A

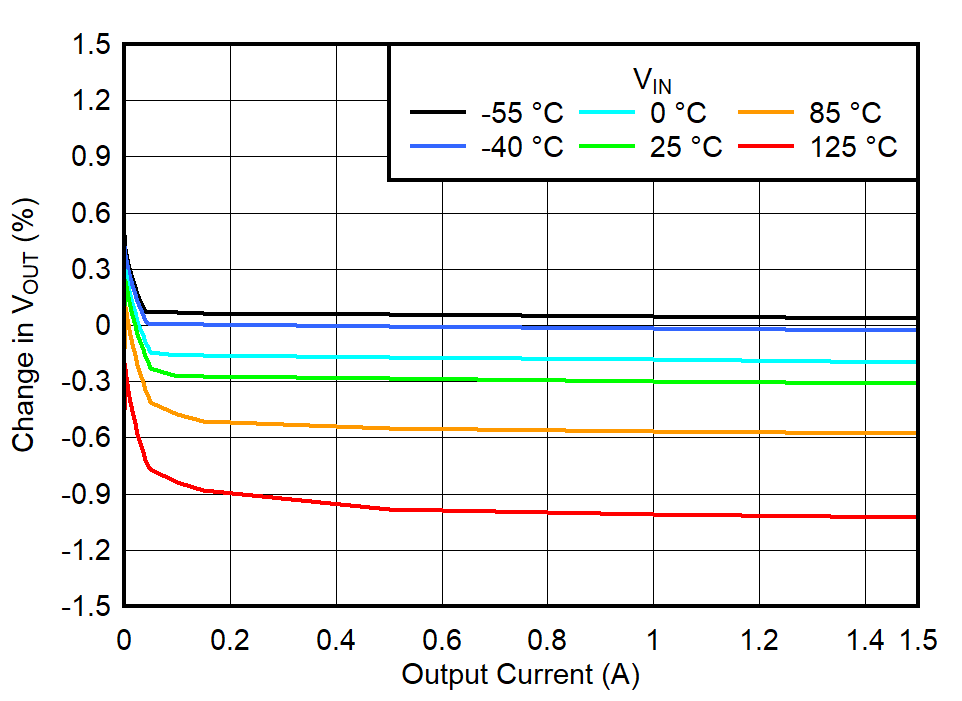

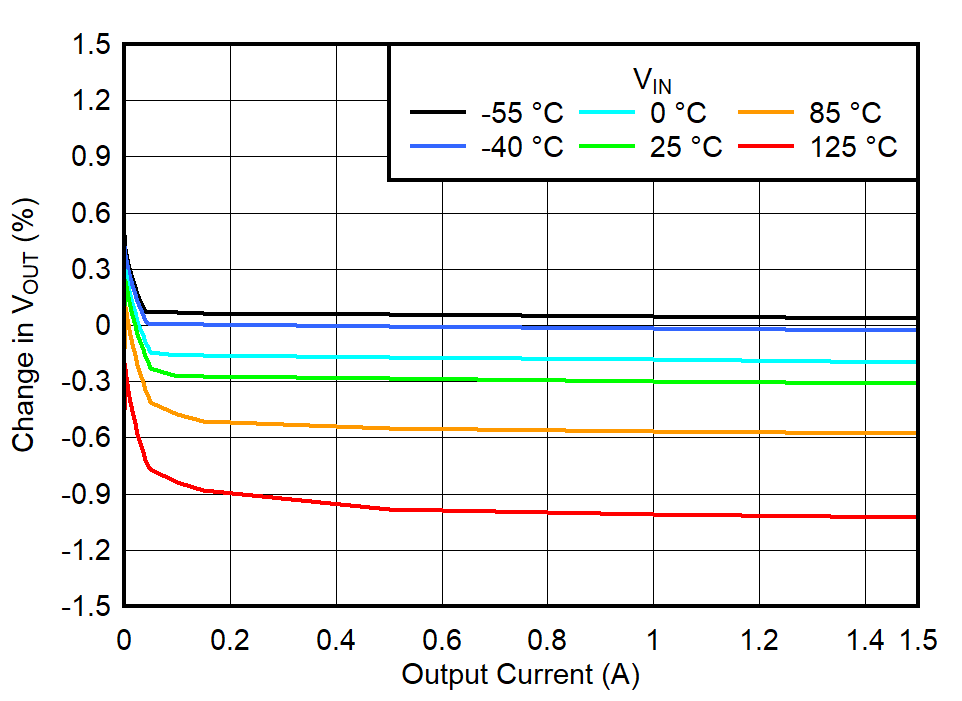

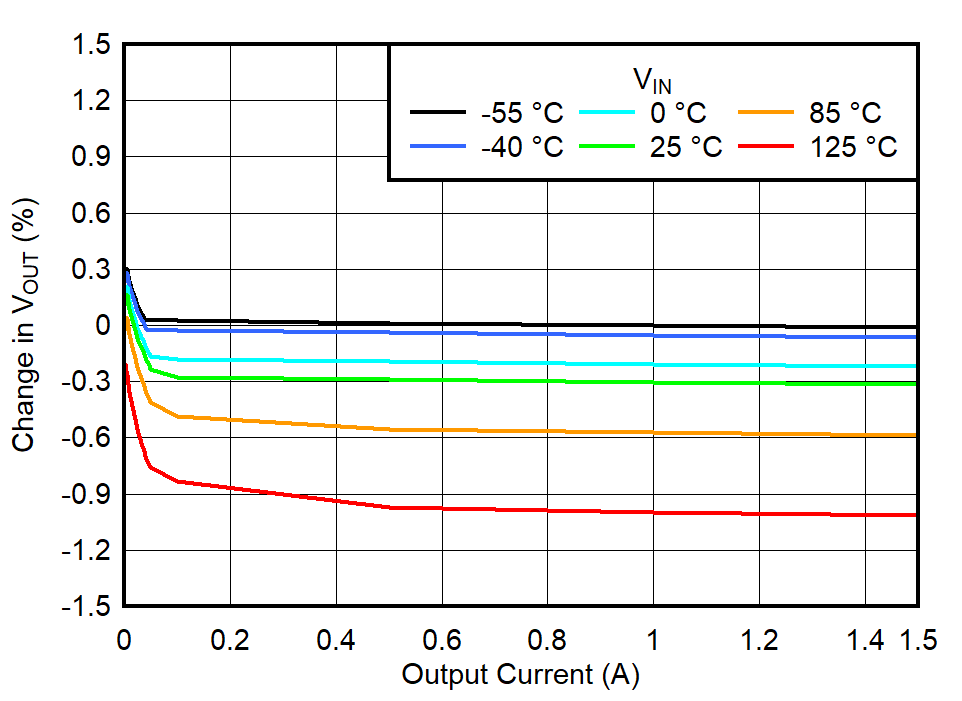

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, VBIAS = 5 V,

VEN = 1.1 V |

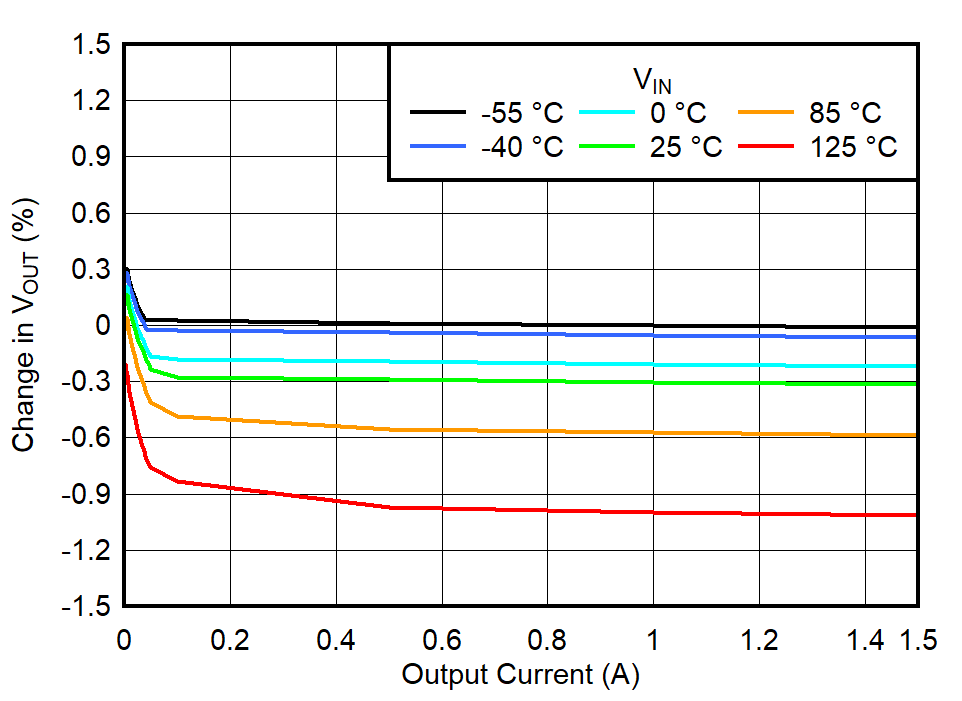

Figure 6-29 Load

Regulation for IOUT = 0 A to Load, VOUT = 3.3

V

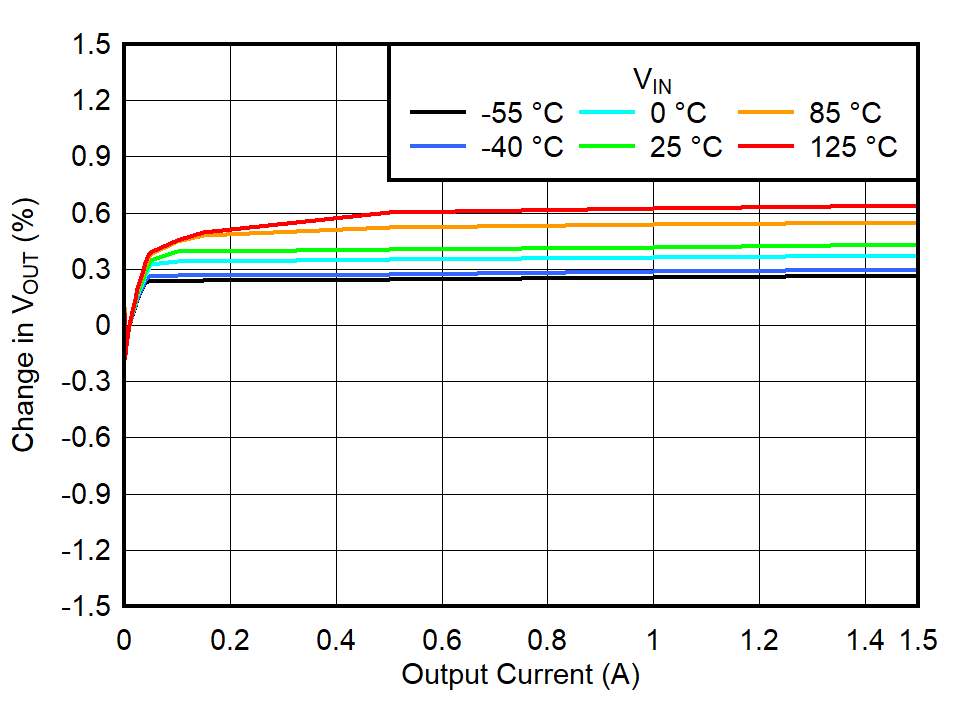

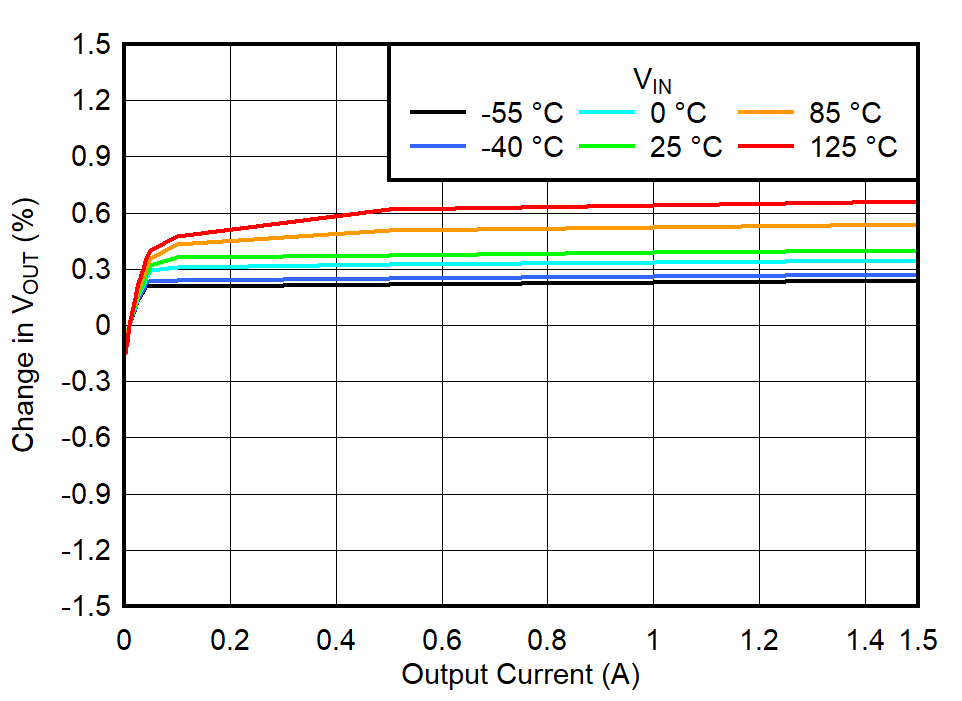

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, VBIAS = 5 V,

VEN = 1.1 V |

Figure 6-31 Load

Regulation for IOUT = 10 mA to Load,

VOUT = 3.3 V

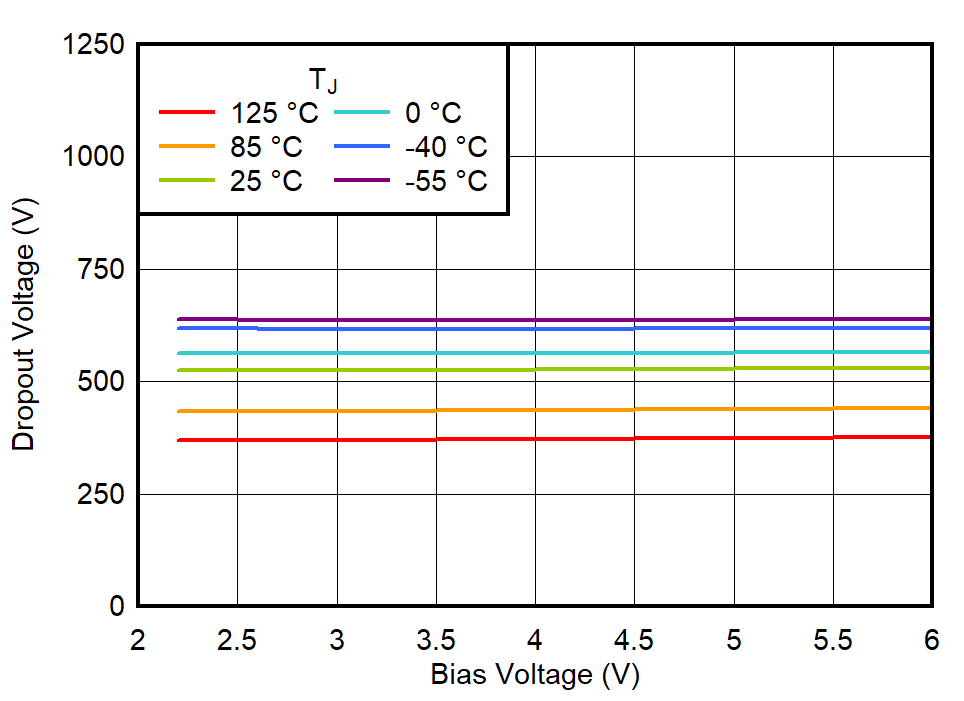

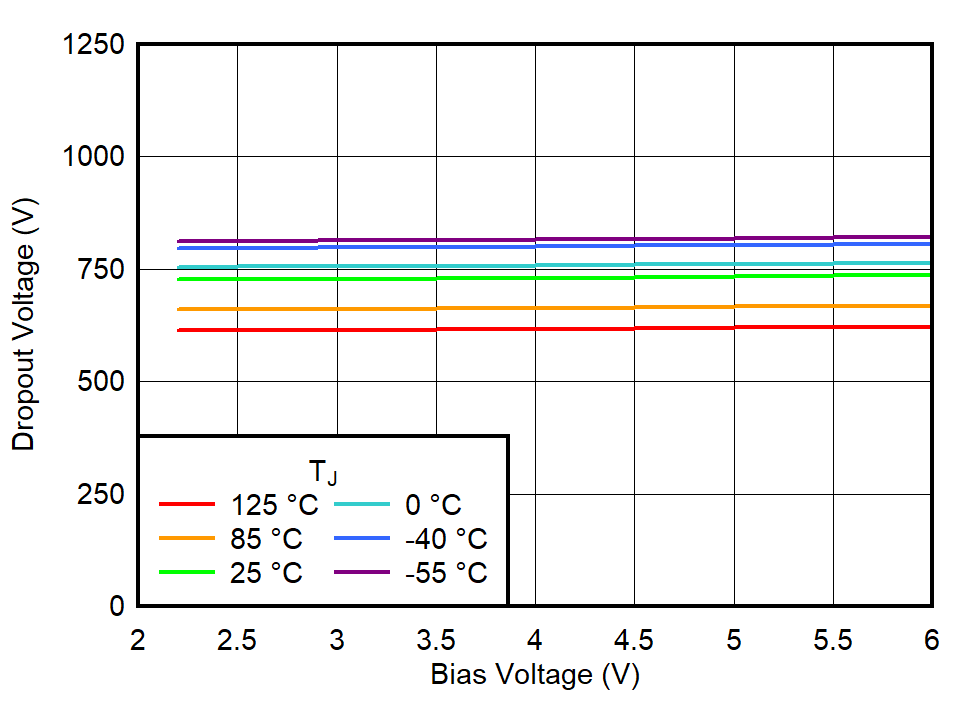

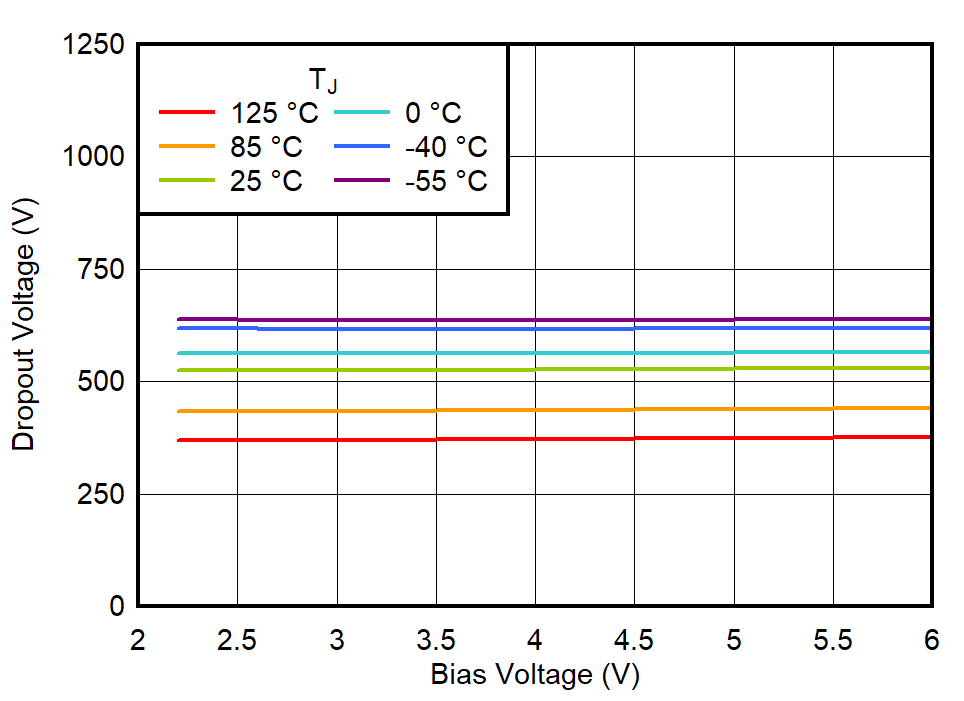

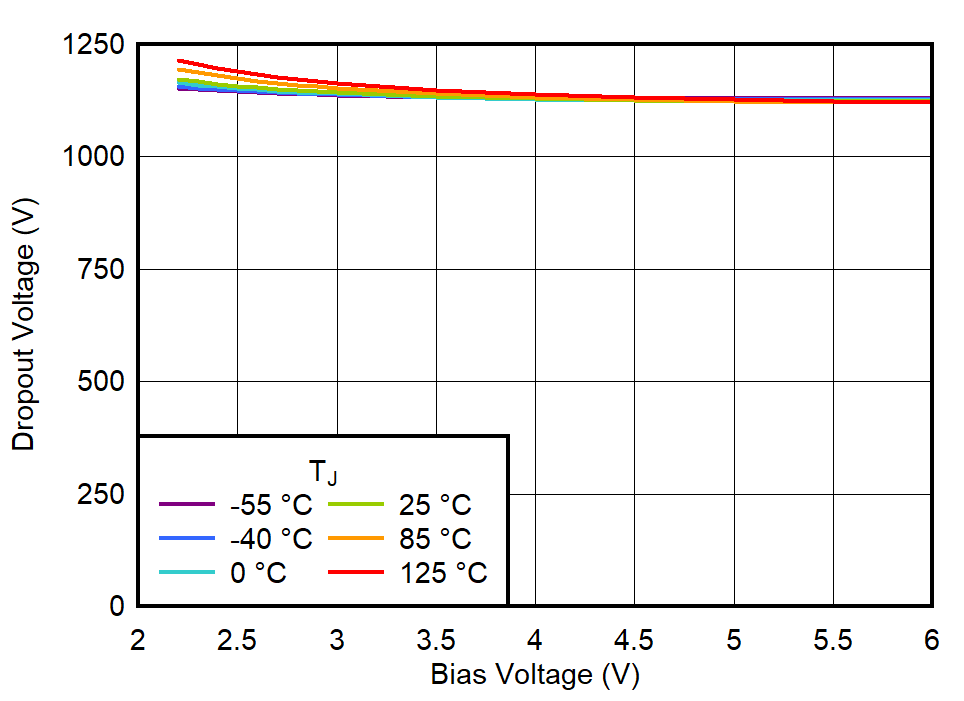

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = VIN, VEN =

1.1 V |

Figure 6-33 Dropout Voltage vs Bias Voltage for IOUT = 0 A

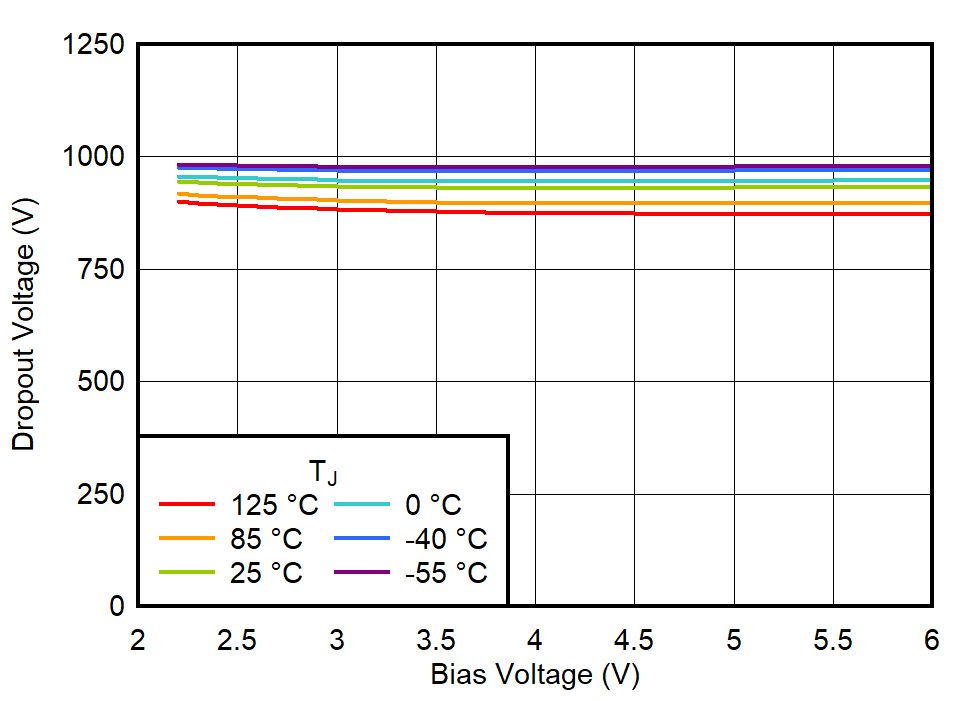

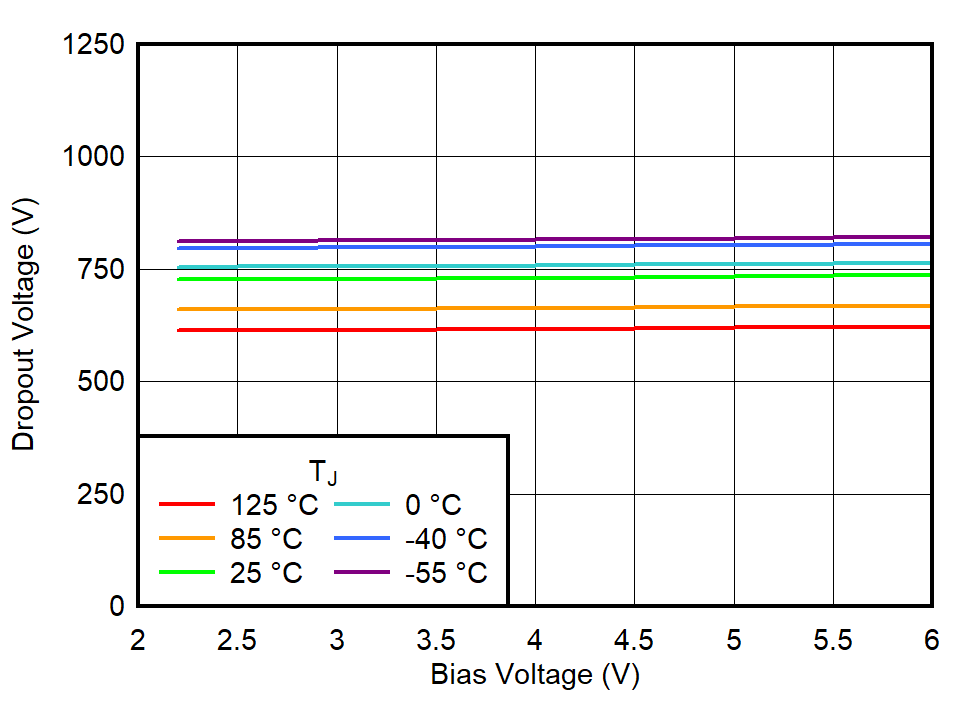

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = VIN, VEN =

1.1 V |

Figure 6-35 Dropout Voltage vs Bias Voltage for IOUT = 500 mA

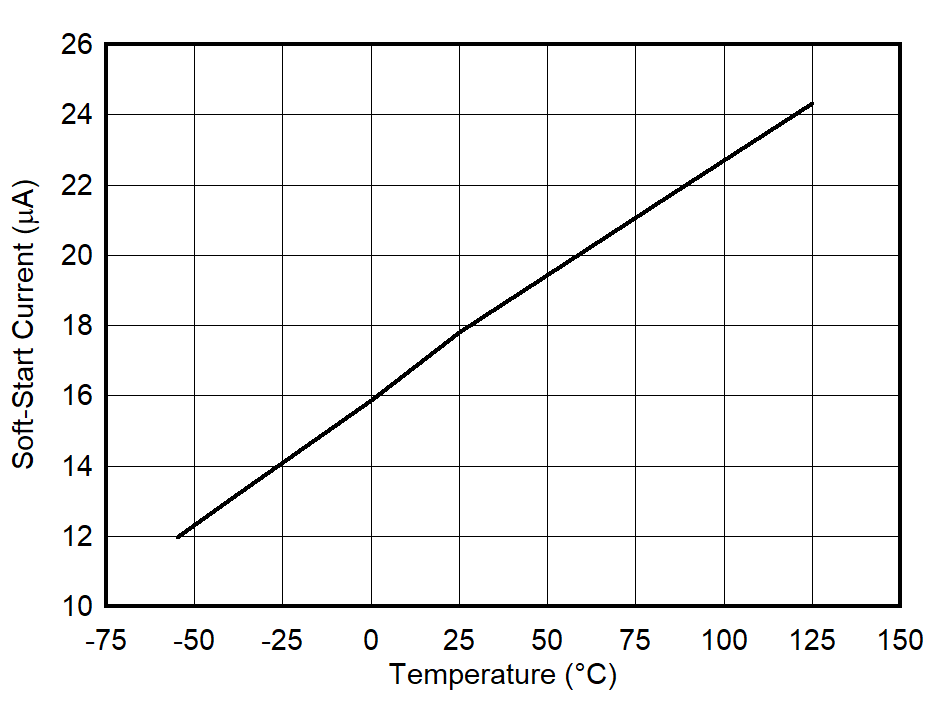

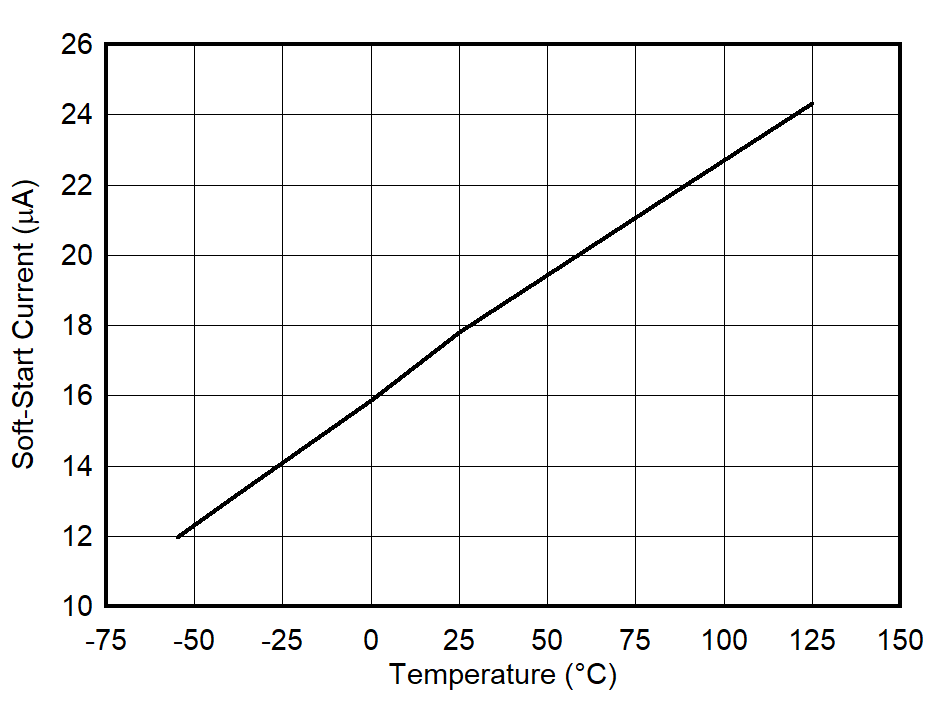

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = VIN =

6 V, VOUT =

0.65 V, VEN = 1.5 V, IOUT = 0

A |

Figure 6-37 Soft-Start Current vs Temperature

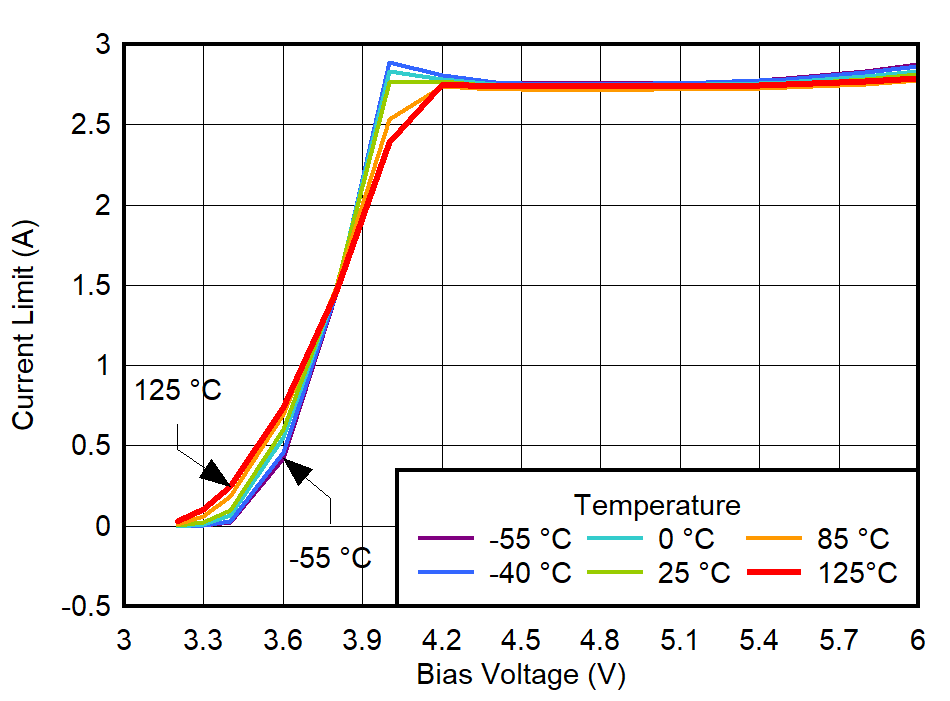

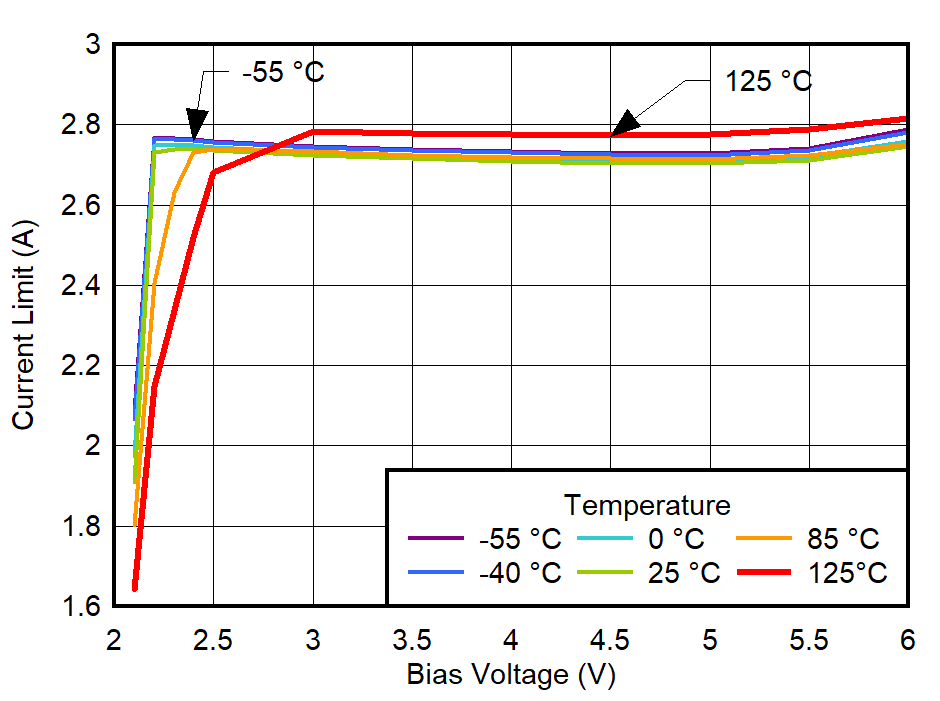

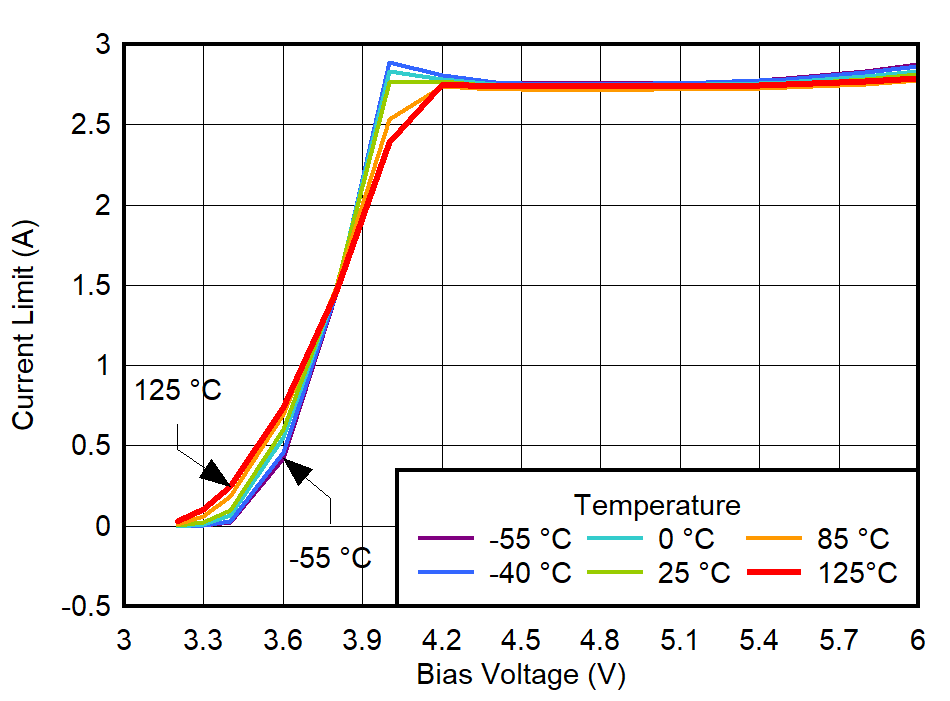

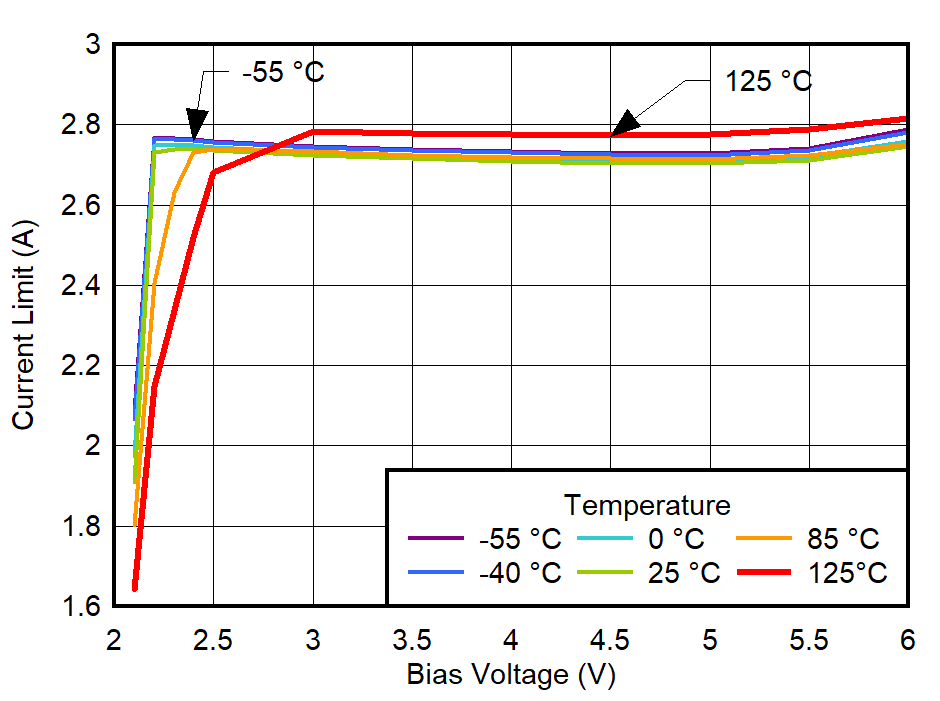

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VEN = 1.1

V |

Figure 6-39 Current Limit vs Bias Voltage for VOUT = 3.3 V

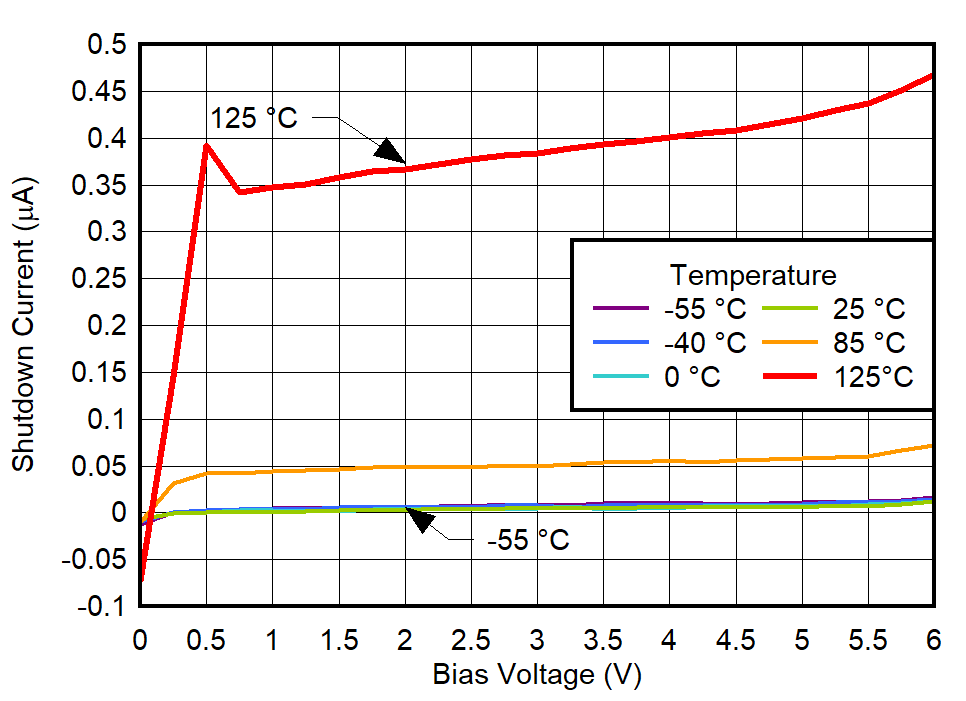

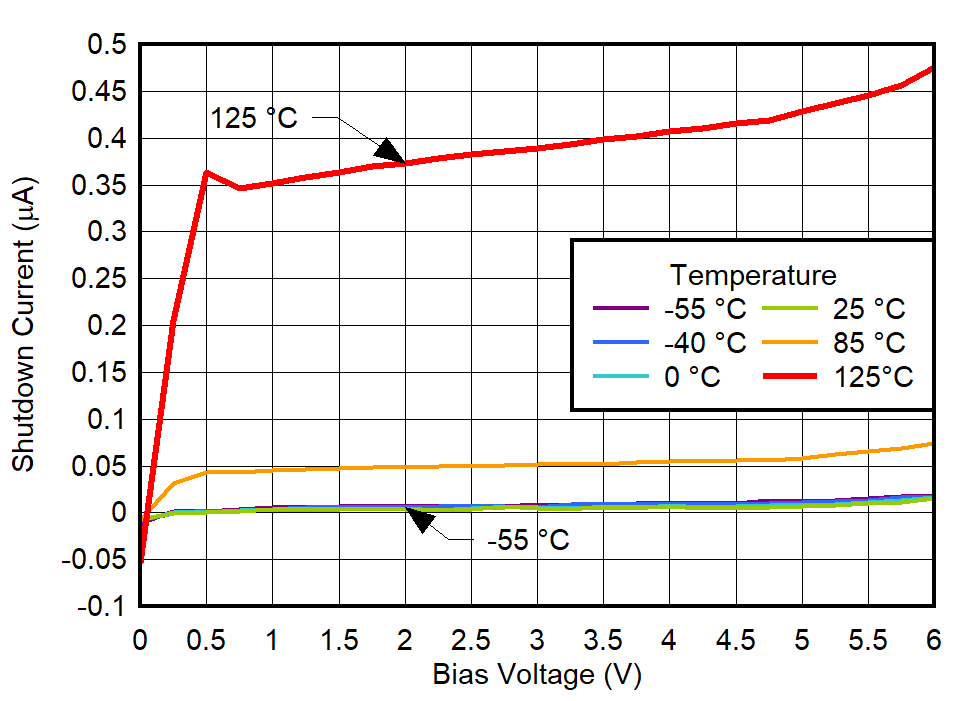

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

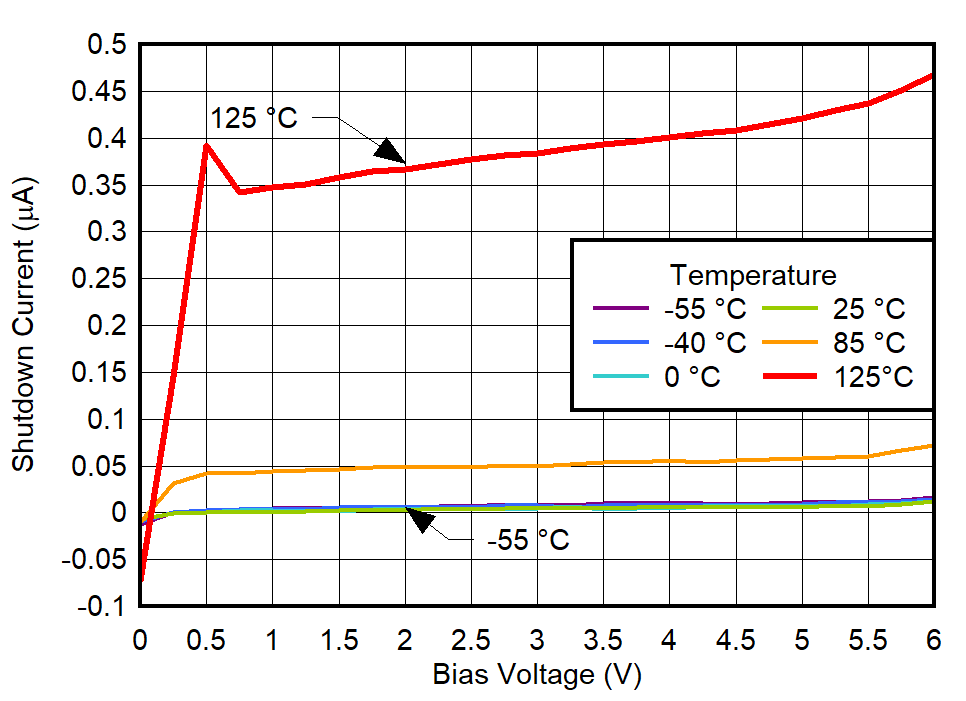

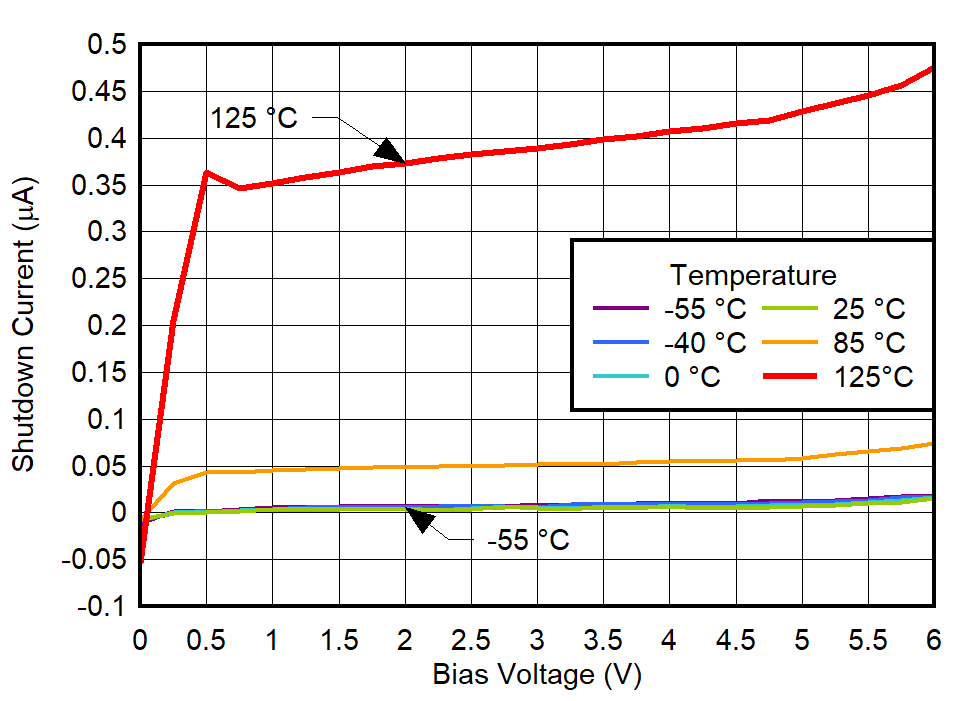

VEN = 0.4 V |

Figure 6-41 Shutdown Current vs Bias Voltage for VIN = 6 V

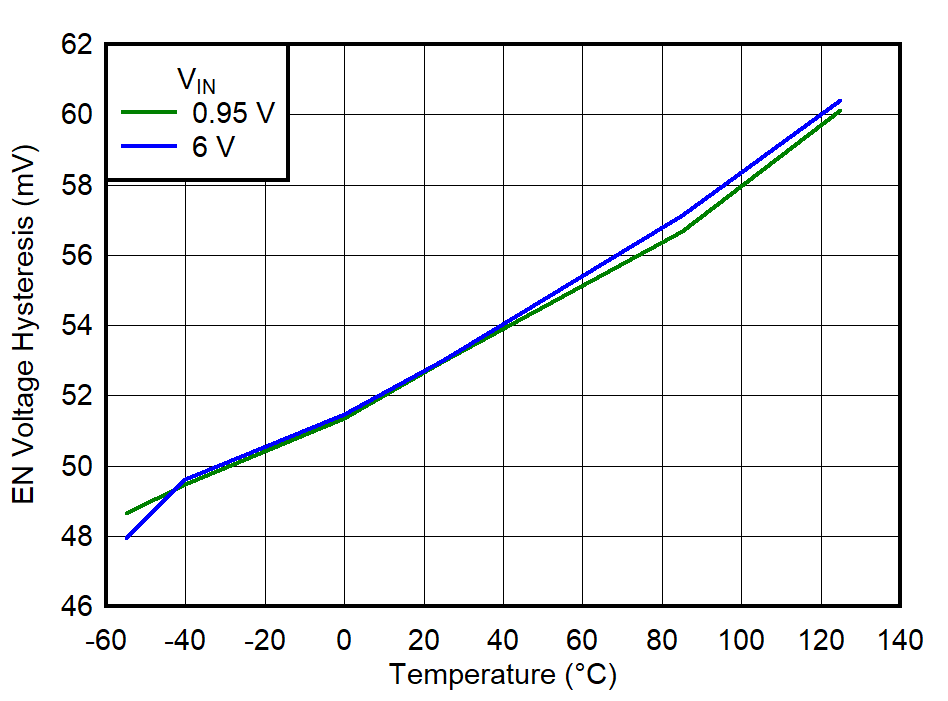

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 6 V |

| |

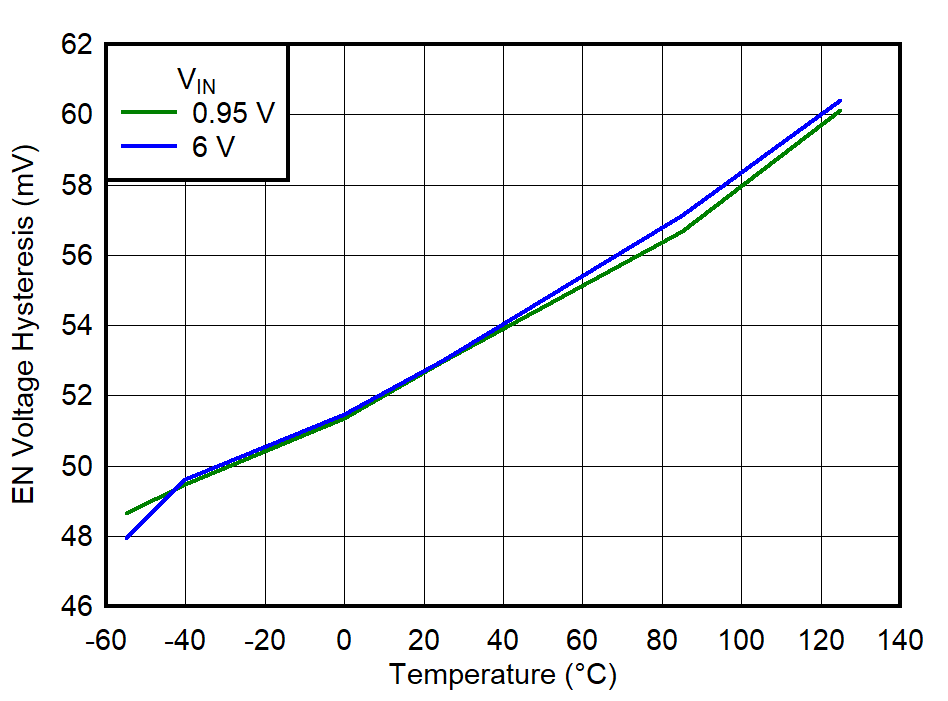

Figure 6-43 Enable Voltage Hysteresis vs Temperature

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V,

1.1 V ≤ VEN ≤ 6 V |

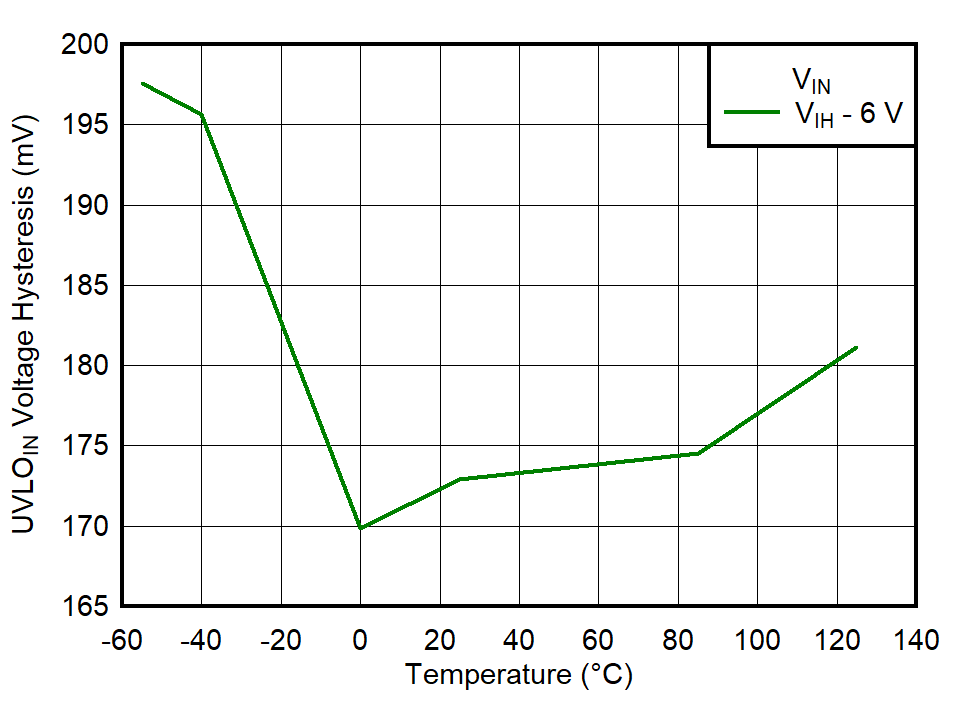

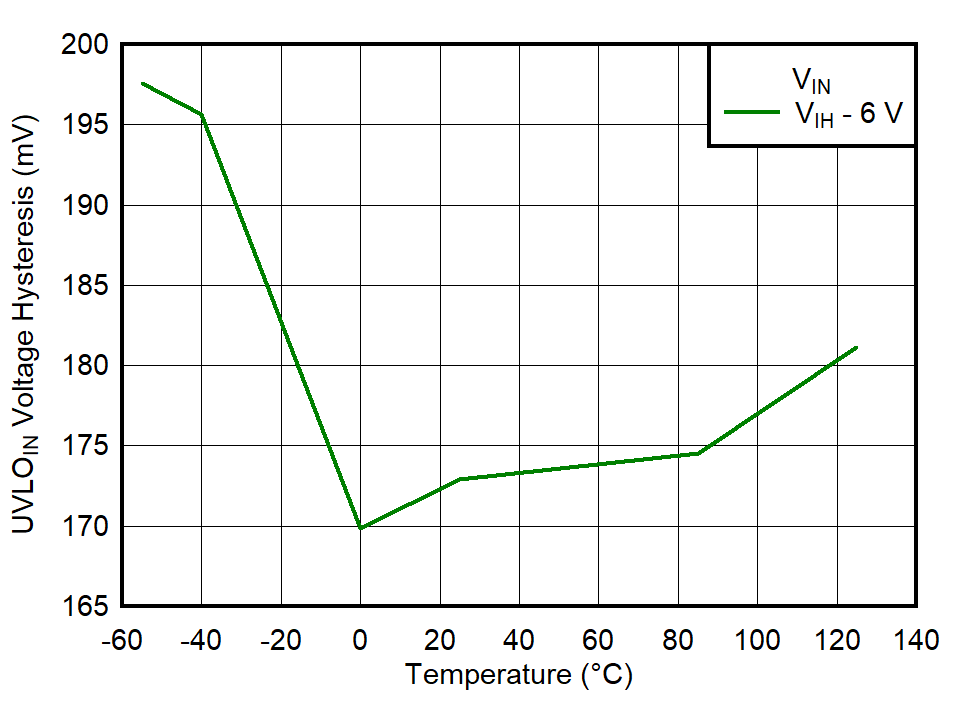

Figure 6-45 UVLOIN Voltage Hysteresis vs Temperature

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V,

1.1 V ≤ VEN ≤ 6 V |

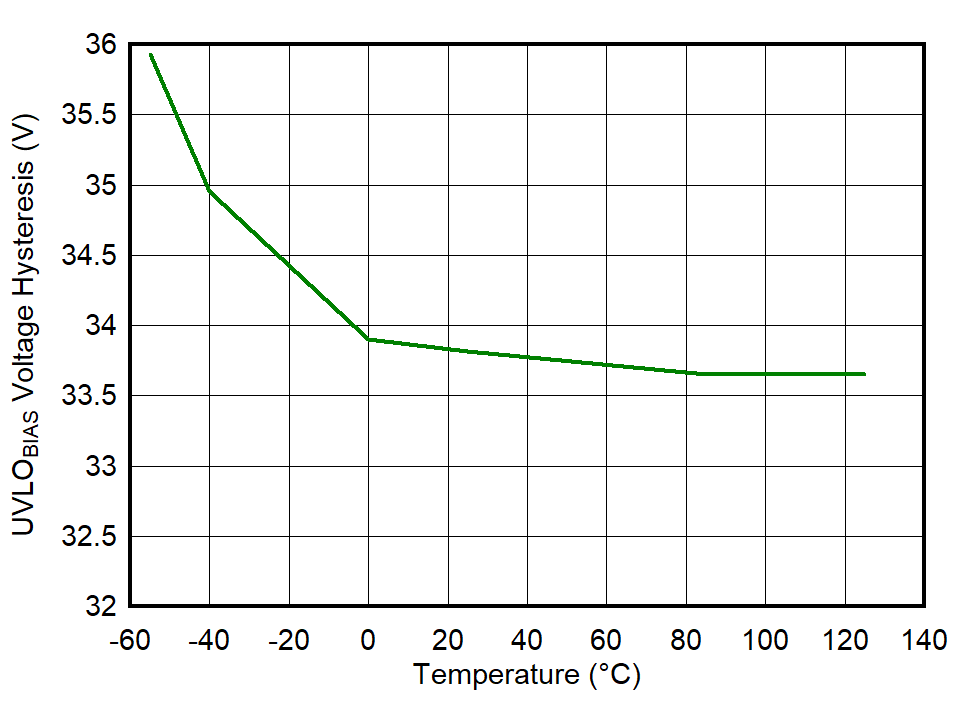

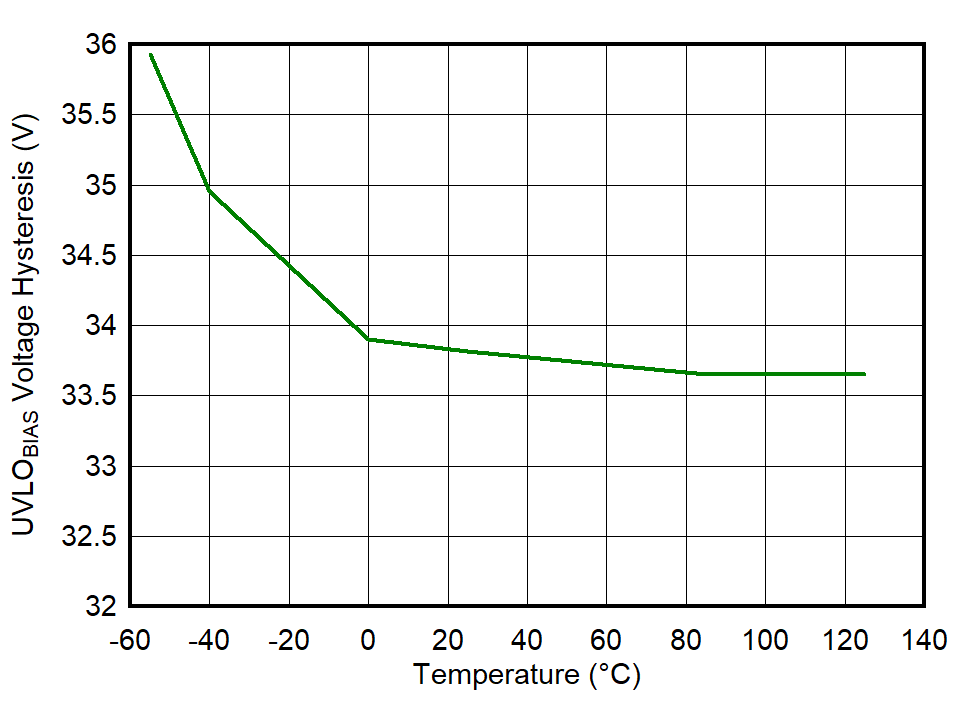

Figure 6-47 UVLOBIAS Voltage Hysteresis vs Temperature

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 6 V, VOUT(NOM) = 0.65 V,

VBIAS = 6 V, IOUT = 2 mA,

VEN = 6 V |

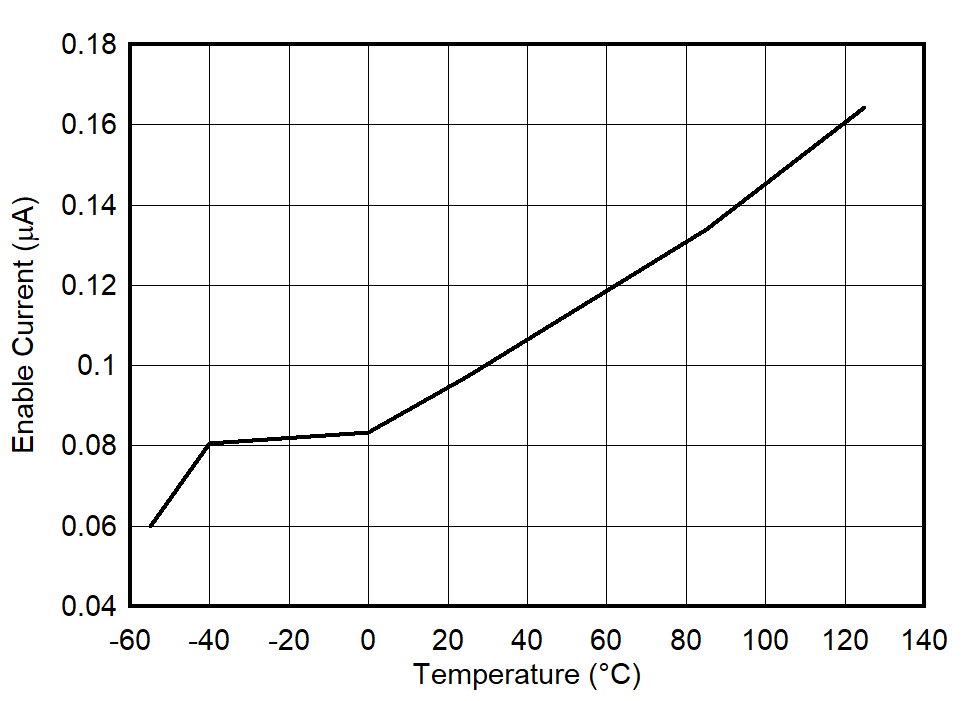

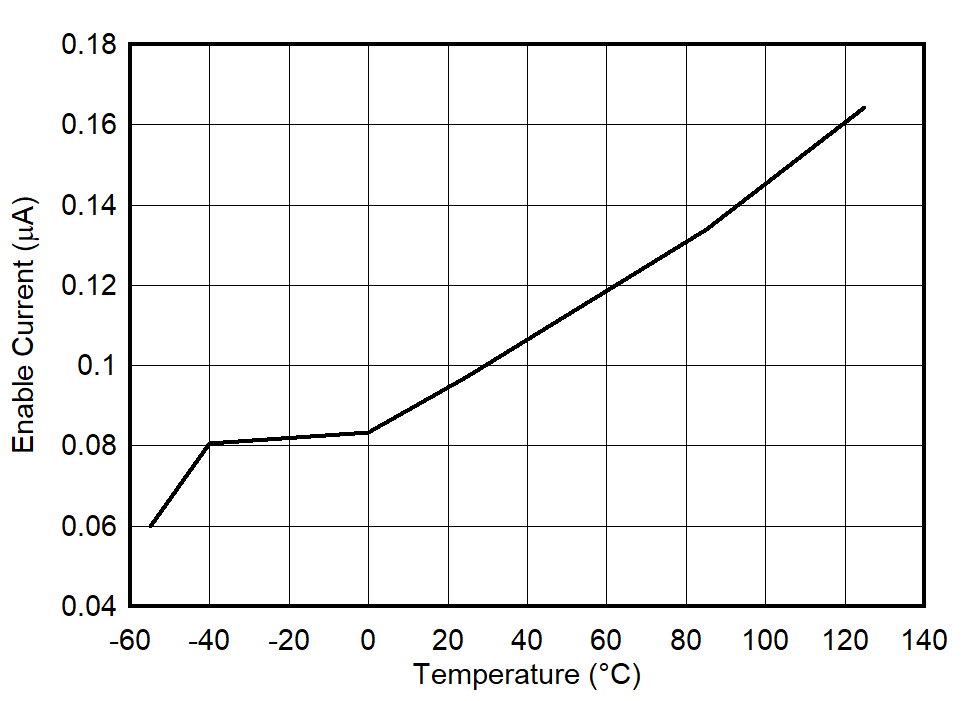

Figure 6-49 EN

Pin Current vs Temperature

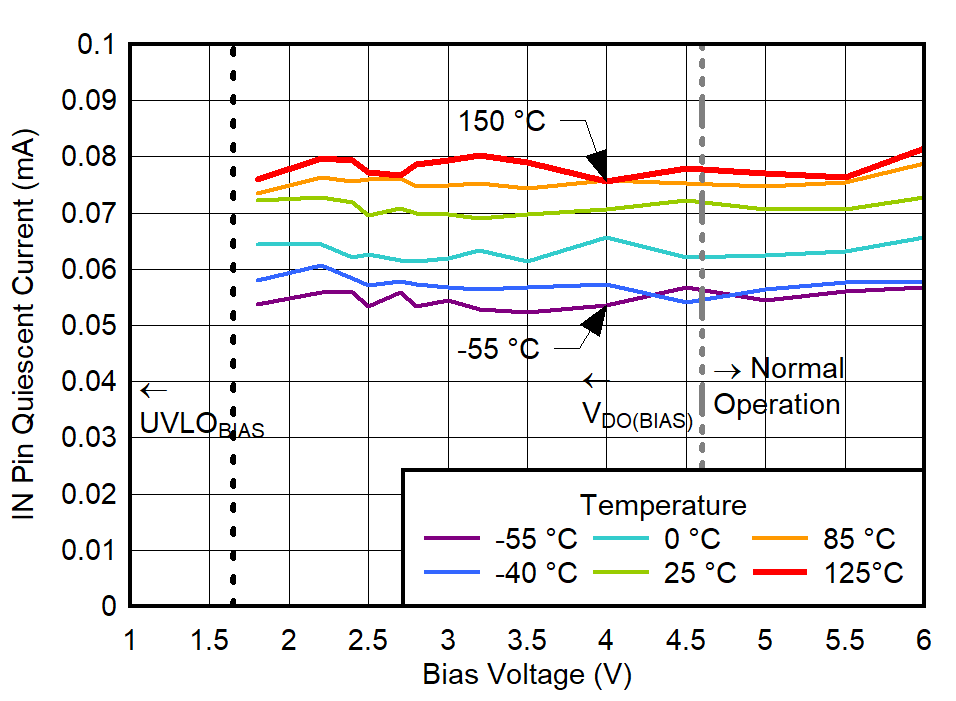

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VEN = 1.1 V |

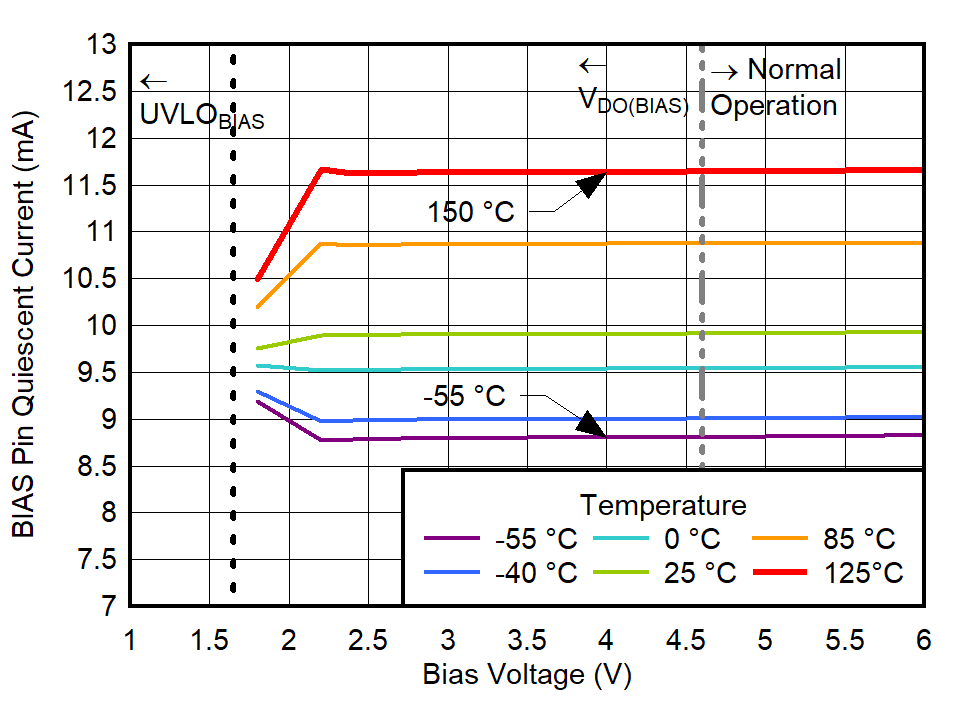

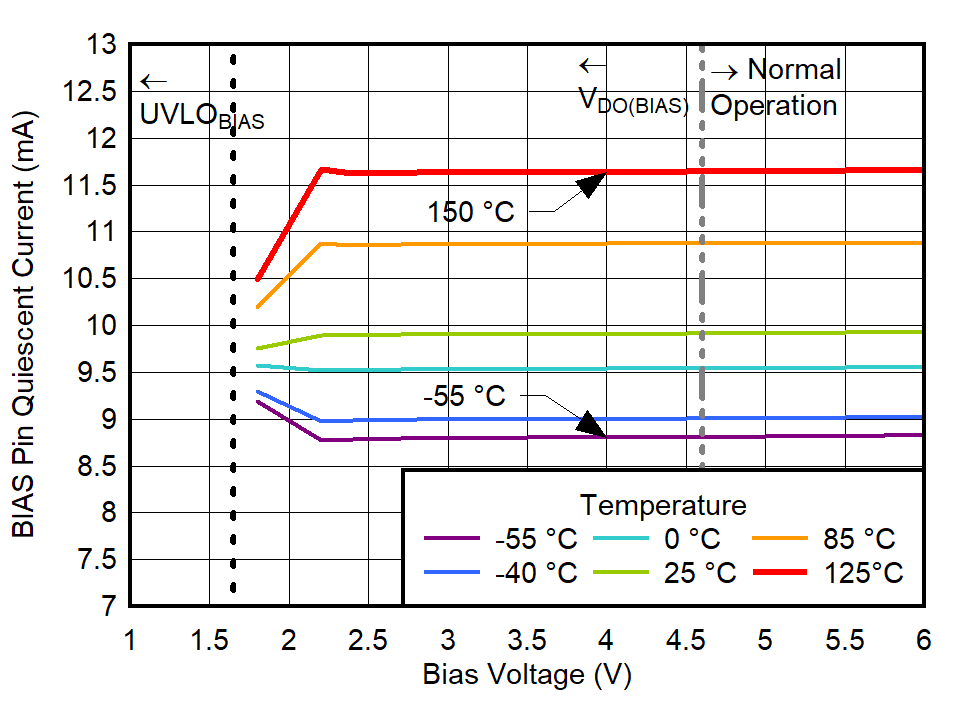

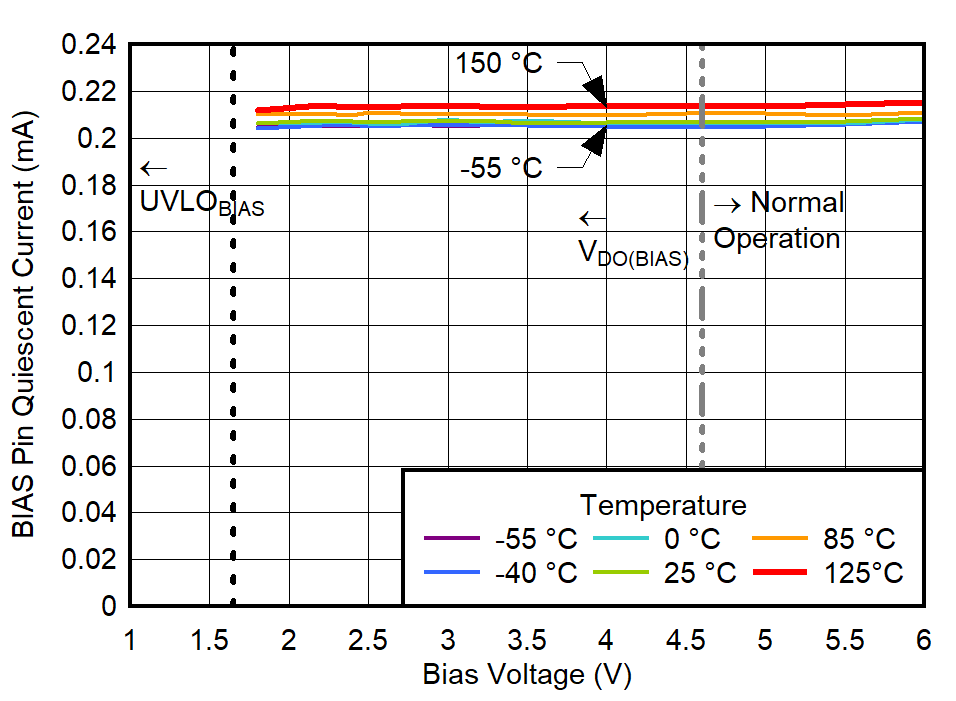

Figure 6-51 BIAS

Pin Quiescent Current vs Bias Voltage for IOUT = 1.5 A

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VEN = 1.1 V |

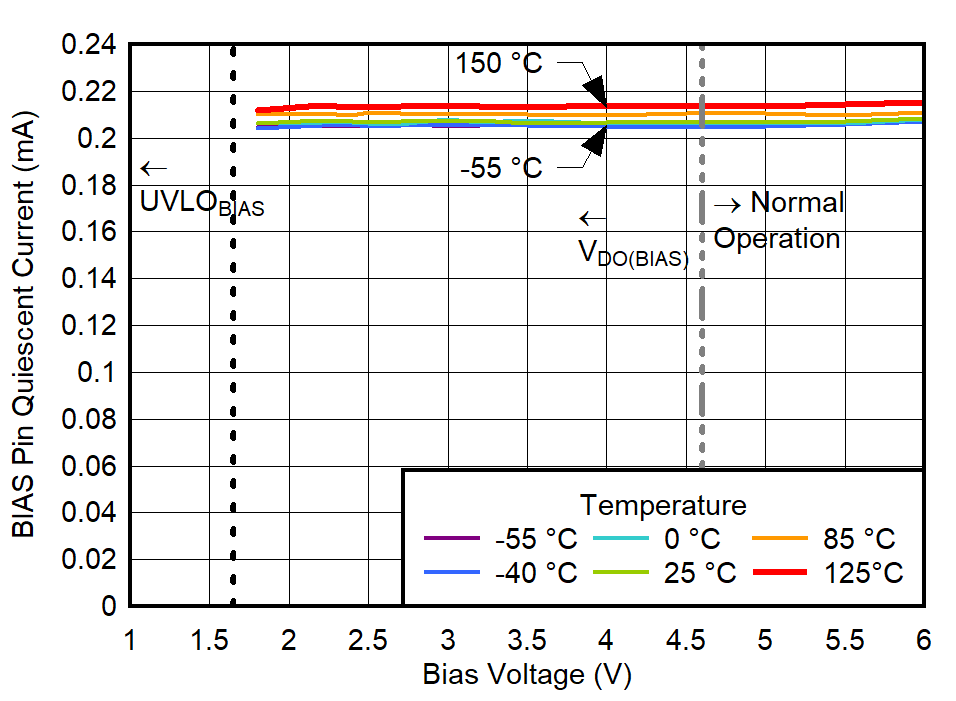

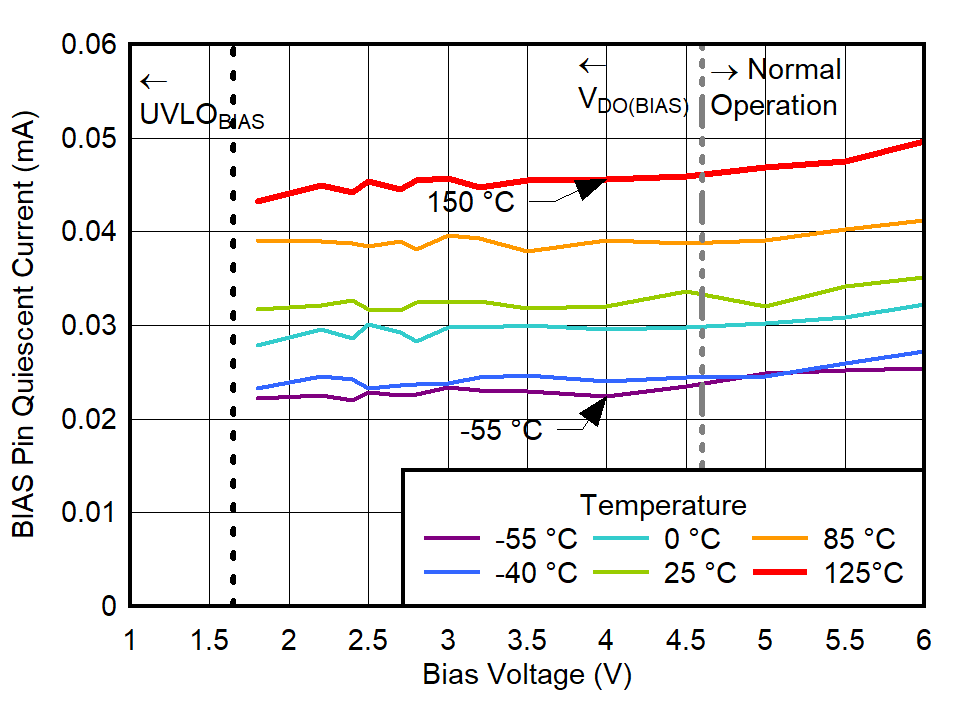

Figure 6-53 BIAS

Pin Quiescent Current vs Bias Voltage for IOUT = 10 mA

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VEN = 1.1 V |

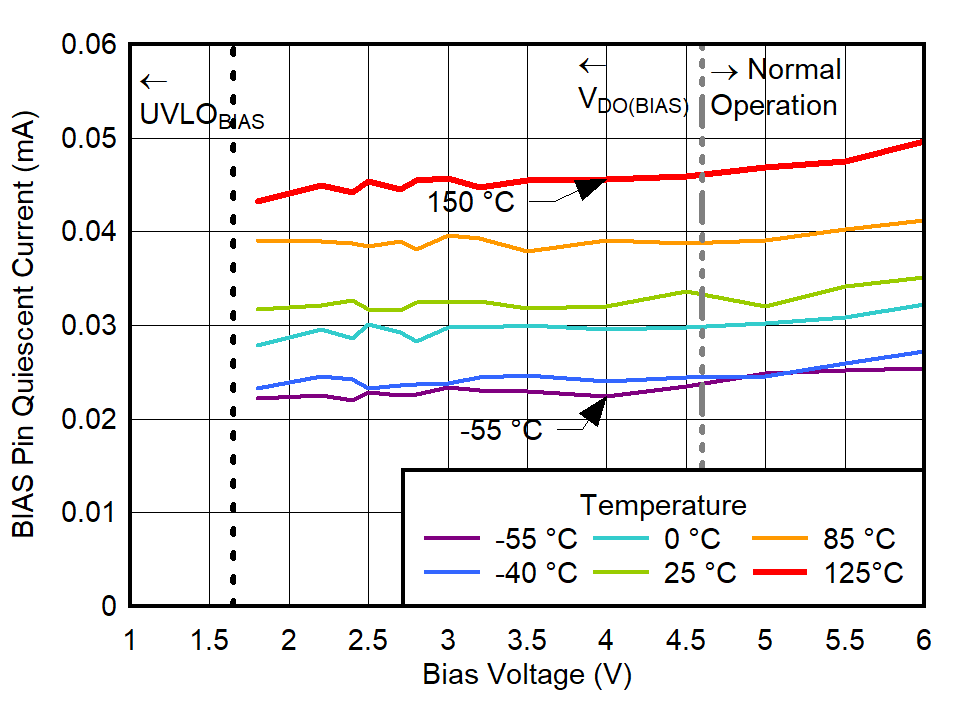

Figure 6-55 BIAS

Pin Quiescent Current vs Bias Voltage for IOUT = 0 A

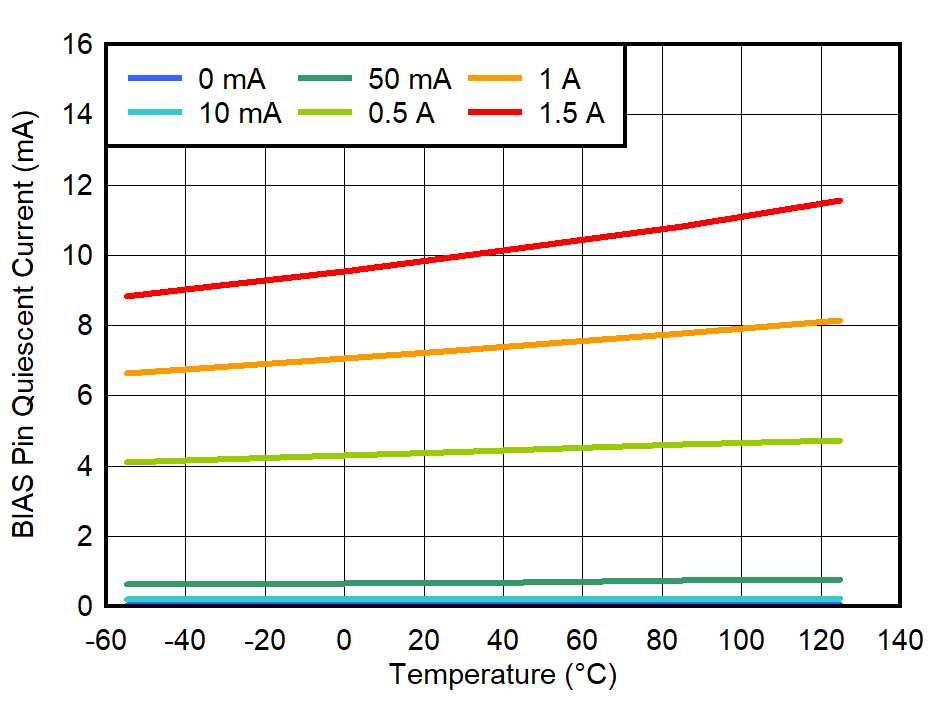

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VBIAS = 5 V, VEN = 1.1

V |

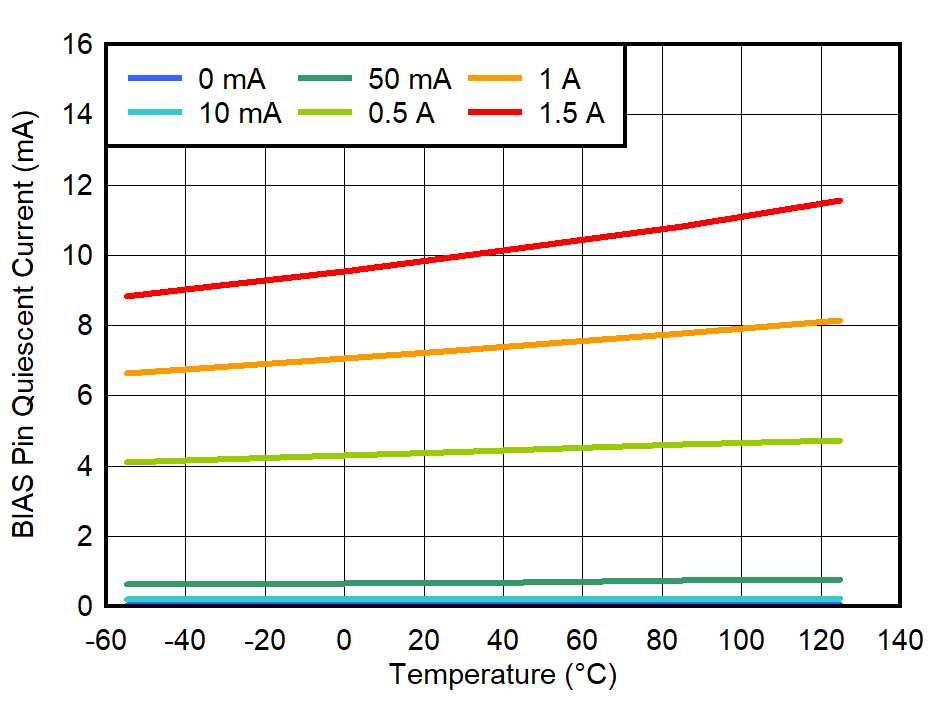

Figure 6-57 BIAS

Pin Quiescent Current vs Temperature

| CIN = 0 μF, COUT = 10 μF,

CBIAS = 1 μF |

Figure 6-2 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 750 mA,

VOUT = 1.8 V

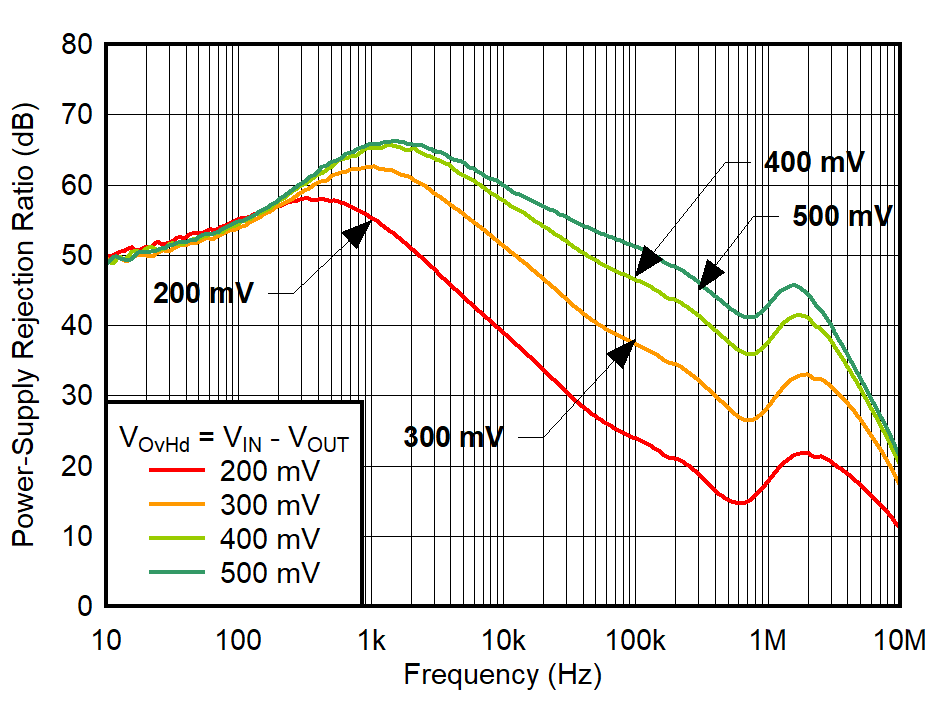

| CIN = 0 μF, COUT = 10 μF,

CBIAS = 1 μF |

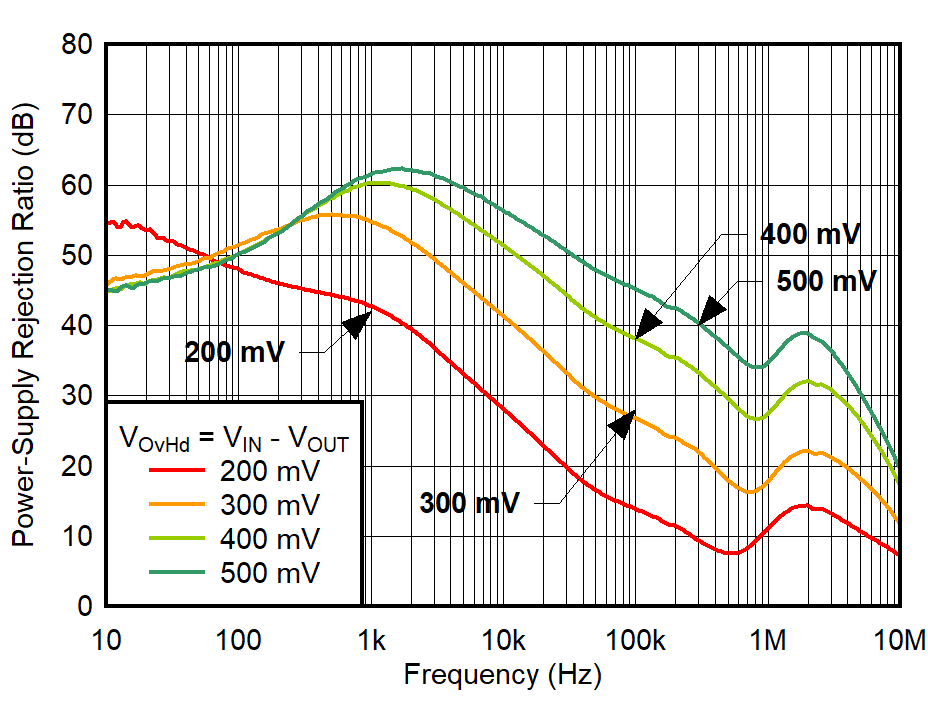

Figure 6-4 PSRR

vs Frequency and Overhead (OvHd) Voltage for IOUT = 1.5 A,

VOUT = 1.8 V

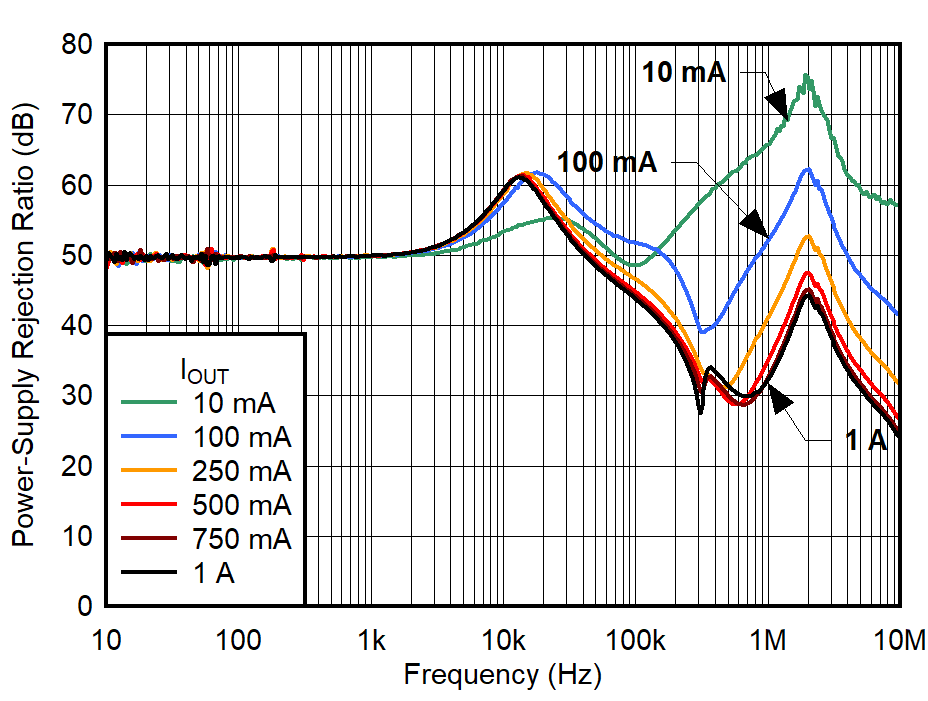

| CIN = 0 μF, COUT = 10 μF,

CBIAS = 1 μF |

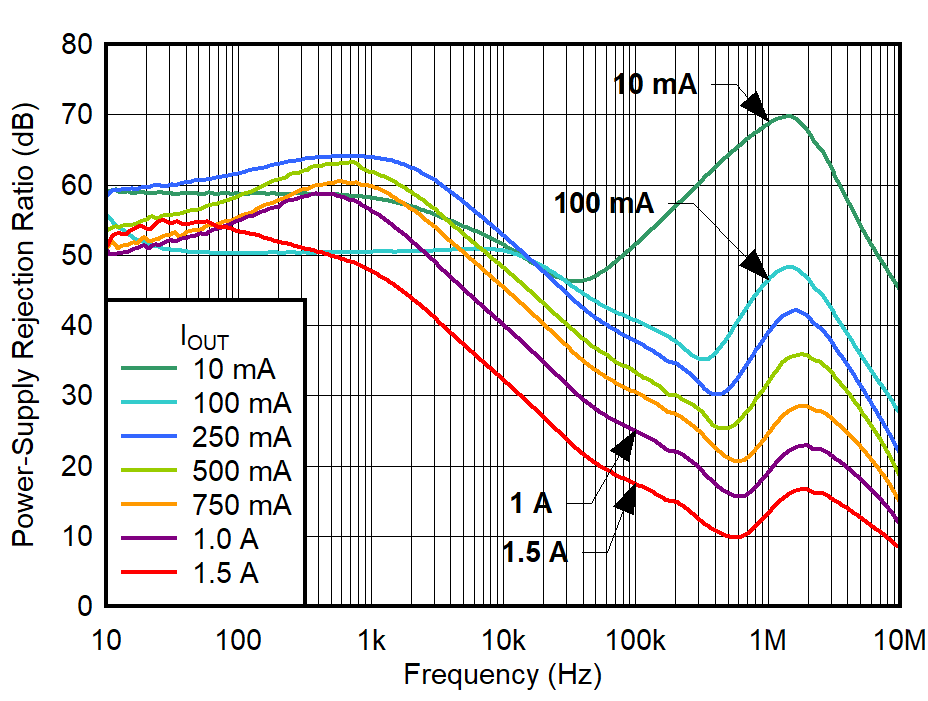

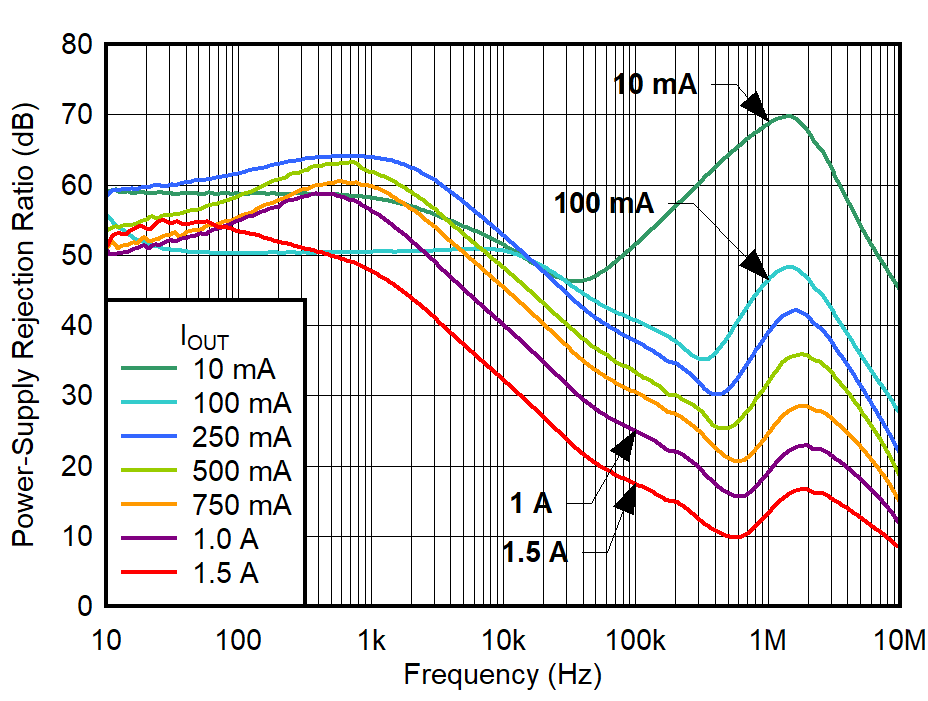

Figure 6-6 PSRR

vs Frequency and IOUT for VOvHd = 200 mV

| CIN = COUT = 10 μF,

CBIAS = 1 μF |

| |

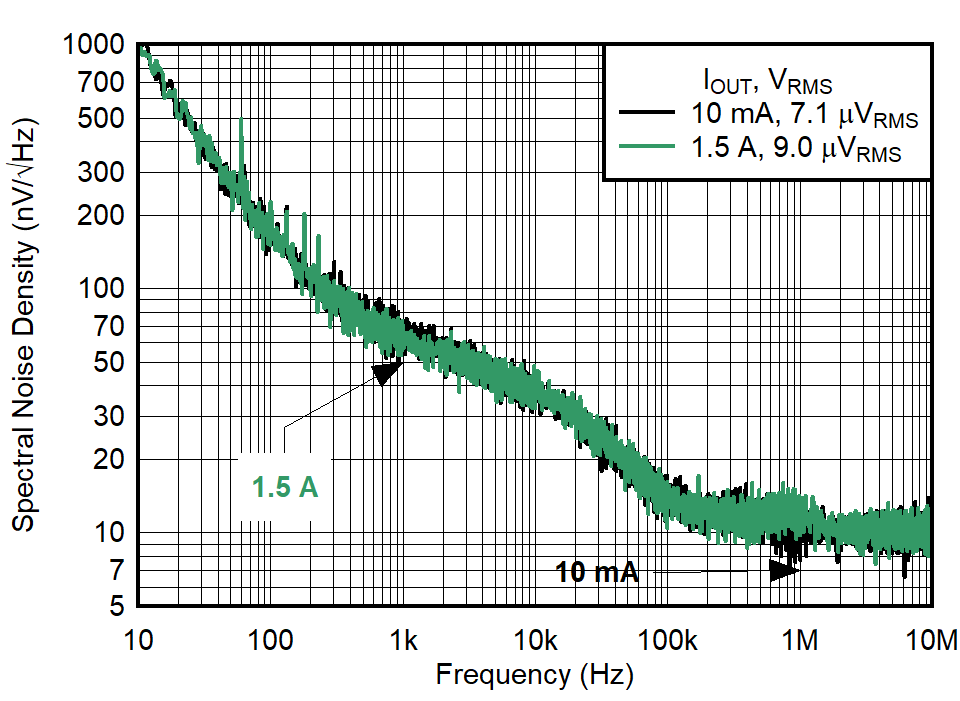

Figure 6-8 Noise

vs Frequency and IOUT for VOUT = 0.65 V

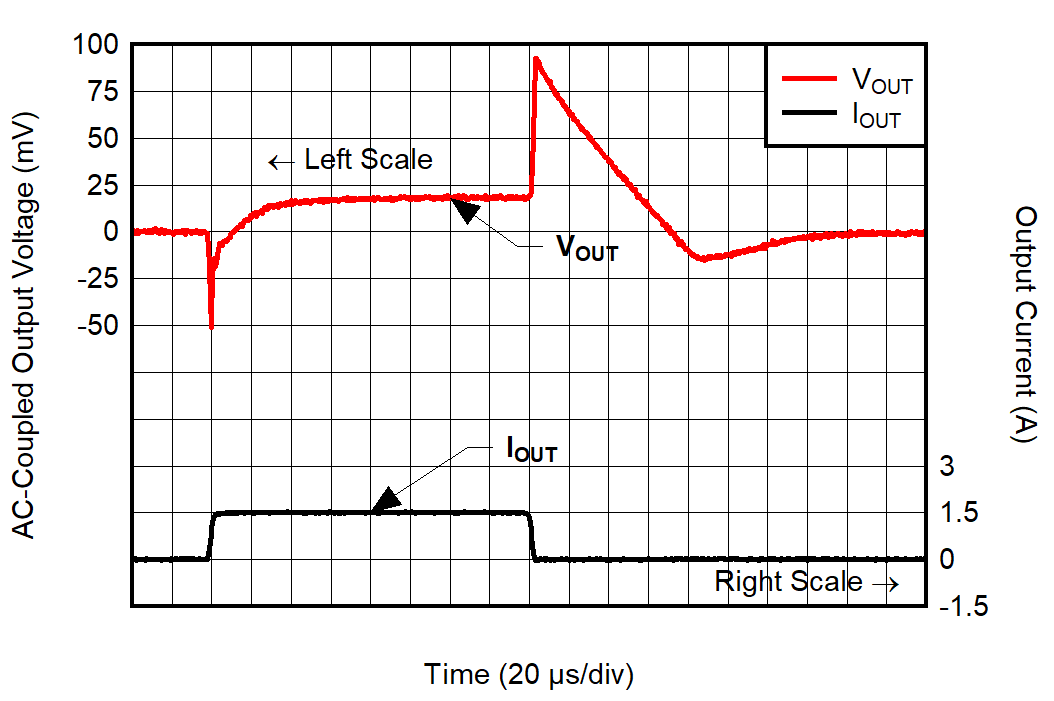

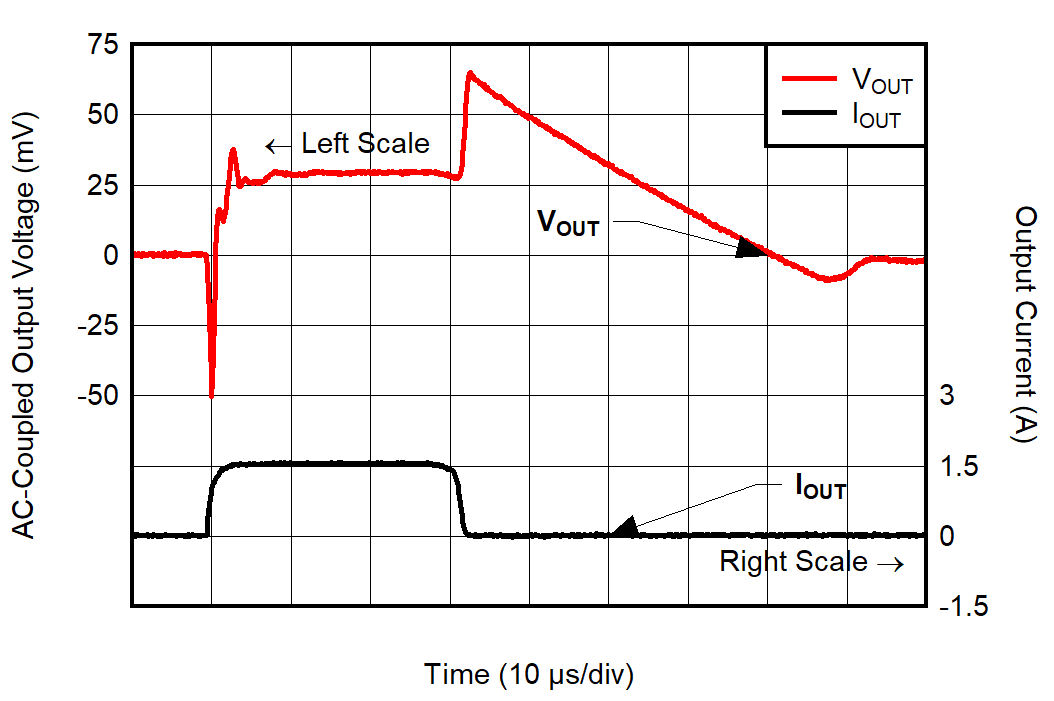

CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 10 mA to

1.5 A to

10 mA at 1

A/μs |

Figure 6-10 Load

Transient for VOUT = 0.65 V

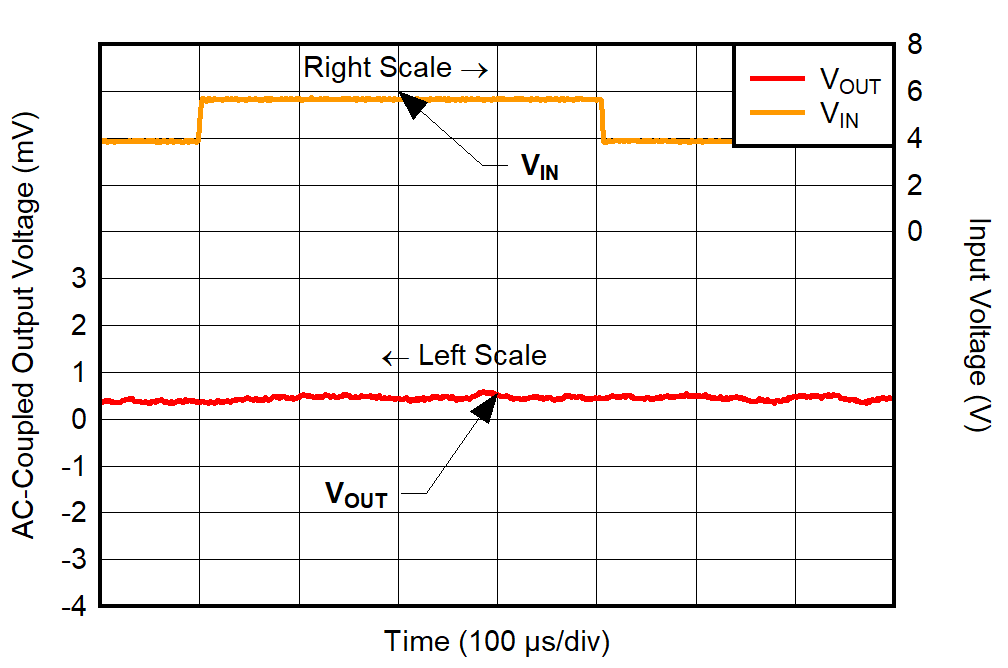

CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

VIN = 0.95

V to 6 V to 0.95 V at 1 V/μs |

Figure 6-12 Line

Transient for VOUT = 0.65 V

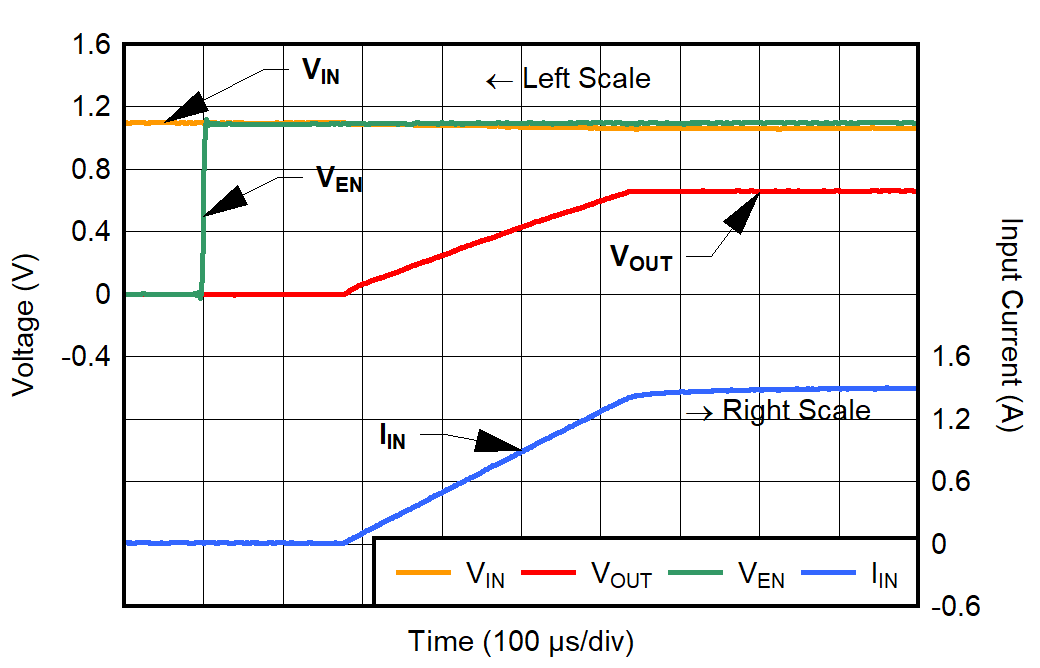

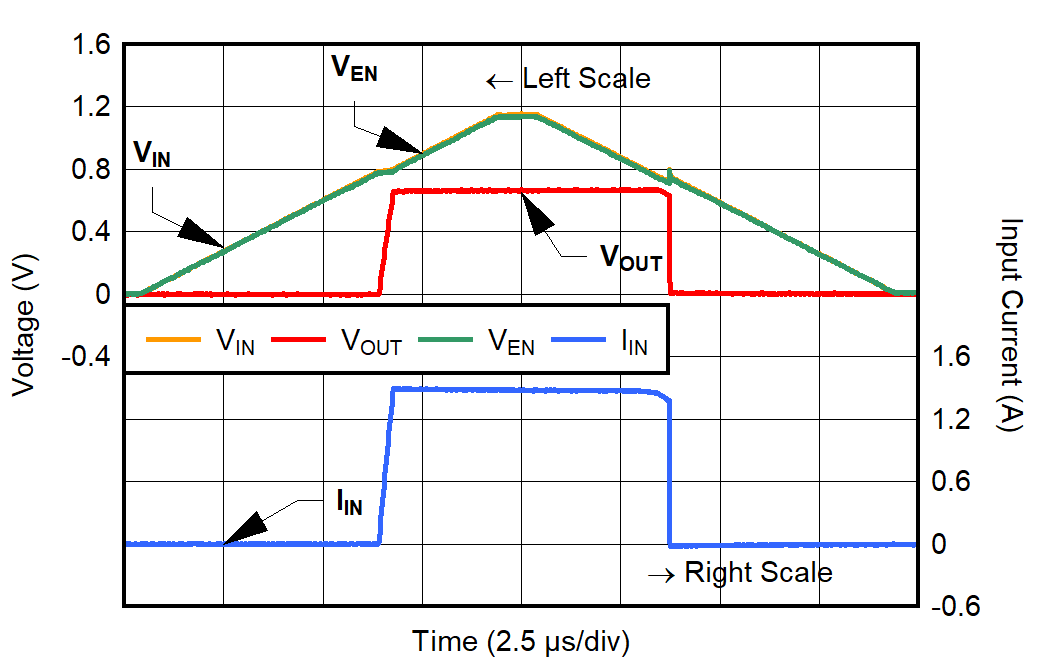

| CIN = COUT = 10 μF,

CBIAS = 1 μF, IOUT = 1.5 A,

VBIAS = 5 V |

| |

Figure 6-14 Input

Ramp-Up and Ramp-Down

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V, VEN = 1.1

V |

Figure 6-16 IN

Line Regulation for VOUT = 0.65 V, IOUT = 0 A

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V, VEN = 1.1

V |

Figure 6-18 IN

Line Regulation for VOUT = 0.65 V, IOUT = 1.5

A

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, VEN = 1.1

V |

Figure 6-20 BIAS

Line Regulation for VOUT = 0.65 V,

IOUT = 10 mA

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V, VEN = 1.1

V |

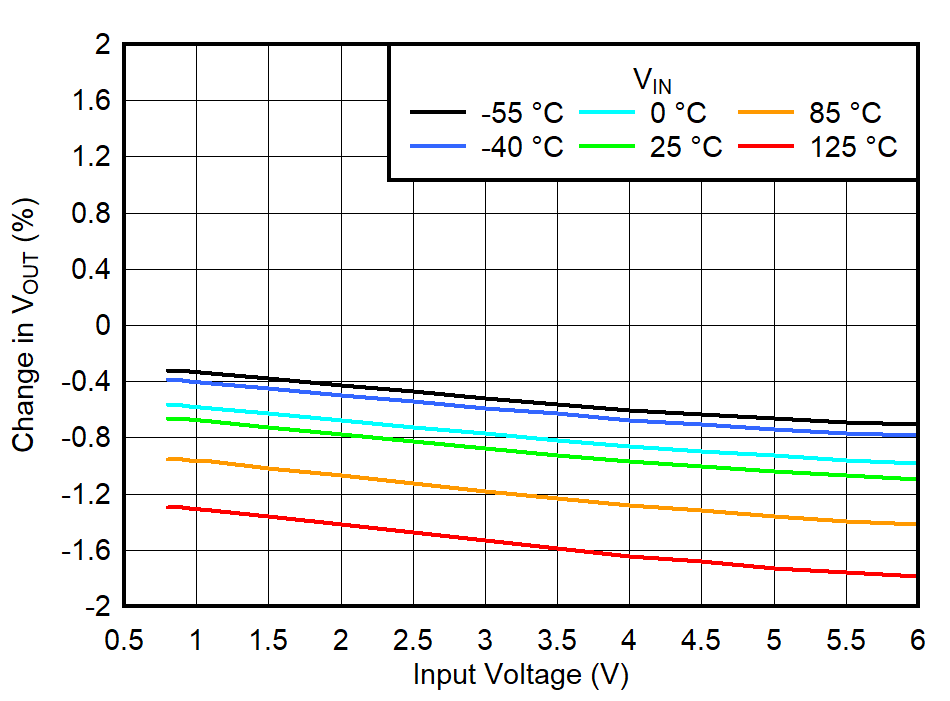

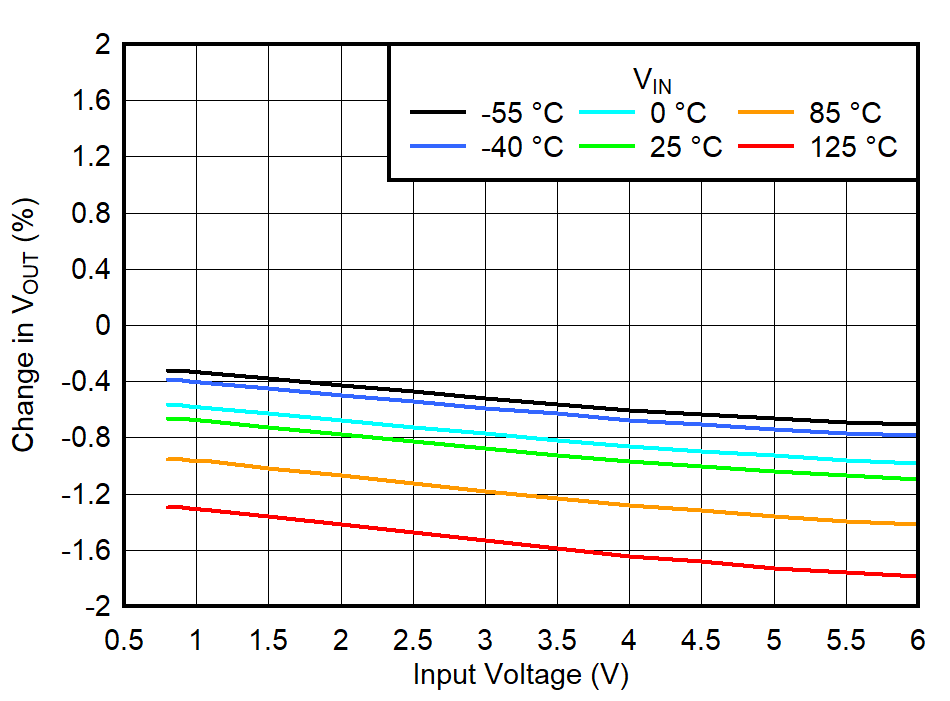

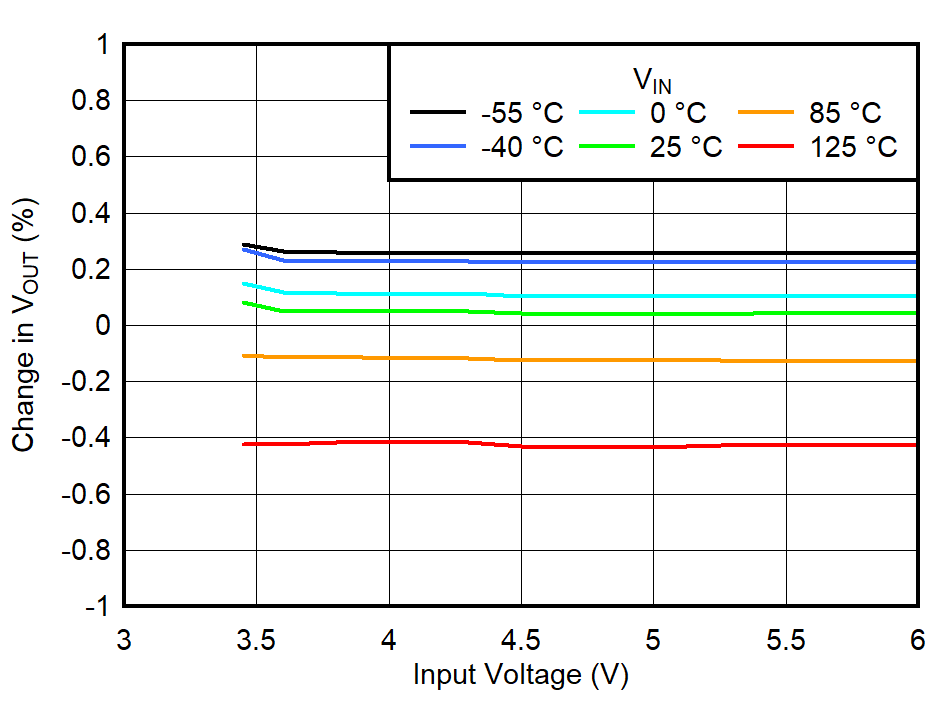

Figure 6-22 IN

Line Regulation for VOUT = 3.3 V, IOUT = 0 A

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V, VEN = 1.1

V |

Figure 6-24 IN

Line Regulation for VOUT = 3.3 V, IOUT = 1.5 A

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

3.6 V ≤ VIN ≤ 6

V, VEN = 1.1 V |

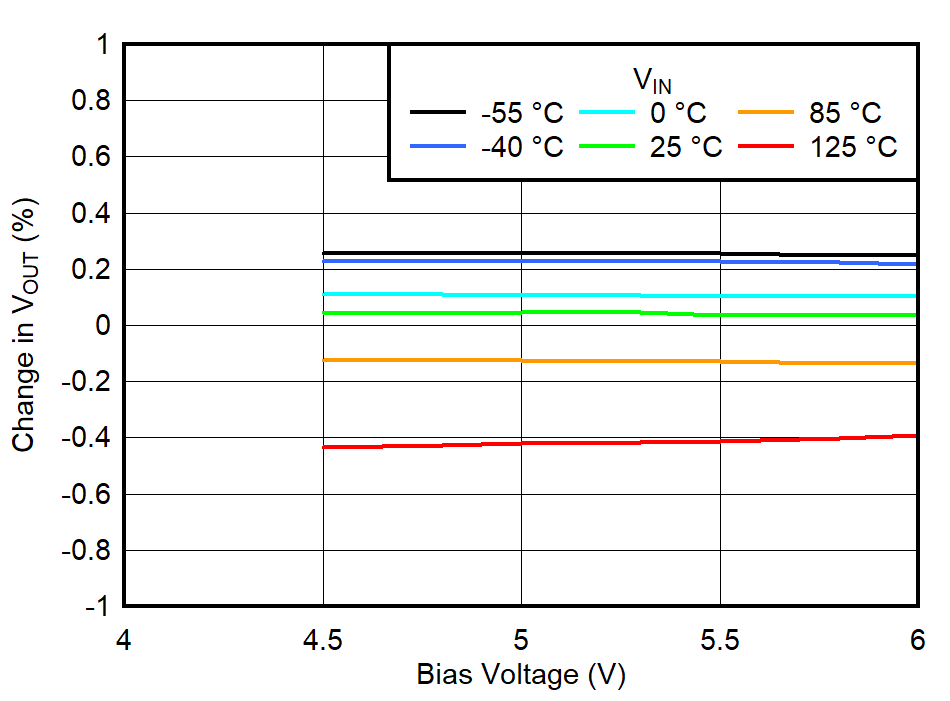

Figure 6-26 BIAS

Line Regulation for VOUT = 3.3 V, IOUT = 10 mA

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, 2.3 V ≤ VBIAS ≤

5 V, VEN = 1.1 V |

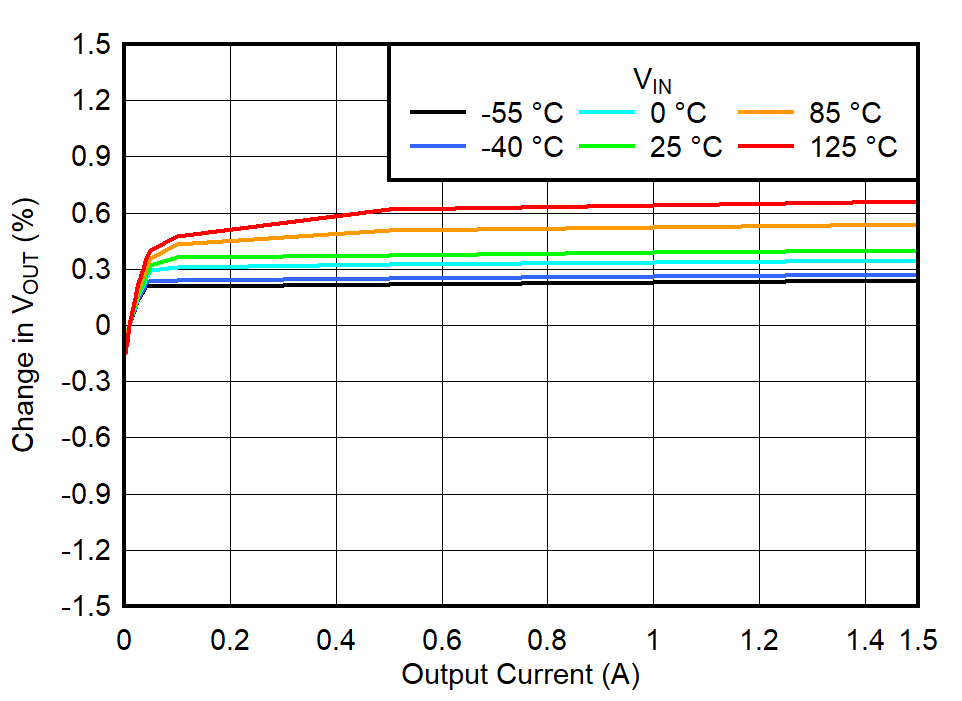

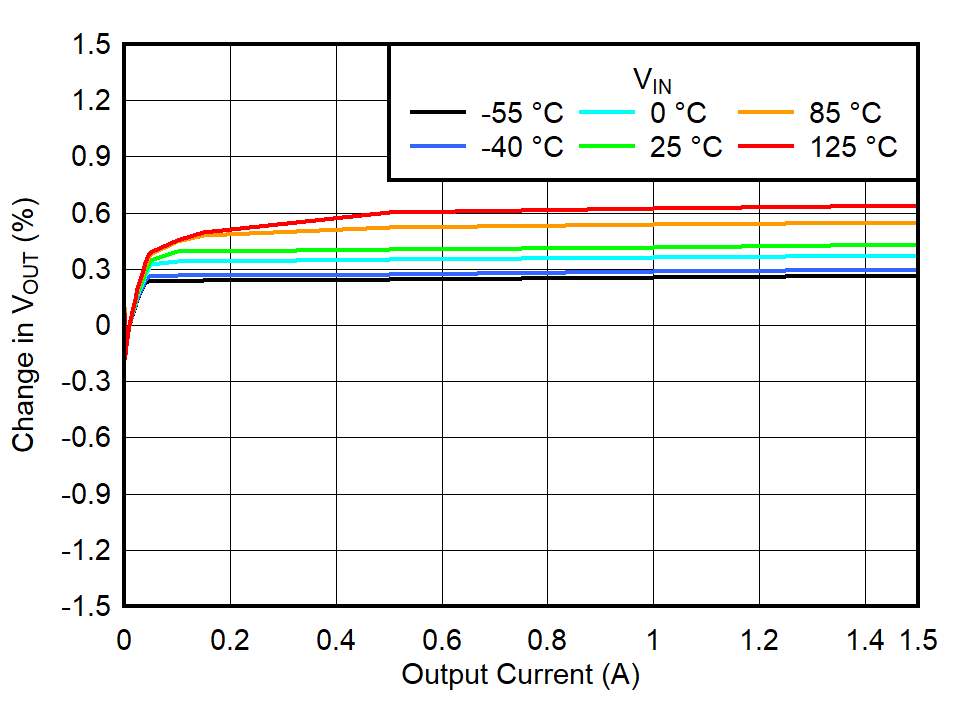

Figure 6-28 Load

Regulation for IOUT = 0 A to Load,

VOUT = 0.65 V

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, 2.3 V ≤ VBIAS ≤

5 V, VEN = 1.1 V |

Figure 6-30 Load

Regulation for IOUT = 10 mA to Load,

VOUT = 0.65 V

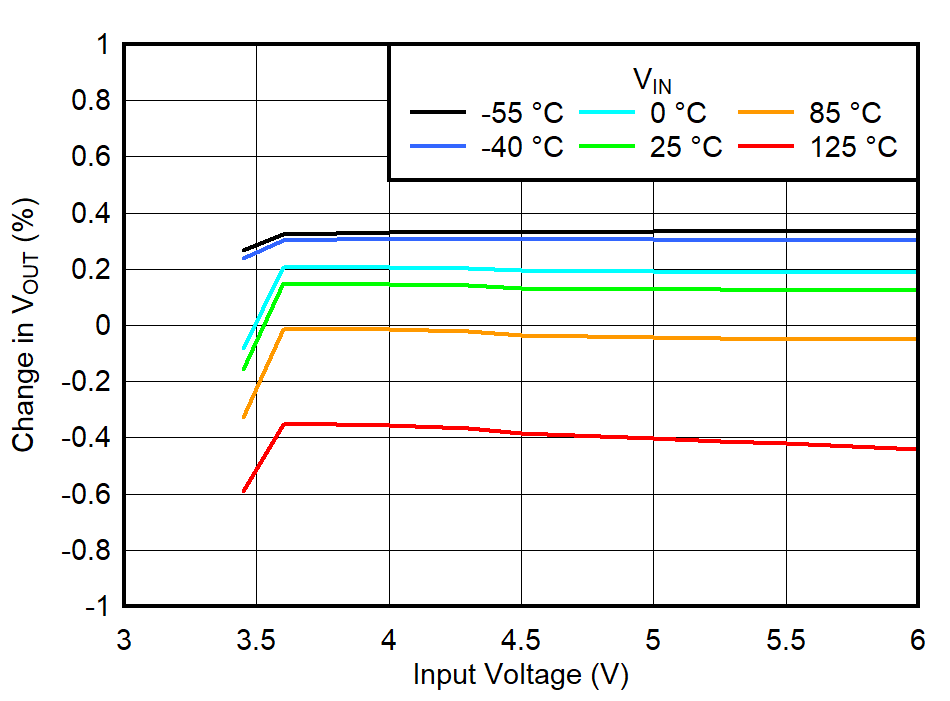

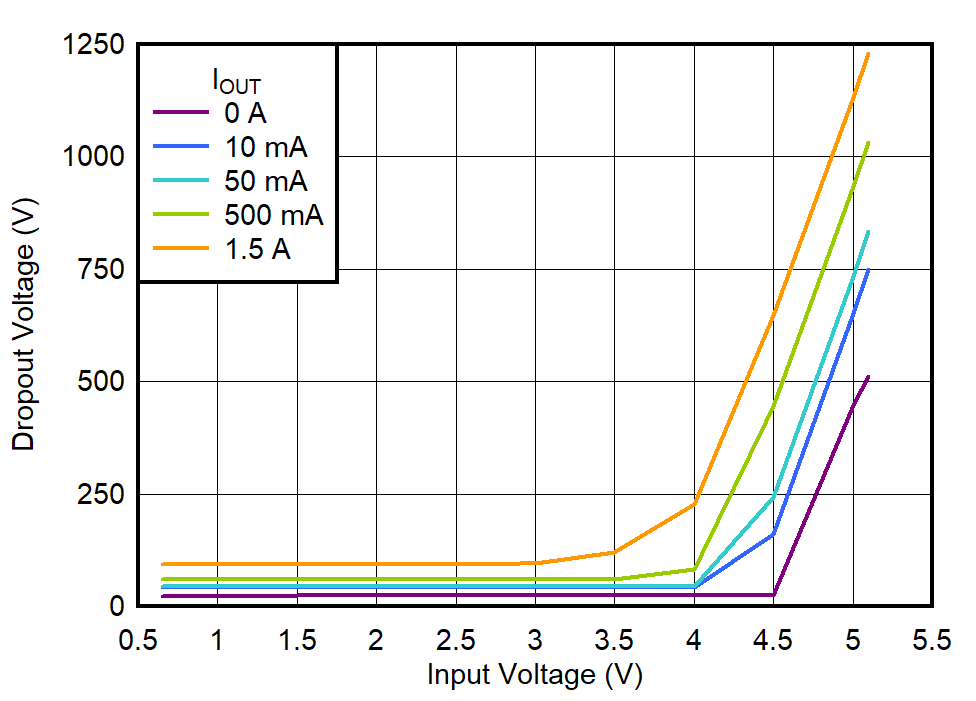

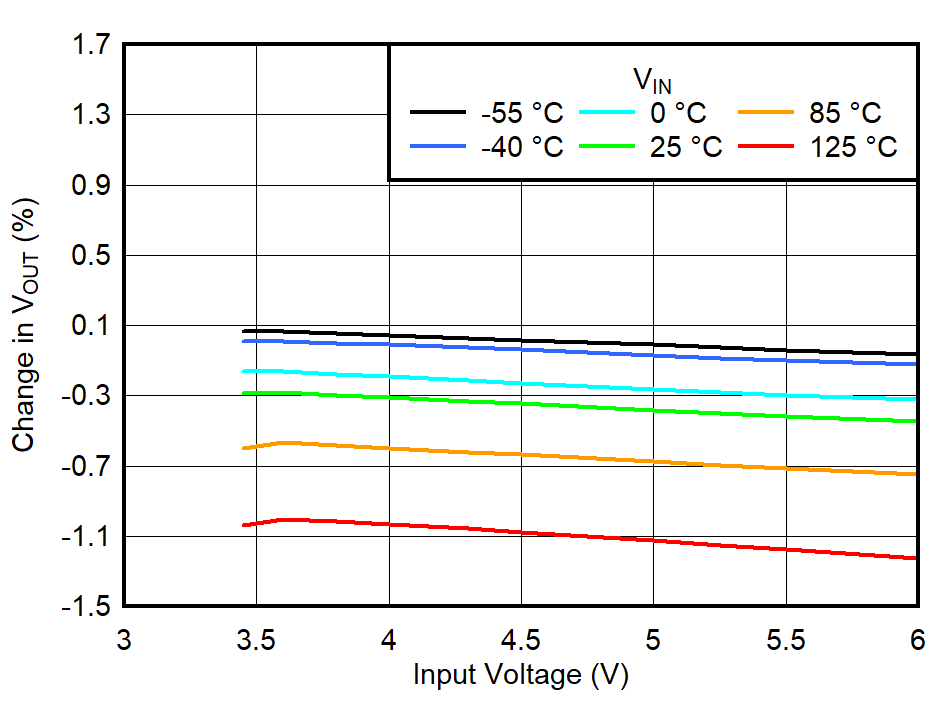

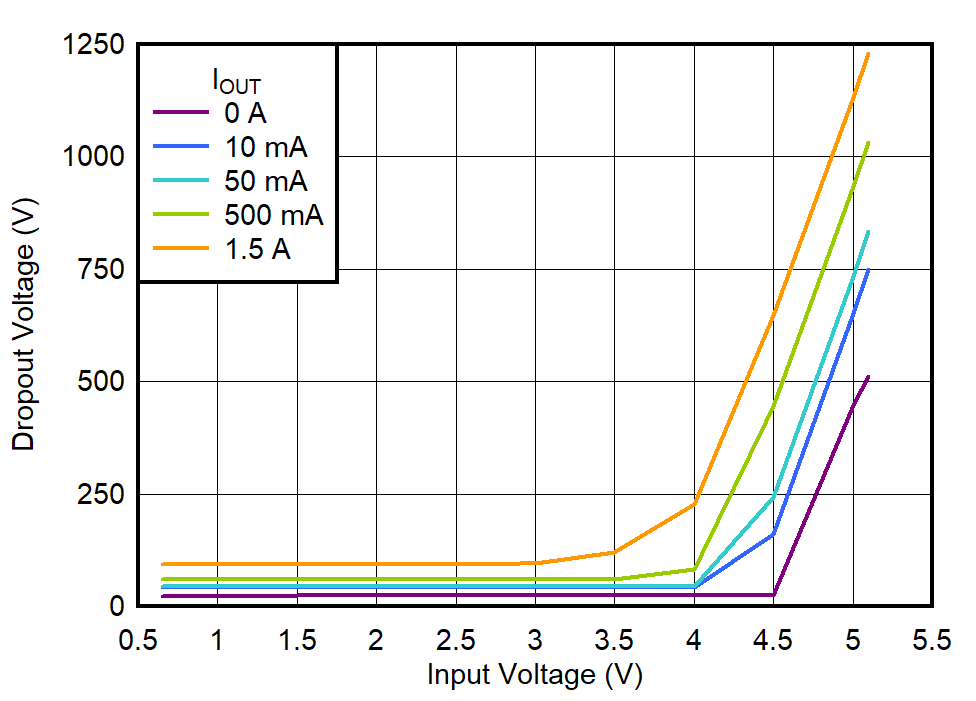

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V, VEN = 1.1

V |

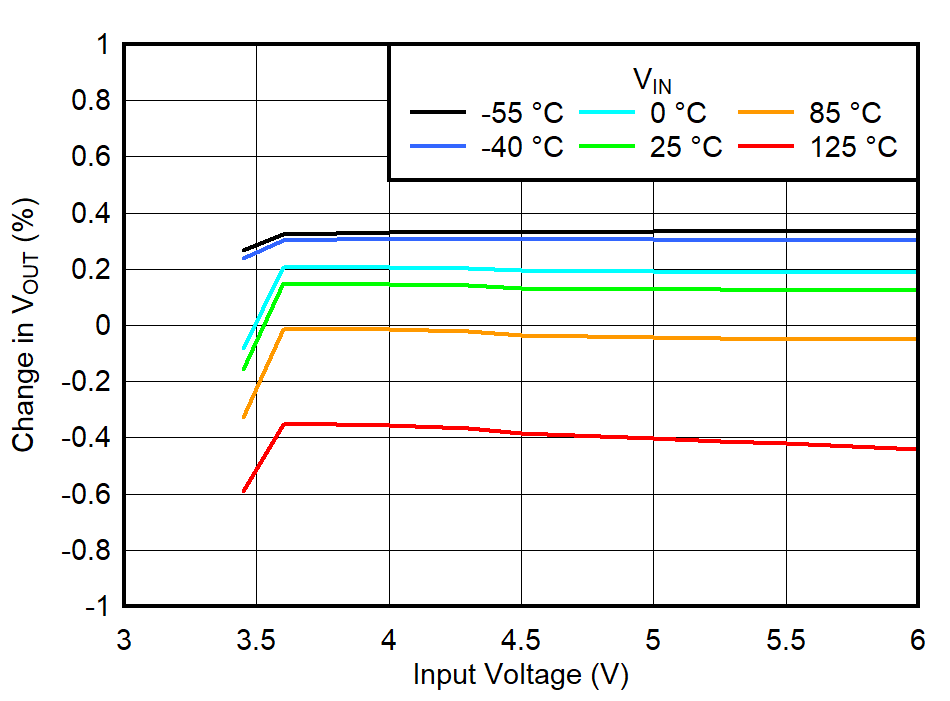

Figure 6-32 Dropout Voltage vs Input Voltage

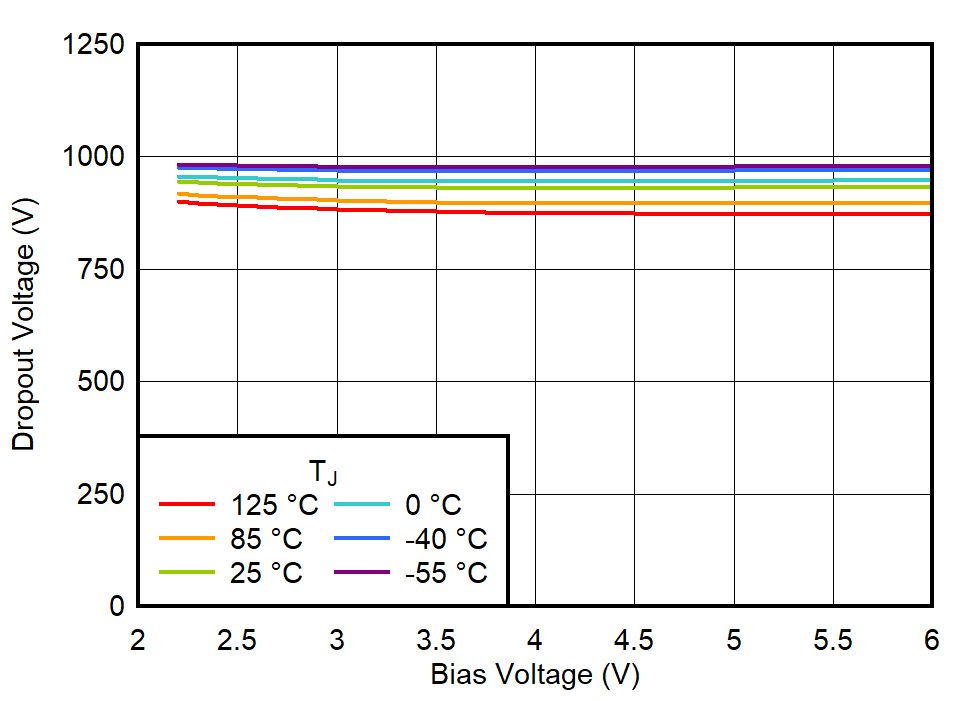

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = VIN, VEN =

1.1 V |

Figure 6-34 Dropout Voltage vs Bias Voltage for IOUT = 50 mA

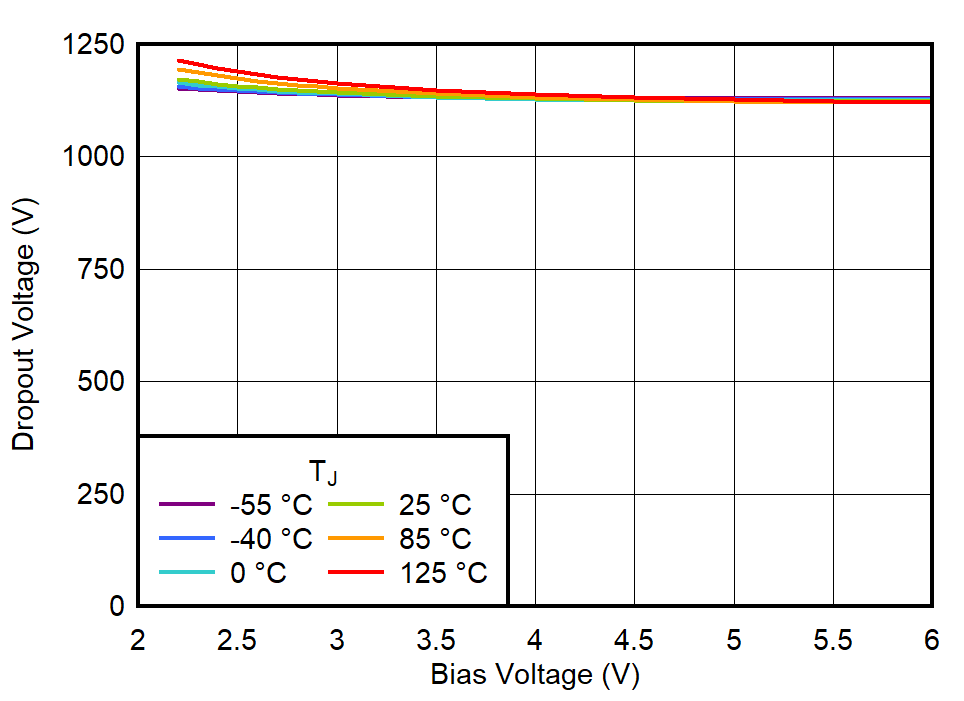

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = VIN, VEN =

1.1 V |

Figure 6-36 Dropout Voltage vs Bias Voltage for IOUT = 1.5 A

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 0.95 V, VEN = 1.1

V |

Figure 6-38 Current Limit vs Bias Voltage for VOUT = 0.65 V

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VEN = 0.4 V |

| |

Figure 6-40 Shutdown Current vs Bias Voltage for VIN = 0.95 V

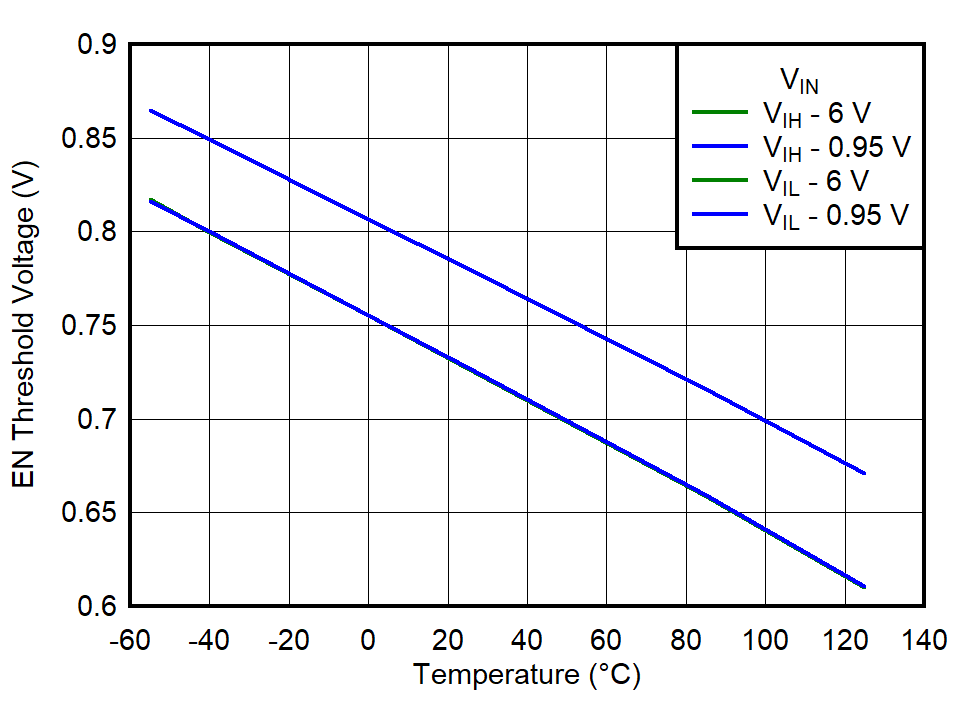

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

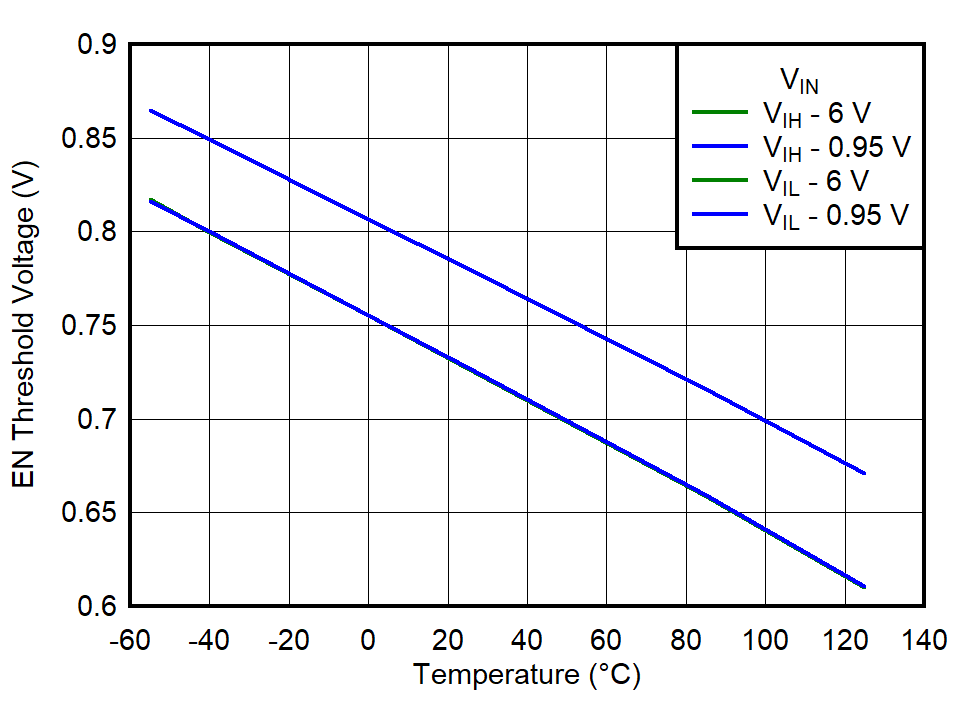

VBIAS = 6 V |

Figure 6-42 Enable Voltage Threshold vs Temperature

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V,

1.1 V ≤ VEN ≤ 6 V |

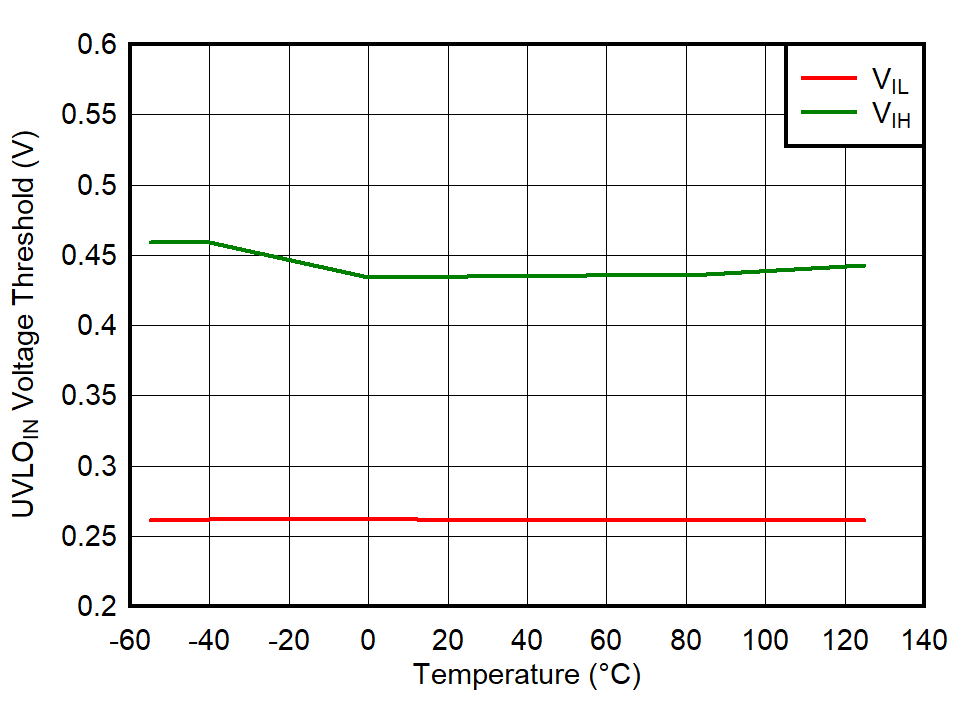

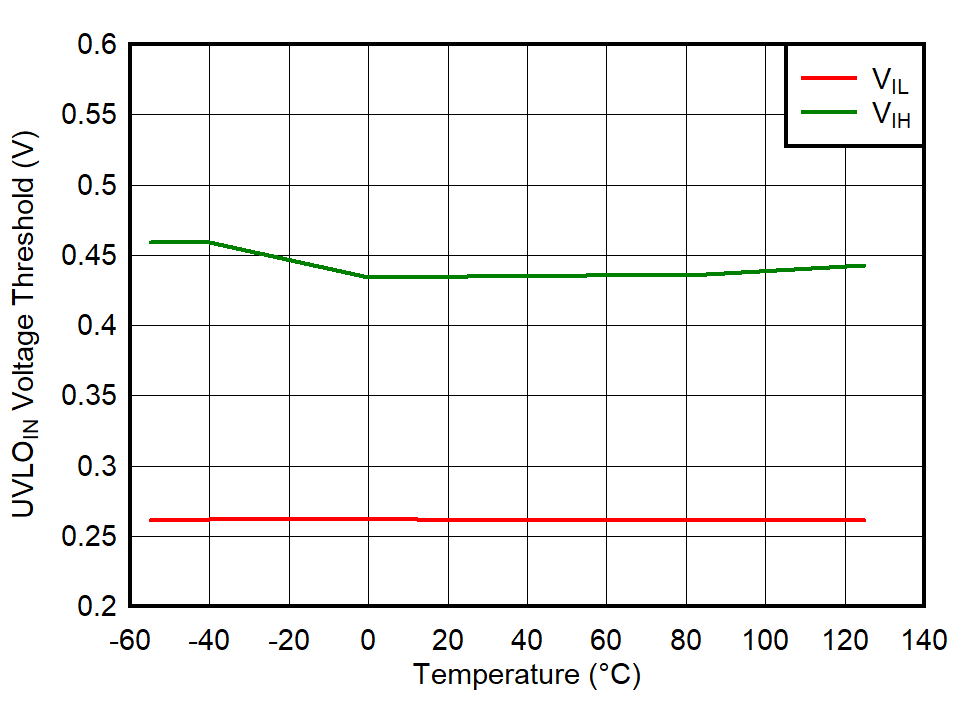

Figure 6-44 UVLOIN Voltage Threshold vs Temperature

CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 5 V,

1.1 V ≤ VEN ≤ 6 V |

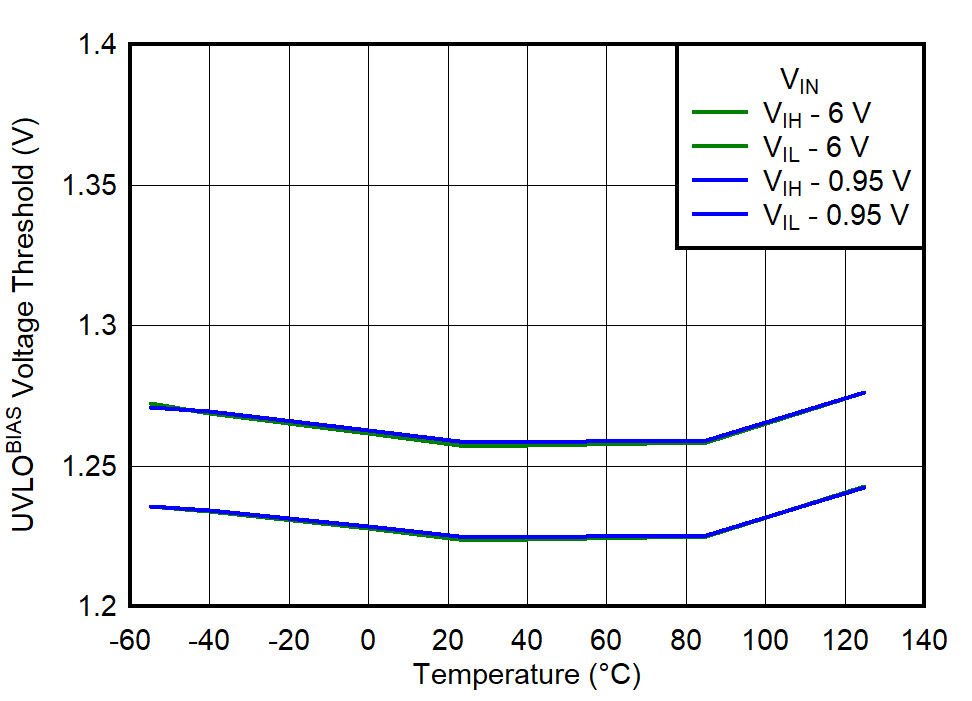

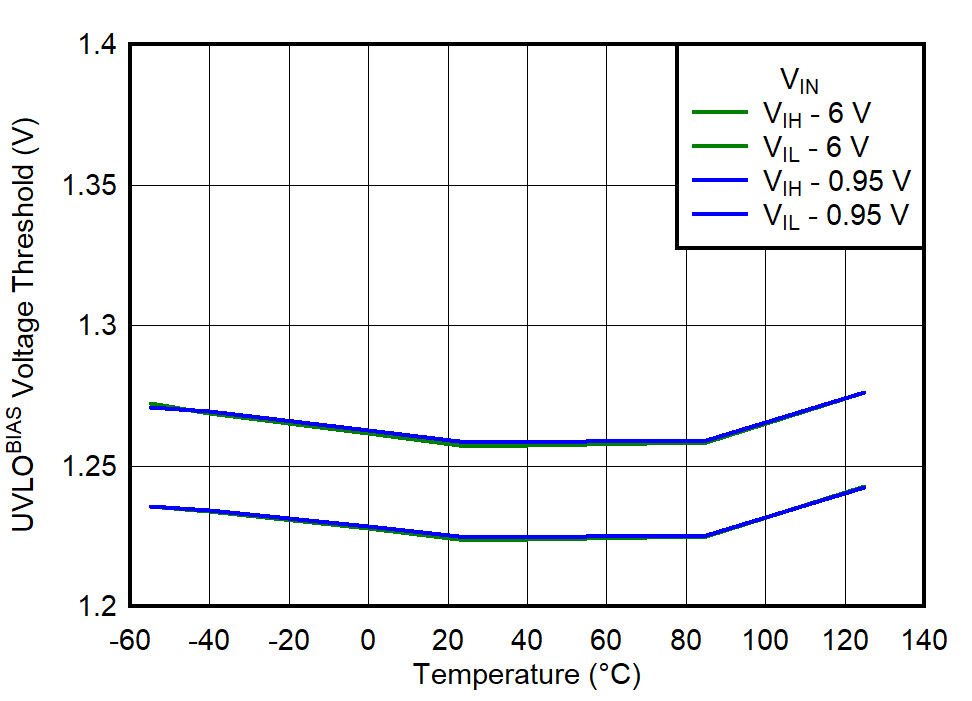

Figure 6-46 UVLOBIAS Voltage Threshold vs Temperature

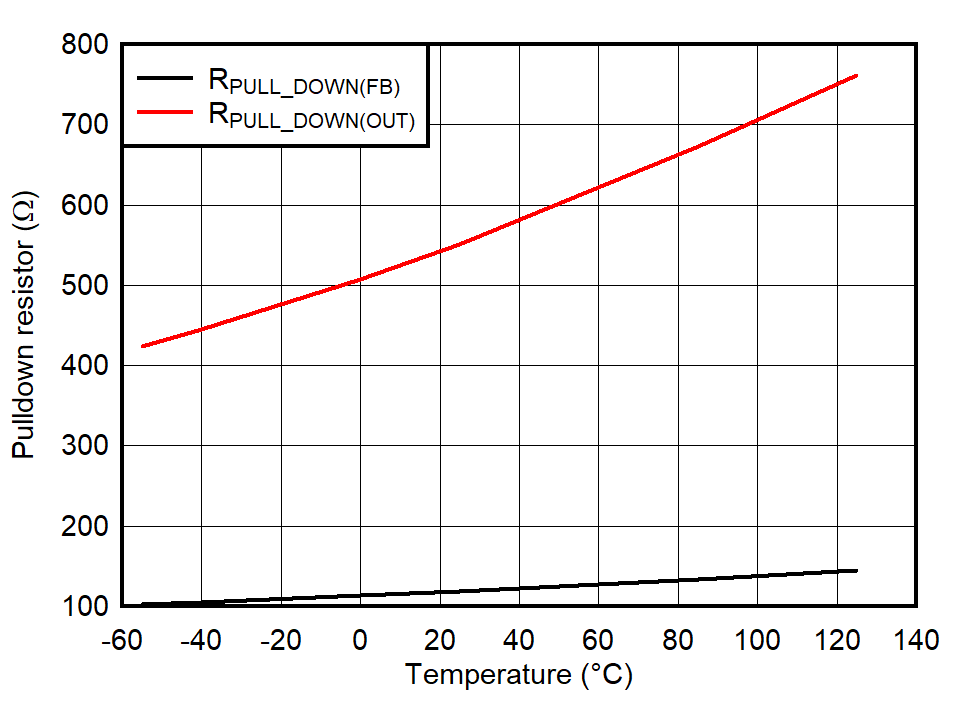

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VBIAS = 6 V, VEN ≤ 0.4

V |

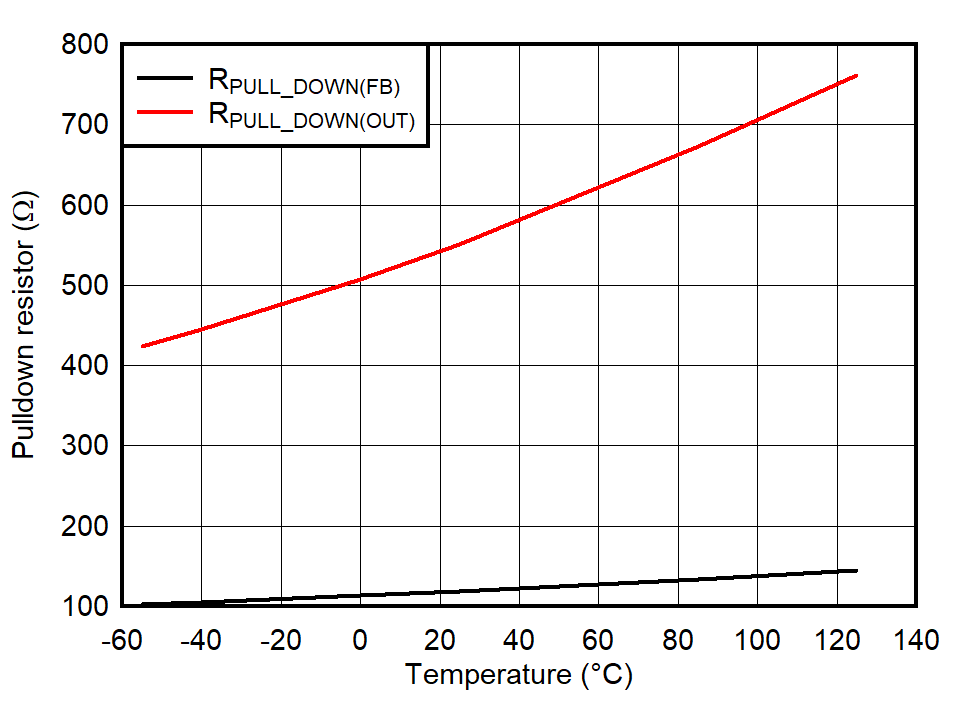

Figure 6-48 Pulldown Resistors vs Temperature

| CIN = COUT = 10 μF,

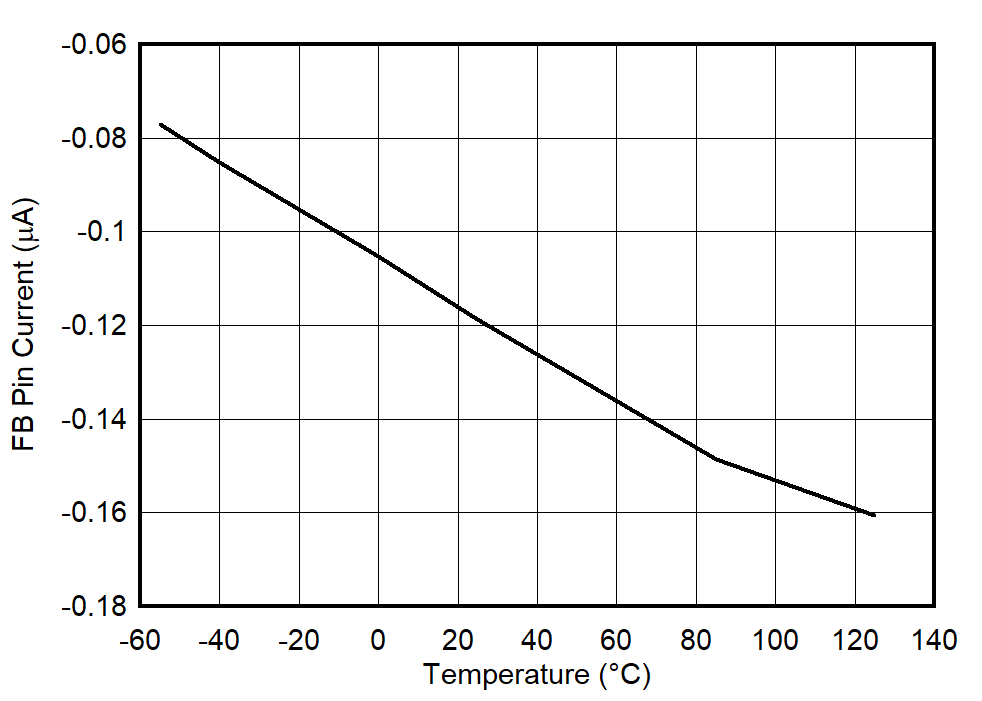

CBIAS = 1 μF, CSS = 0 nF, 0.95

V ≤ VIN ≤ 6 V, VOUT(NOM) = 0.65 V,

VBIAS = 6 V, IOUT = 2 mA,

VEN = 6 V |

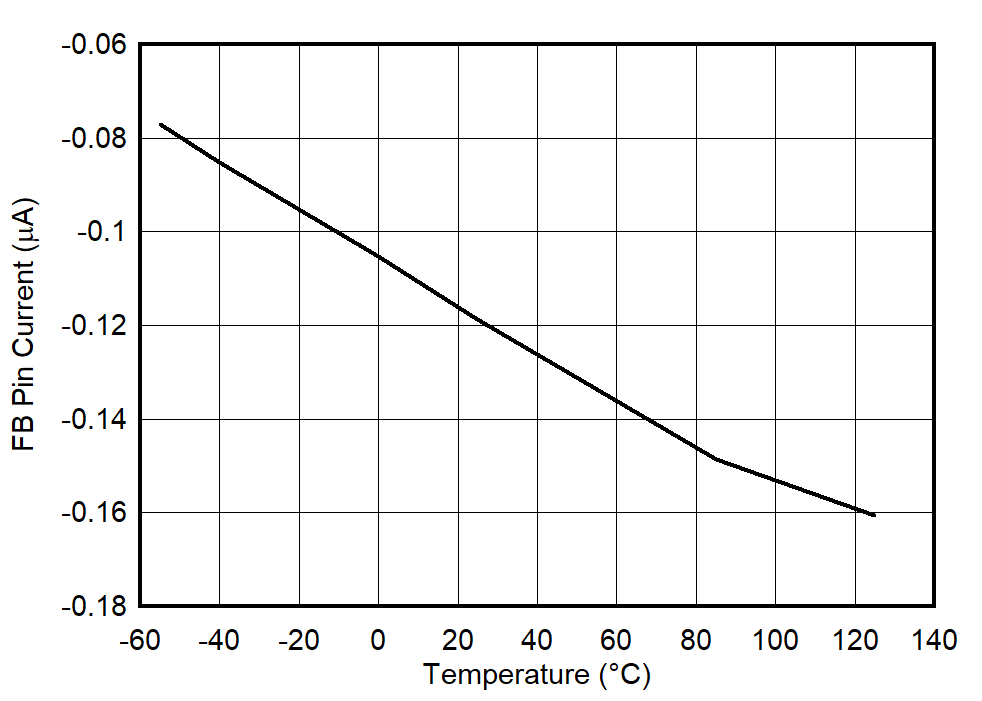

Figure 6-50 FB

Pin Current vs Temperature

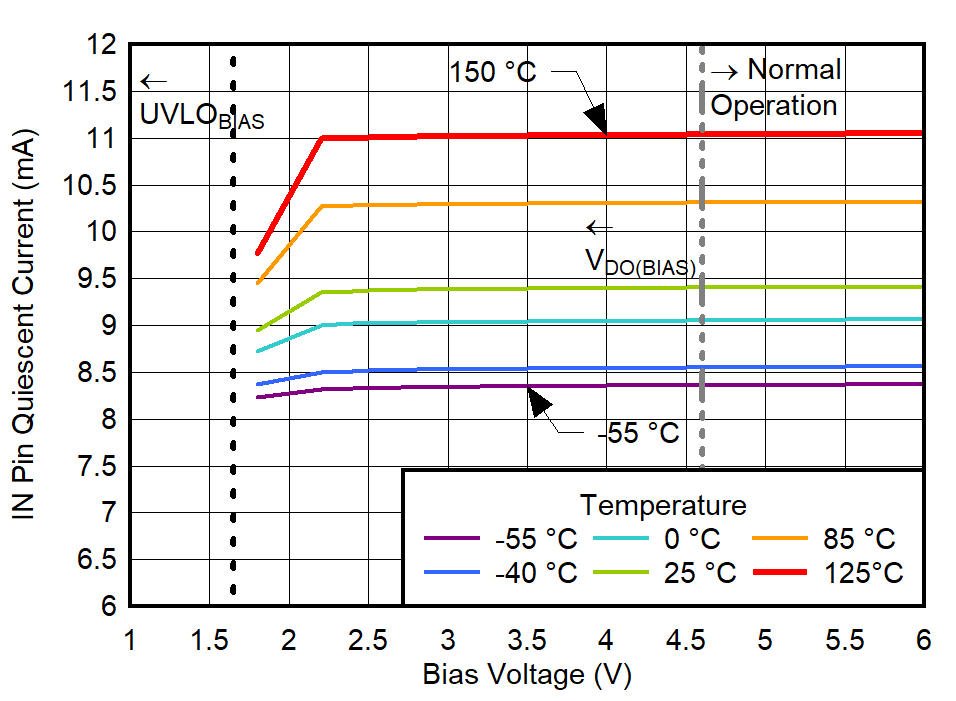

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VEN = 1.1 V |

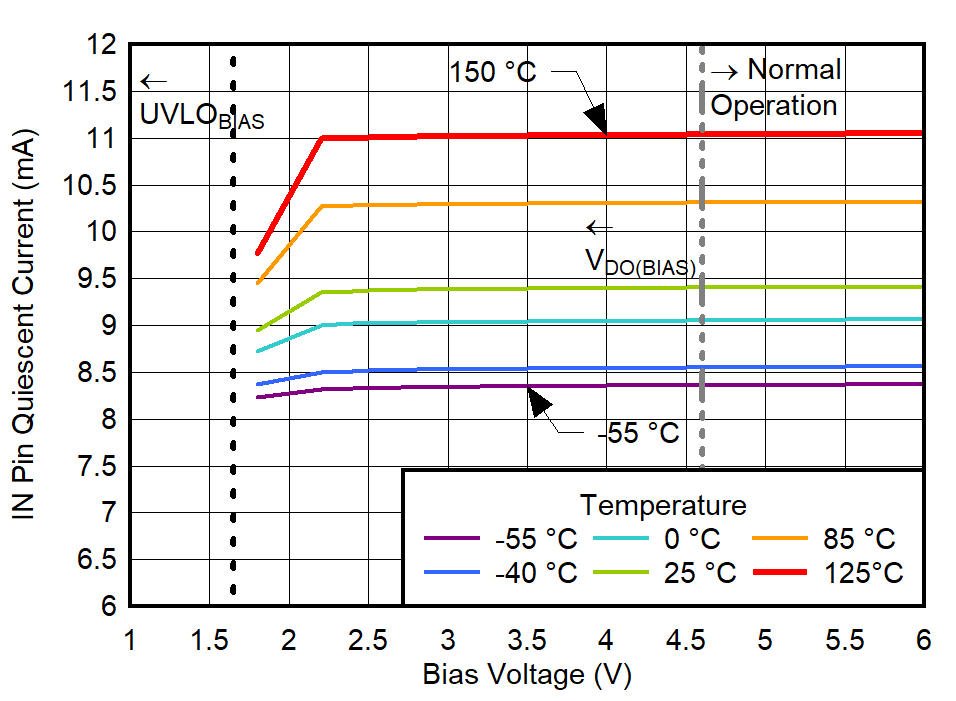

Figure 6-52 IN

Pin Quiescent Current vs Bias Voltage for

IOUT = 1.5 A

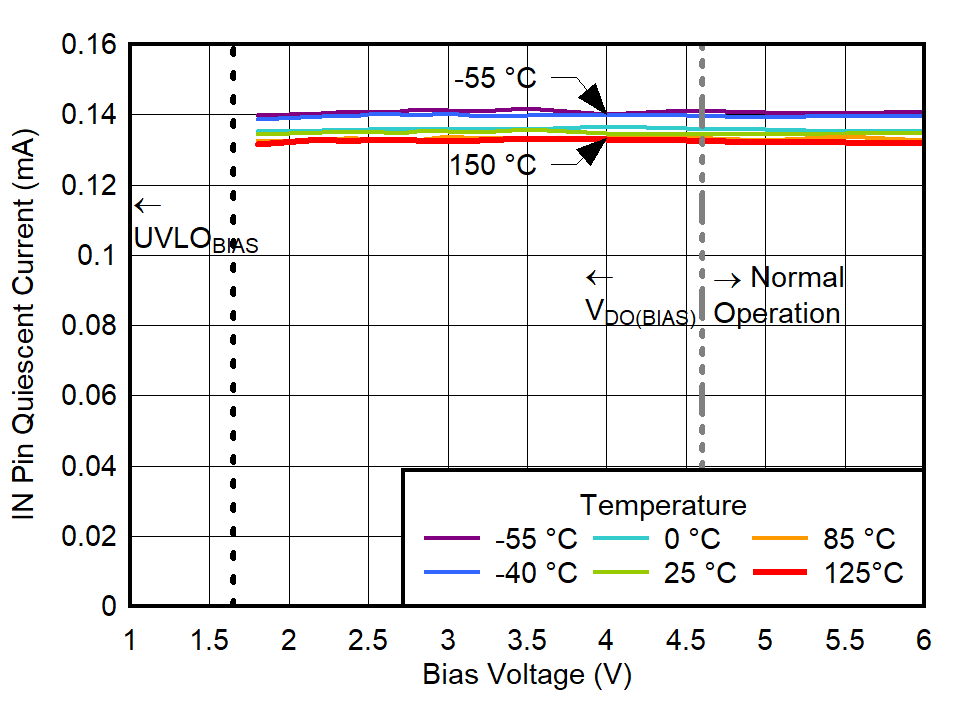

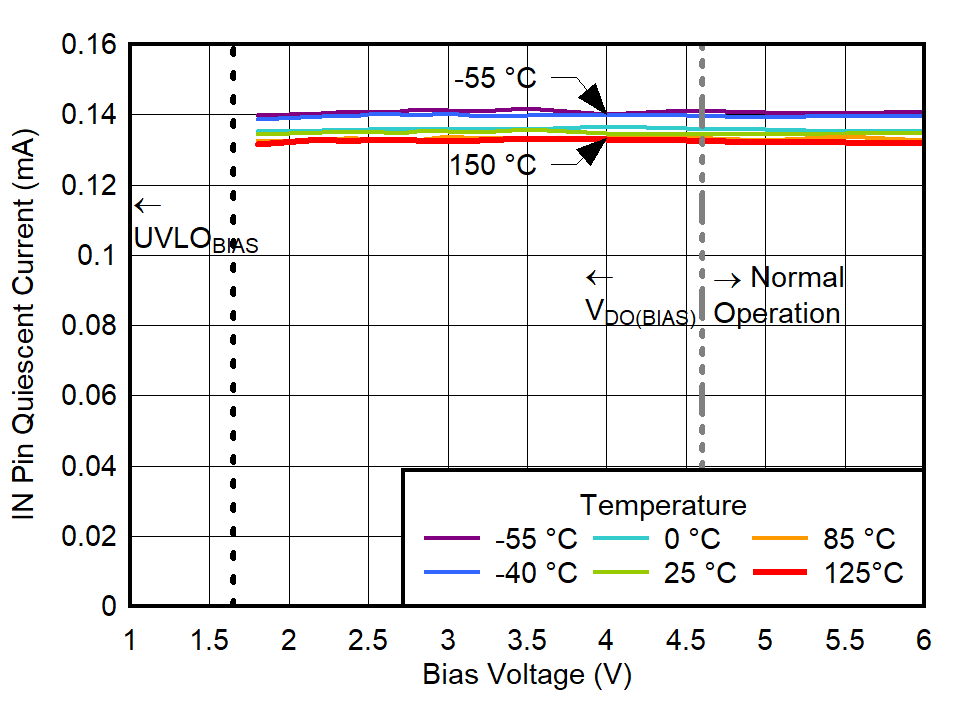

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VEN = 1.1 V |

Figure 6-54 IN

Pin Quiescent Current vs Bias Voltage for

IOUT = 10 mA

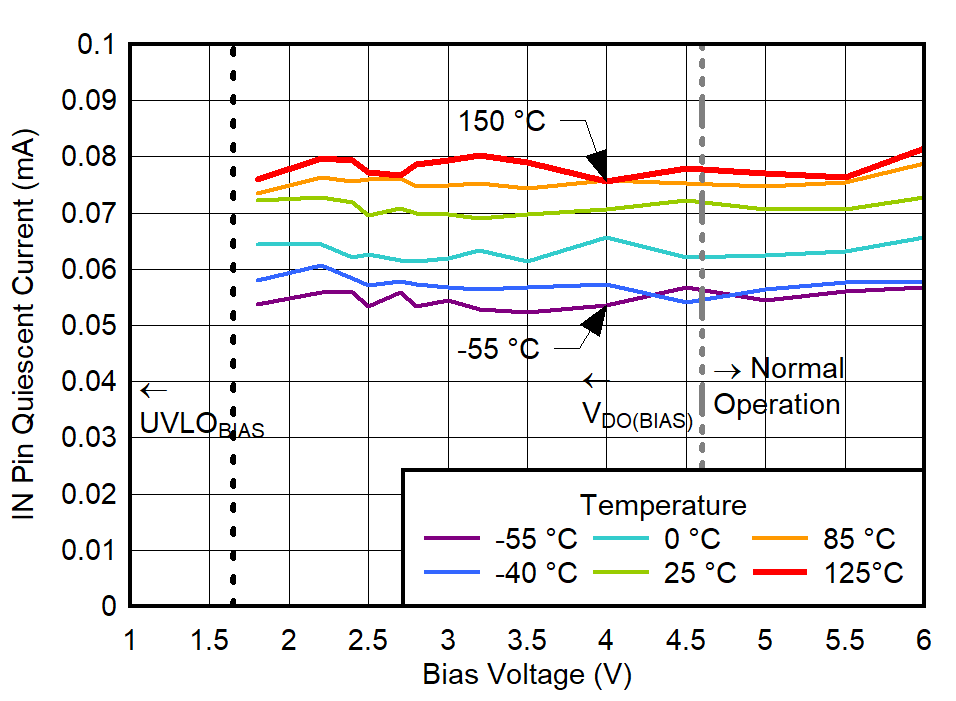

| CIN = COUT = 10 μF,

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VEN = 1.1 V |

Figure 6-56 IN

Pin Quiescent Current vs Bias Voltage for

IOUT = 0 A

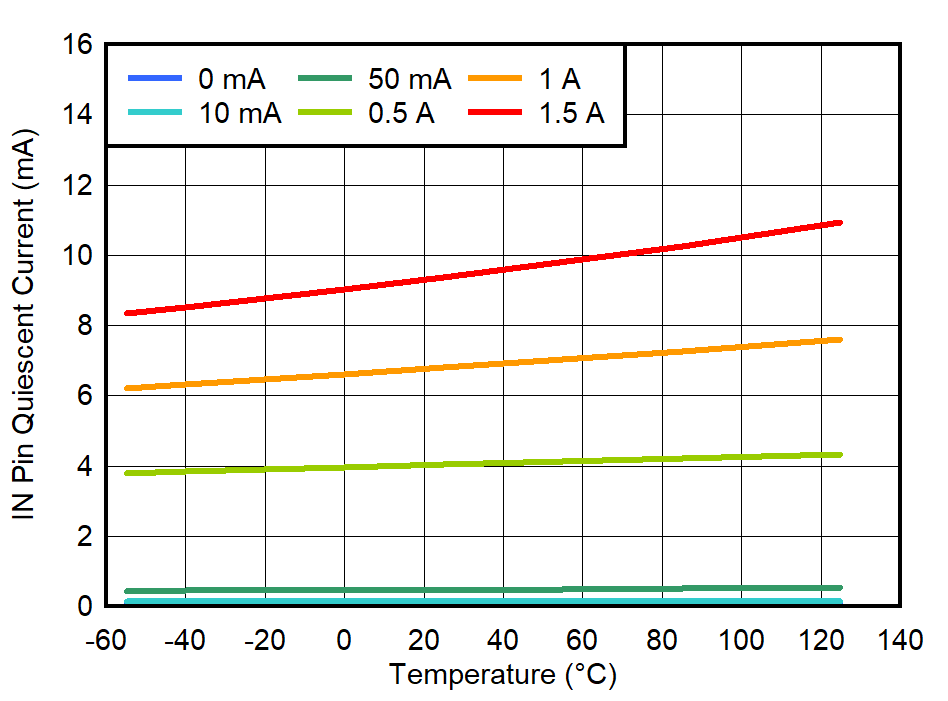

| CIN = COUT = 10 μF,

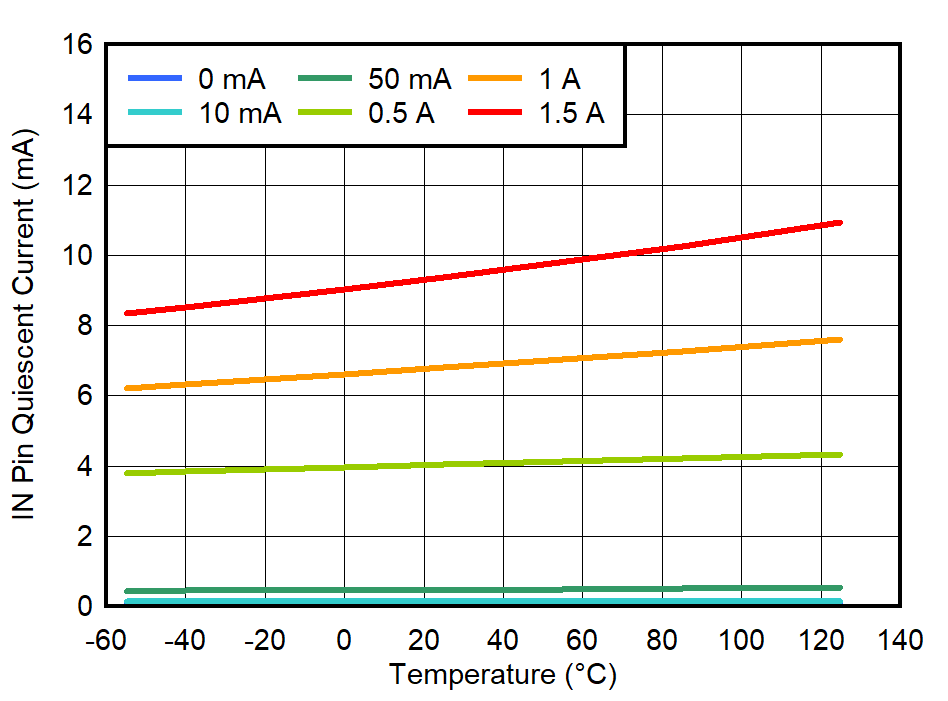

CBIAS = 1 μF, CSS = 0 nF,

VIN = 3.6 V, VOUT = 3.3 V,

VBIAS = 5 V, VEN = 1.1

V |

Figure 6-58 IN

Pin Quiescent Current vs Temperature