SCES651K June 2006 – October 2023 TXS0104E

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information: ZXU, YZT, and NMN

- 6.5 Thermal Information: D, PW, and RGY

- 6.6 Electrical Characteristics

- 6.7 Timing Requirements: VCCA = 1.8 V ± 0.15 V

- 6.8 Timing Requirements: VCCA = 2.5 V ± 0.2 V

- 6.9 Timing Requirements: VCCA = 3.3 V ± 0.3 V

- 6.10 Switching Characteristics: VCCA = 1.8 V ± 0.15 V

- 6.11 Switching Characteristics: VCCA = 2.5 V ± 0.2 V

- 6.12 Switching Characteristics: VCCA = 3.3 V ± 0.3 V

- 6.13 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

3 Description

This 4-bit non-inverting translator uses two separate configurable power-supply rails. The A port is designed to track VCCA. VCCA accepts any supply voltage from 1.65 V to 3.6 V. VCCA must be less than or equal to VCCB. The B port is designed to track VCCB. VCCB accepts any supply voltage from 2.3 V to 5.5 V. This allows for low-voltage bidirectional translation between any of the 1.8-V, 2.5-V, 3.3-V, and 5-V voltage nodes.

When the output-enable (OE) input is low, all outputs are placed in the high-impedance state.

The TXS0104E is designed so that the OE input circuit is supplied by VCCA.

For the high-impedance state during power up or power down, tie OE to GND through a pull-down resistor; the minimum value of the resistor is determined by the current-sourcing capability of the driver.

| PART NUMBER | PACKAGE(1) | PACKAGE SIZE(2) |

|---|---|---|

| TXS0104E | D (SOIC, 14) | 8.65 mm × 6 mm |

| PW (TSSOP, 14) | 5 mm × 6.4 mm | |

| ZXU (BGA, 12) | 2 mm × 2.5 mm | |

| RGY (VQFN, 14) | 3.5 mm × 3.5 mm | |

| YZT (DSBGA, 12) | 2.25 mm × 1.75 mm | |

| NMN (nFBGA, 12) | 2 mm × 2.5 mm | |

| BQA (WQFN, 12) | 3 mm × 2.5 mm | |

| RUT (UQFN, 12) | 2.00 mm × 1.70 mm |

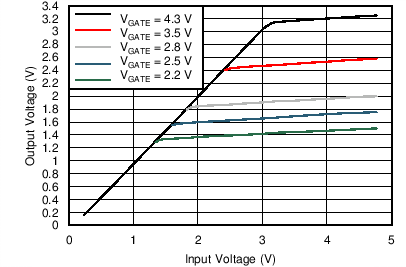

Transfer Characteristics of an

N-Channel Transistor

Transfer Characteristics of an

N-Channel Transistor