JAJSFA3B September 2012 – April 2018 CSD86360Q5D

PRODUCTION DATA.

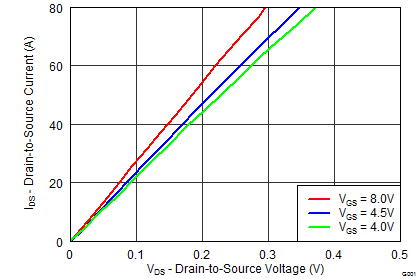

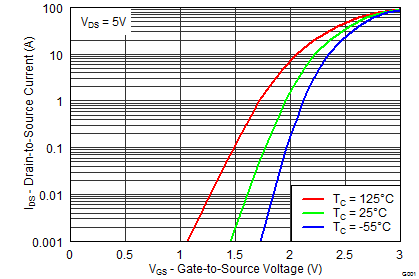

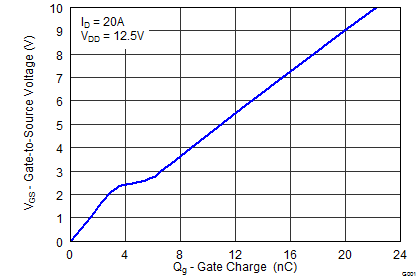

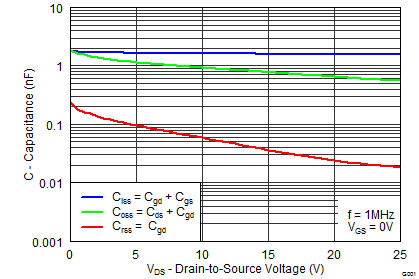

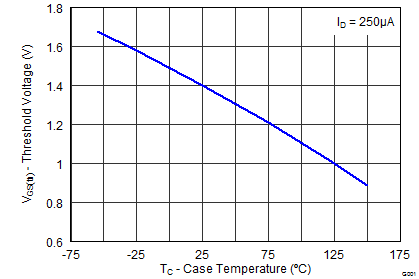

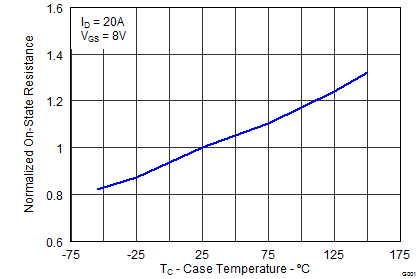

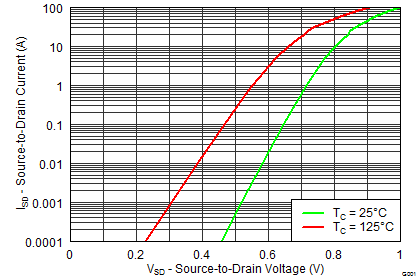

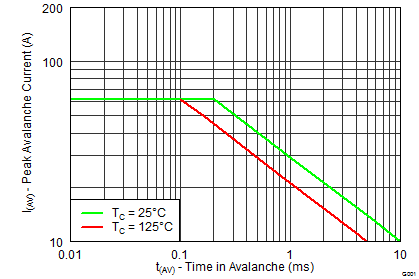

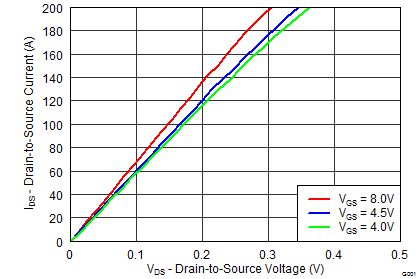

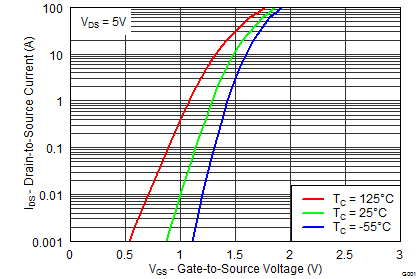

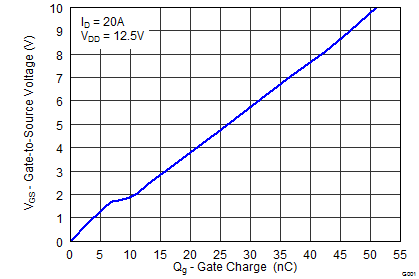

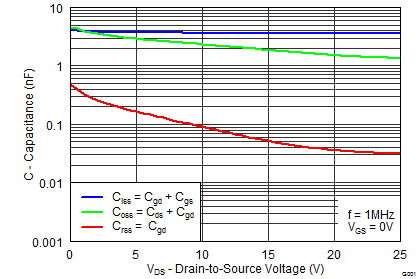

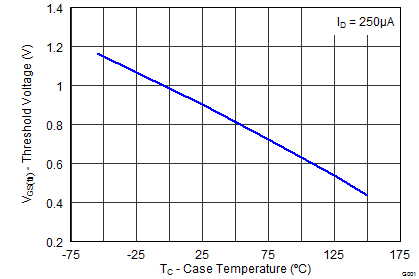

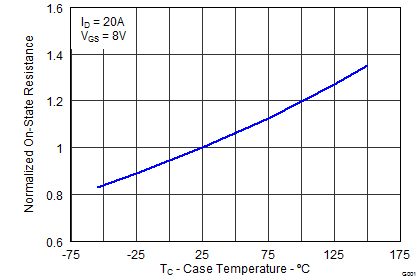

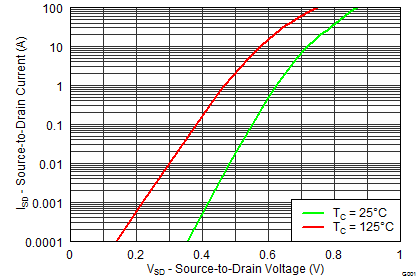

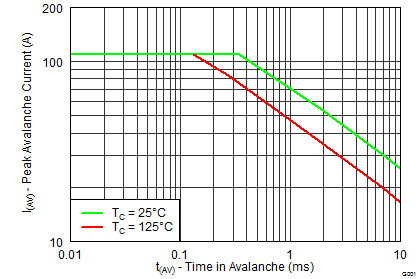

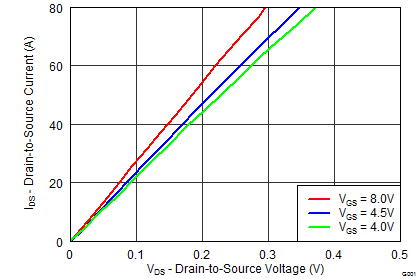

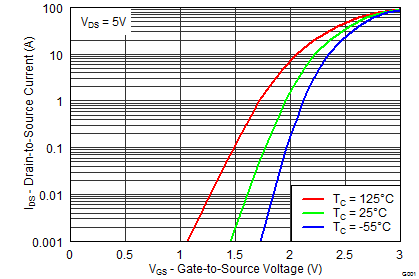

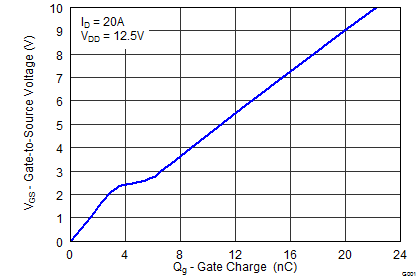

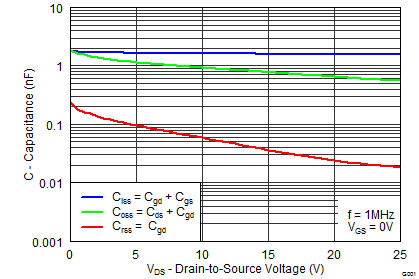

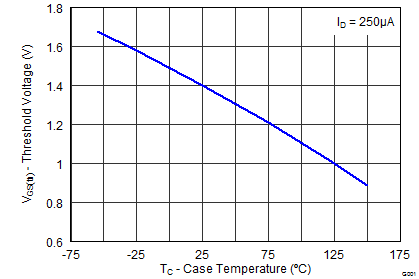

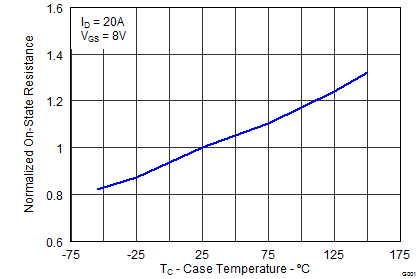

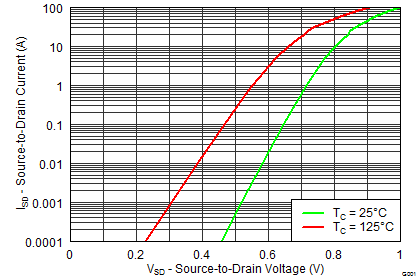

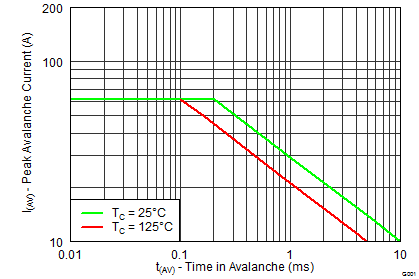

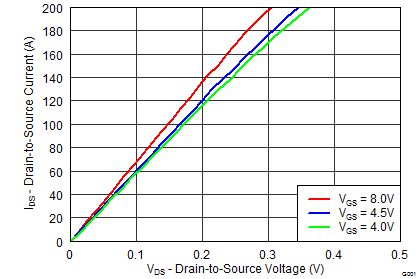

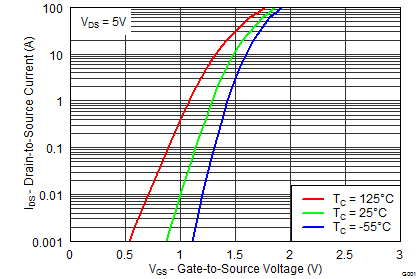

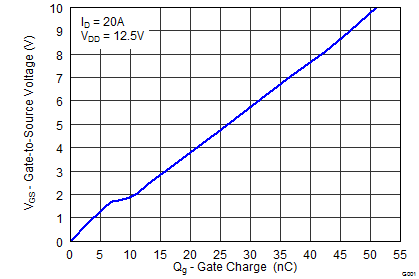

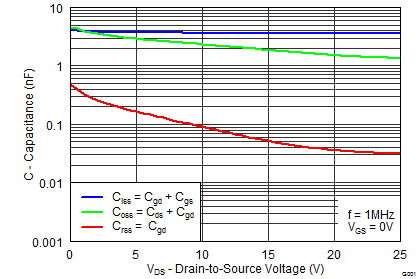

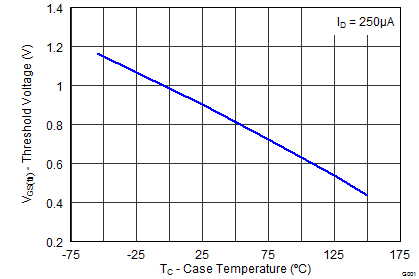

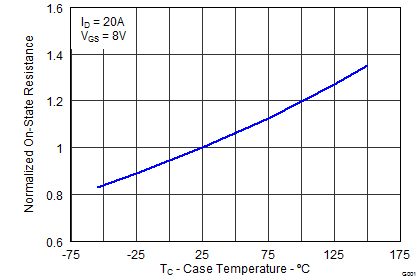

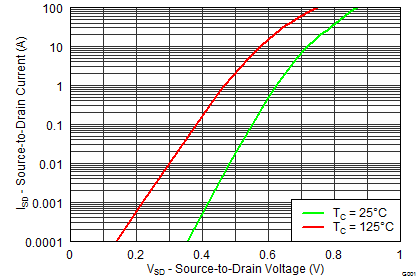

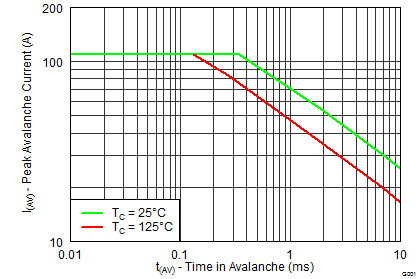

5.7 Typical Power Block MOSFET Characteristics

TA = 25°C, unless stated otherwise.

JAJSFA3B September 2012 – April 2018 CSD86360Q5D

PRODUCTION DATA.