JAJSEF1D December 2013 – December 2021 DAC7750 , DAC8750

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

8.4.4 Filtering The Current Output

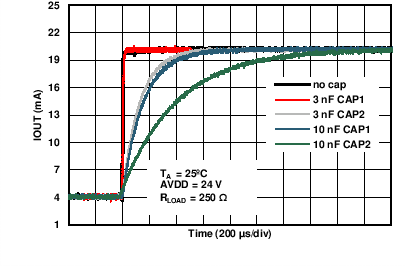

The DACx750 provides access to internal nodes of the circuit; see Figure 9-2. Place capacitors on these pins and AVDD to form a filter on the output current, reducing bandwidth and the slew rate of the output, especially useful for driving inductive loads. However, to achieve large reductions in slew rate, use the programmable slew rate to avoid having to use large capacitors. Even in that case, use the capacitors on CAP1 and CAP2 to smooth out the stairsteps caused by the digital code changes as shown in Figure 8-6. However, note that power supply ripple also couples into the devices through these capacitors.

Figure 8-6 IOUT vs Time for Different Cap Values on CAP1 and CAP2

Figure 8-6 IOUT vs Time for Different Cap Values on CAP1 and CAP2