JAJS814F August 2000 – February 2024 LMC6492 , LMC6494

PRODUCTION DATA

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|8

サーマルパッド・メカニカル・データ

発注情報

6.1.4 容量性負荷の許容誤差

すべてのレール ツー レール出力スイング オペアンプは、出力段で電圧ゲインを持っています。通常、この積分段には補償コンデンサが含まれます。ドミナント ポールの周波数の位置は、アンプの抵抗性負荷の影響を受けます。容量性負荷と並列に、適切な抵抗性負荷を使用することで、容量性負荷駆動能力を最適化できます (「代表的特性」を参照)。

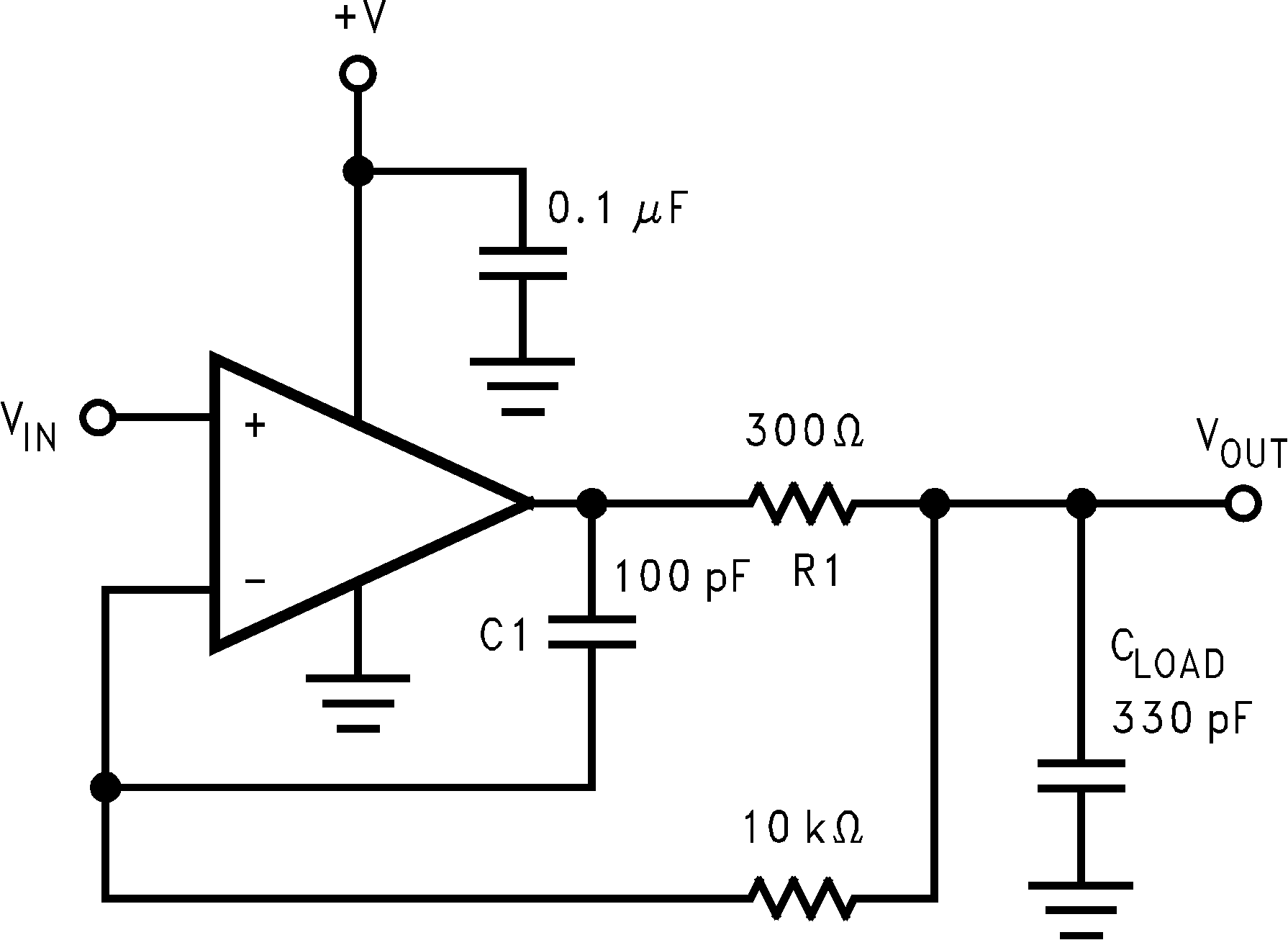

容量性負荷を直接接続すると、多くのアンプでは位相マージンが減少します。帰還ループの極は、オペアンプの出力インピーダンスと容量性負荷の組み合わせによって形成されます。図 6-6 に、LMC649x の開ループ出力インピーダンスを示します。この極は、アンプのユニティ ゲイン クロスオーバー周波数で位相遅れを引き起こし、結果的に、振動性と減衰不足のどちらかのパルス応答をもたらします。少数の外付け部品を使用することで、オペアンプは簡単に容量性負荷を間接的に駆動できます (図 6-7 を参照)。

図 6-6 LMC649x の開ループ出力インピーダンス

図 6-6 LMC649x の開ループ出力インピーダンス 図 6-7 LMC649x 非反転アンプ、容量性負荷を駆動するために補償済み

図 6-7 LMC649x 非反転アンプ、容量性負荷を駆動するために補償済み