JAJA708 September 2020 TPS55288 , TPS55288-Q1 , TPS552882 , TPS552882-Q1

2.3.1 クリティカル・ループの下にグランド・プレーンを追加する

クリティカル・ループ領域 A は、コンパクトな配置によって最小化できます。ただし、部品の物理サイズによっては、この方法が制限されます。EMI を低減するために最も重要な方法の 1 つは、スイッチング・ループの下にグランド・プレーンを追加することです。スイッチング・ループの下に層全体の GND 銅プレーンを配置すると、回路のパッシブ・シールドが確立されます。レンツの法則により、シールド層の電流によって生成される磁界は、元のスイッチ・ループの磁界を打ち消すように働きます。結果として磁束が減少し、等価ループ領域が小さくなり、EMI 性能が向上します。

グランド・プレーンを持つ多層 PCB では、特定のループにおけるインダクタンスの近似値はEquation3 で計算できます。

- μo=4π × 10-7

- h は、信号層とグランド・プレーンとの間にある絶縁の厚さです。

- Wg は、グランド・プレーンの幅です。

Equation3 から、グランド・プレーンの幅が広く面積が大きいほど、信号ループのインダクタンスが小さくなることがわかります。グランド・プレーンと信号ループとの間にある絶縁物が薄くなったときも、インダクタンスは小さくなります。

異なる PCB 基板上での、特定のループのインダクタンスを、表 2-1 に示します。4 層 PCB で、信号層とグランド・プレーンとの間にある絶縁物の厚さが 0.4mm の場合、配線のインダクタンスは厚さが 1.6mm の 2 層 PCB よりはるかに小さいことがわかります。したがって、ソリッドなグランド・プレーンを配置するときに、クリティカル・ループとの最小距離を保つことは、EMI を低減する最も効果的な方法の 1 つです。

|

PCB |

h (mm) |

Wg (mm) |

L (nH) |

|---|---|---|---|

|

2 層 PCB |

1.6 |

10 |

4.8 |

|

4 層 PCB |

0.4 |

10 |

1.2 |

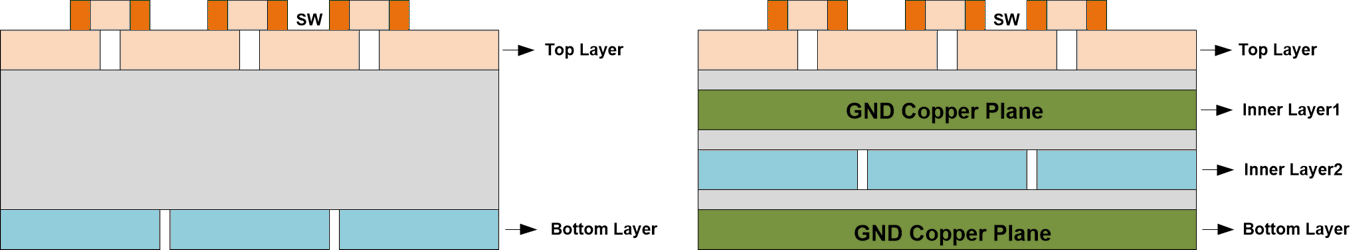

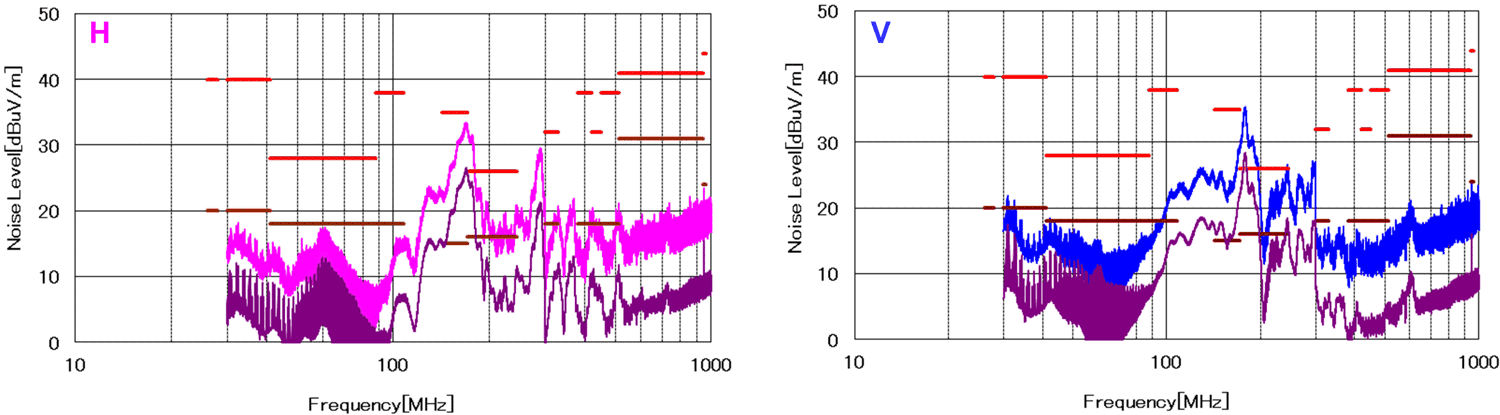

2 層 PCB と 4 層 PCB の断面図を、図 2-3に示します。2 層 PCB から放射される EMI の結果を、図 2-4 に示します。4 層 PCB から放射される EMI を、図 2-5 に示します。レイヤ・スタックと PCB の断面図は、図 2-4 のものとほぼ同じです。同じ部品の配置と同じテスト条件において、4 層 PCB では放射 EMI を 15dBμV/m 以上改善できます。

図 2-3 2 層基板と 4 層基板の断面図

図 2-3 2 層基板と 4 層基板の断面図 図 2-4 2 層 PCB の放射 EMI の結果

図 2-4 2 層 PCB の放射 EMI の結果 図 2-5 4 層 PCB の放射 EMI の結果

図 2-5 4 層 PCB の放射 EMI の結果