JAJSGJ4D August 2018 – April 2021 UCC21530-Q1

PRODUCTION DATA

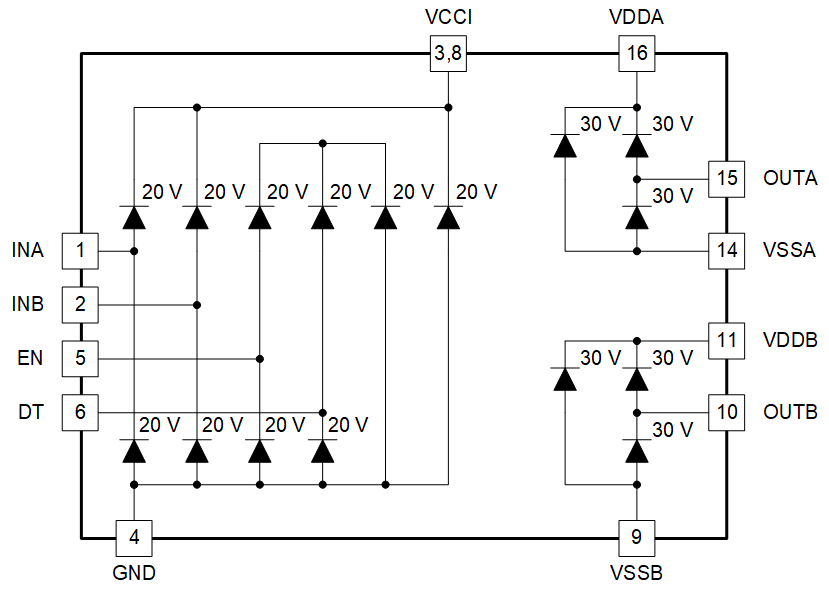

8.3.5 UCC21530-Q1 のダイオード構造

UCC21530-Q1 のESD 保護素子に関連する複数のダイオードを、図 8-3 に示します。これは、本デバイスの絶対最大定格を図で表したものです。

図 8-3 ESD 構造

図 8-3 ESD 構造JAJSGJ4D August 2018 – April 2021 UCC21530-Q1

PRODUCTION DATA

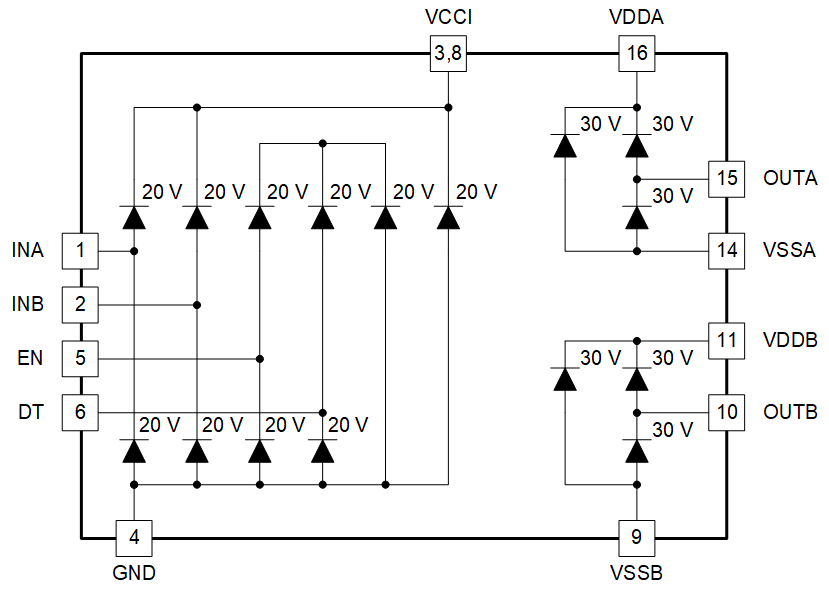

UCC21530-Q1 のESD 保護素子に関連する複数のダイオードを、図 8-3 に示します。これは、本デバイスの絶対最大定格を図で表したものです。

図 8-3 ESD 構造

図 8-3 ESD 構造