JAJSGJ4D August 2018 – April 2021 UCC21530-Q1

PRODUCTION DATA

3 概要

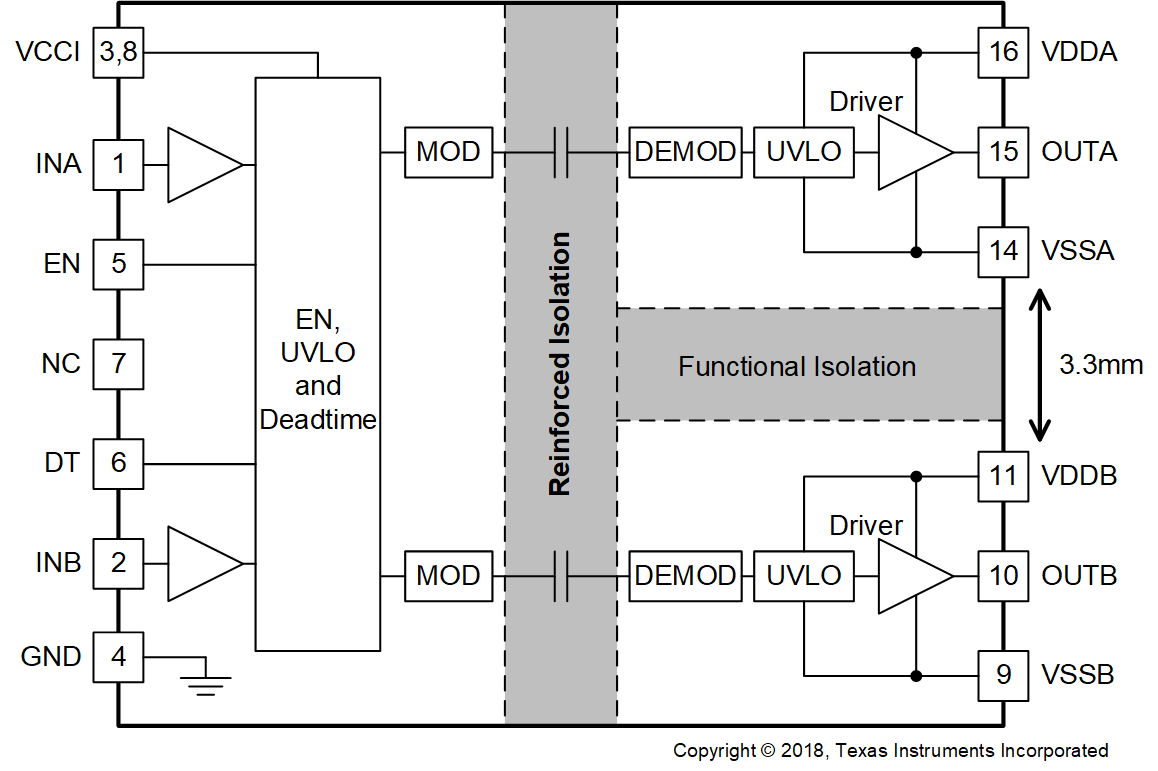

UCC21530-Q1 は絶縁されたデュアル・チャネルのゲート・ドライバで、ピーク電流はソース 4A、シンク 6A です。IGBT、Si MOSFET、SiC MOSFET を最高 5MHz で駆動し、クラス最高の伝搬遅延とパルス幅歪みを実現するよう設計されています。

入力側は 5.7kVRMS の強化絶縁バリアによって 2 つの出力ドライバと分離され、同相過渡耐性 (CMTI) は最小で 100V/ns です。2 つの 2 次側ドライバ間は、内部的に機能絶縁されているため、1850V までの電圧で動作します。

このドライバは 2 つのローサイド・ドライバ、2 つのハイサイド・ドライバ、またはデッド・タイム (DT) をプログラム可能な 1 つのハーフブリッジ・ドライバとして構成可能です。EN ピンが Low にプルされると、両方の出力が同時にシャットダウンされ、オープンまたは High にプルされているときは通常動作します。フェイルセーフ手法として、1 次側のロジック障害が発生すると、両方の出力が強制的に Low になります。

このデバイスは、25V までの VDD 電源電圧を受け付けます。VCCI 入力電圧範囲が 3V~18V と広いため、このドライバはアナログ / デジタルいずれのコントローラとの接続にも適しています。すべての電源電圧ピンには、低電圧誤動作防止 (UVLO) 保護機能が搭載されています。

製品情報(1)

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| UCC21530-Q1 | DWK SOIC (14) | 10.30mm × 7.50mm |

| UCC21530B-Q1 | DWK SOIC (14) | 10.30mm × 7.50mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

機能ブロック図

機能ブロック図