JAJU847B april 2021 – april 2023

3.3.3.4 サージ・テスト

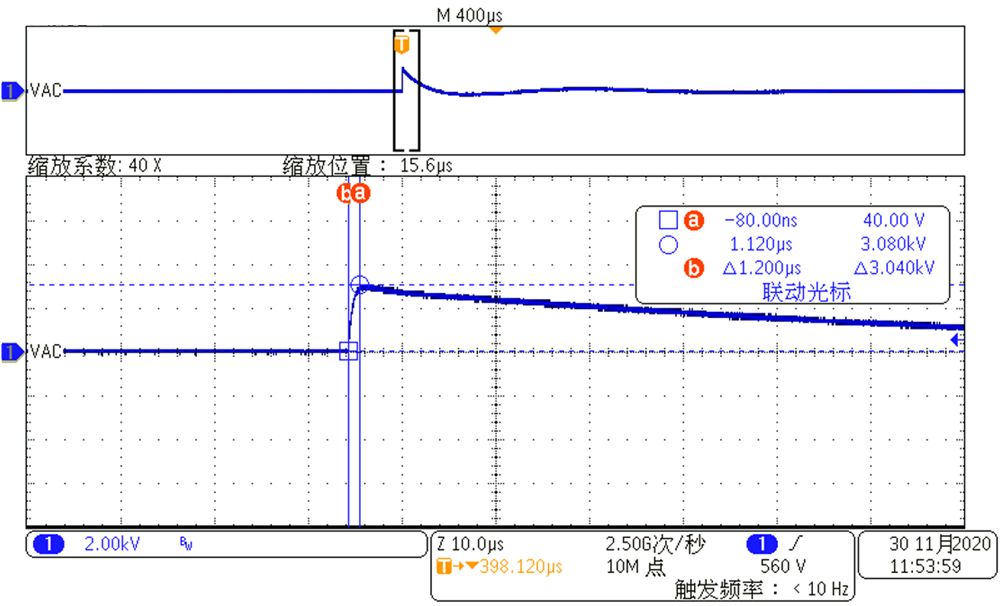

この設計では、ACL と ACN の間の雷サージ・テストを実施しました。図 3-14 に、EUT が接続されていないときの 3kV ライン対中性点サージ電圧波形を示します。

図 3-14 サージ電圧波形

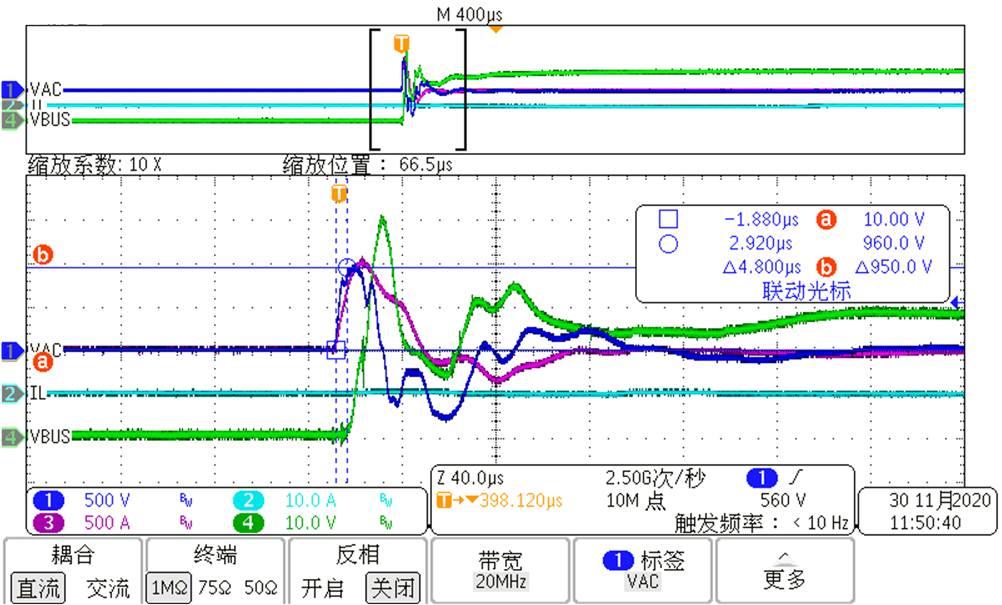

このサージ波形を使用して、入力電流と PFC チョーク電流 (GaN FET を流れる電流と同じ) をテストしました。結果は、サージ電流が突入ダイオードによって完全にバイパスされ、GaN FET にはリスクがないことを示しています (図 3-15 を参照)。

図 3-15 GaN FET、サージ・テストでのチョーク電流

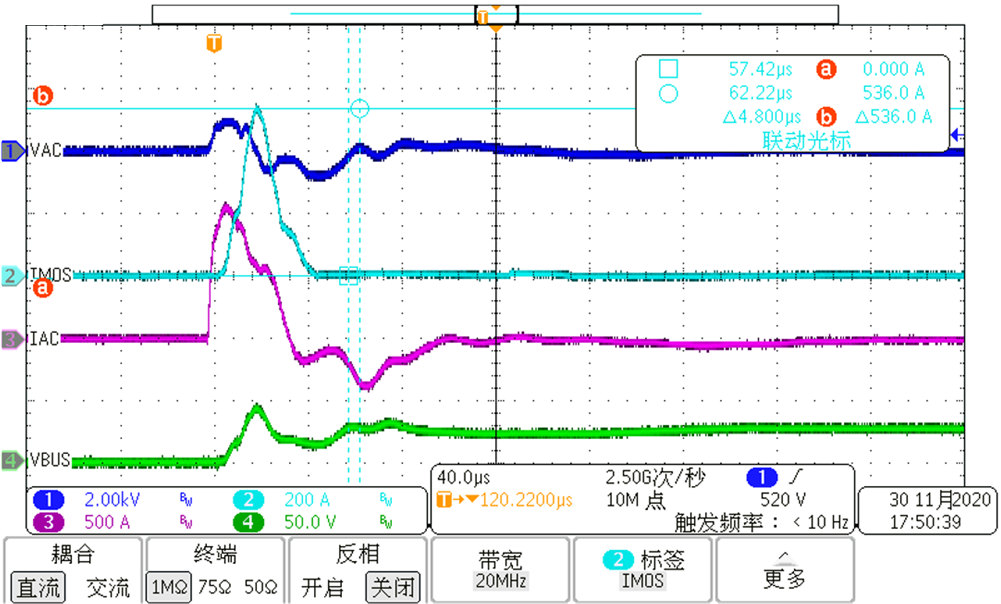

MOSFET を流れるサージ電流は脅威になります。図 3-16 に示すテスト波形では、3kV サージ下の電流が MOSFET の最大ピーク電流仕様を超えています。

図 3-16 MOSFET を流れるサージ電流

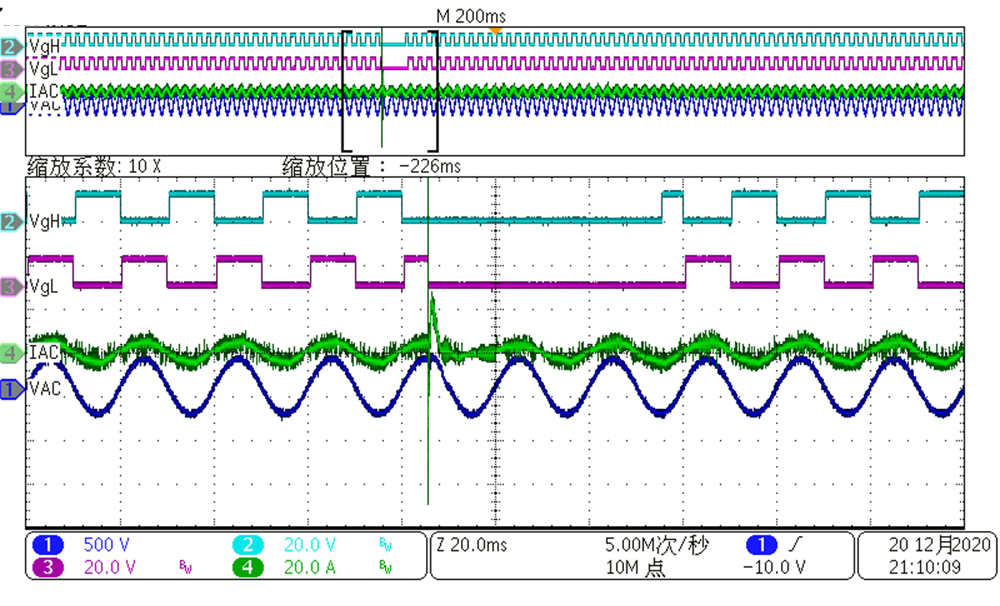

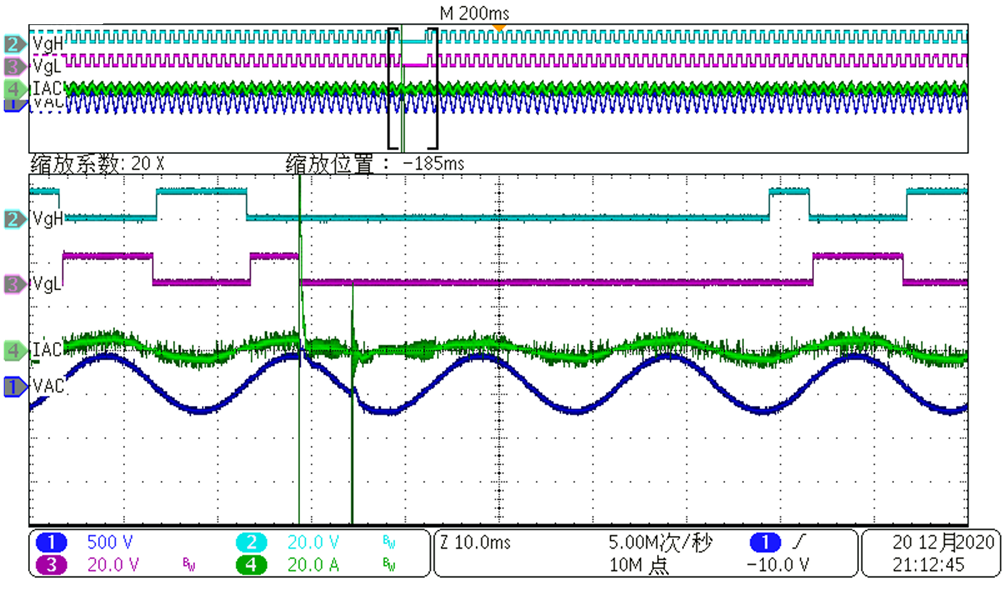

実験は、電力段は ±3kV のサージに耐えられますが、MOSFET レッグは -4kV のサージで破損することを示しています。図 3-17 および図 3-18 に、±3kV のサージ波形を示します。

図 3-17 +3kV、90 度でのサージ・テスト

図 3-18 -3kV、90 度でのサージ・テスト