JAJU849A september 2022 – may 2023

3.3.2 インターフェイス・ウェークアップ電圧 (TCM_PHYL_INTF_IQWUF および TCM_PHYL_INTF_IQWUHL)

次のテストでは、ウェークアップ・パルスの生成中の IO-Link CQライン・ドライバ段の動作を検証します。CQ 出力に抵抗性負荷がかけられ 500mA の電流が発生し、電圧レベルが観測されます。最初の 2 つのテストは、ハイサイド・ドライバを検証します。

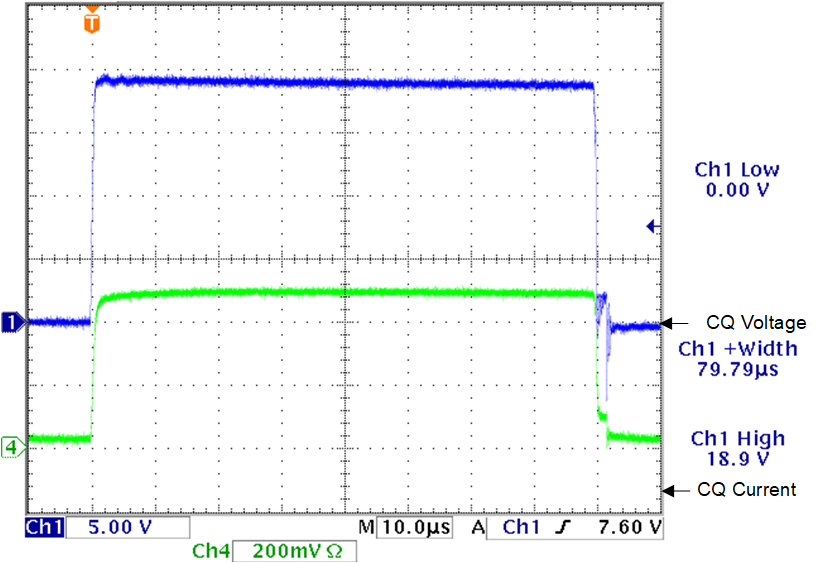

図 3-3 20V の TCM_PHYL_INTF_IQWUH

図 3-3 20V の TCM_PHYL_INTF_IQWUH図 3-3 に初回のテストを示します。ここでは、電源電圧を 20V に設定し、ラインに 40Ω の負荷をかけて 500mA の電流を発生させます。電圧レベルが、13V の VTHHHmax を超えている場合に観測されます。スコープ・プロットは 18.9V の測定値を示しているため、このテストに合格しています。

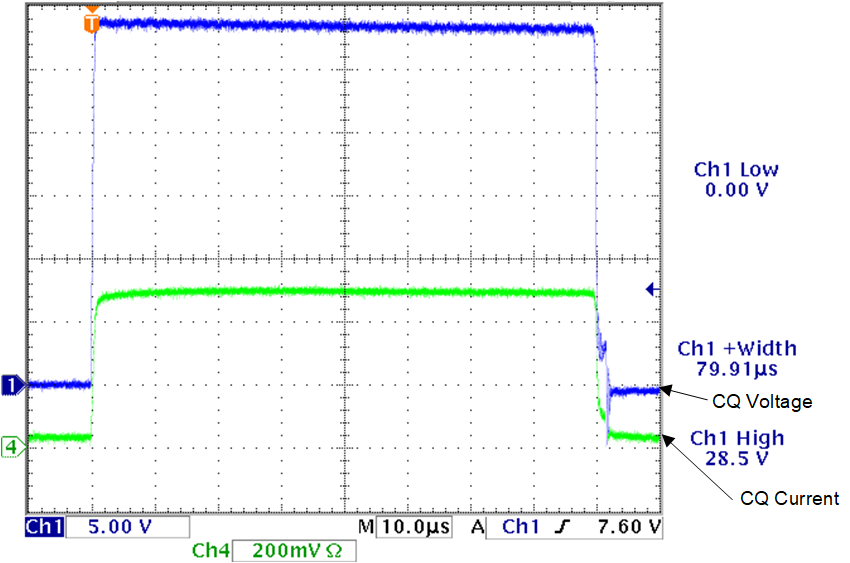

図 3-4 30 V の TCM_PHYL_INTF_IQWUH

図 3-4 30 V の TCM_PHYL_INTF_IQWUH30V の電源電圧で同様の測定を行う必要があります。図 3-4 のスコープ・プロットは、これを示しています。この場合、抵抗性負荷を 60Ω に変更する必要があるため、結果として得られる電流は引き続き 500mA になります。28.5V の電圧を測定したので、このテストにも合格しました。

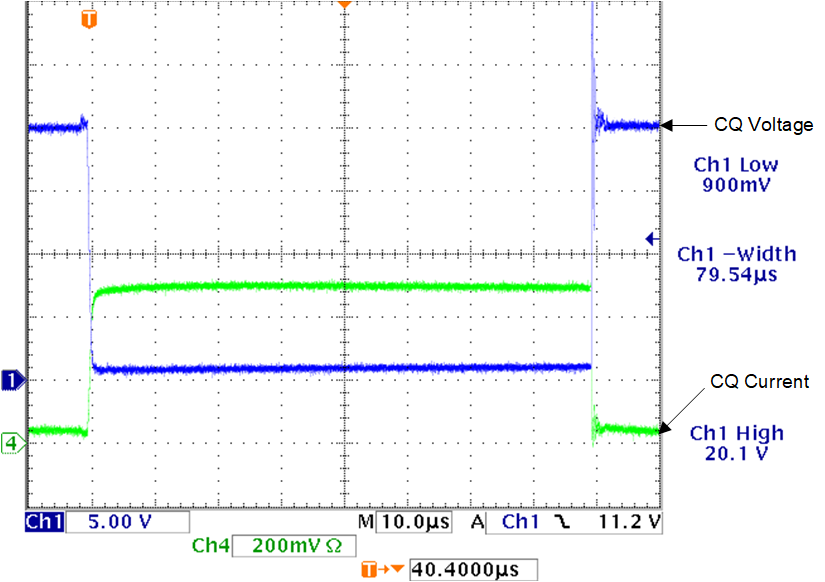

図 3-5 20V の TCM_PHYL_INTF_IQWUL

図 3-5 20V の TCM_PHYL_INTF_IQWULローサイド・ドライバに対しても同じテストを実施します。図 3-5 に、電源電圧 20V での最初のテストを示します。この場合も、抵抗性負荷を使用してラインに負荷をかける必要があり、その結果、500mA になります。この場合、負荷は L+ に接続されます。図に示すように、0.9V の電圧が測定されます。これでこのテストは合格です。

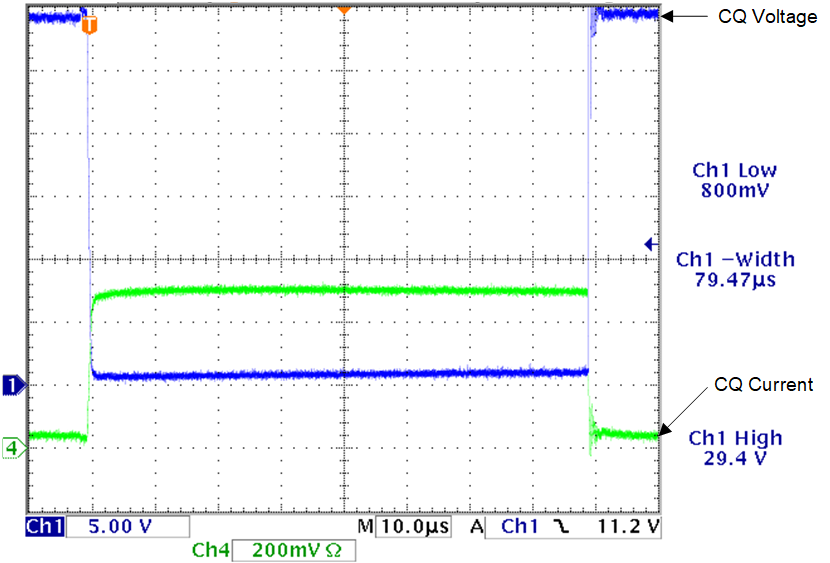

図 3-6 30V の TCM_PHYL_INTF_IQWUL

図 3-6 30V の TCM_PHYL_INTF_IQWUL最後の物理層テストは類似していますが、30V で、負荷抵抗も同様に高くなっています。図 3-6 の結果は、再び 0.9V の電圧を示しています。これも合格です。

表 3-1 に、すべての物理層テストの概要と結果を示します。

| ID | 名称 | 構成 | 仕様 (条項) | コメント | 結果 |

|---|---|---|---|---|---|

| SDCI_TC_0001 | TCM_PHYL_INTF_ISM | マスタ・ポートの供給電流が監視されます。 | 『IO-Link インターフェイスおよびシステム仕様書 V1.1.3』4のセクション 5.3.2.3、表 6 を参照してください | 500mA でテスト | 20V:合格 30V:合格 |

| SDCI_TC_0002 | TCM_PHYL_INTF_ISIRM | マスタ・ポートの供給電流が監視されます。 | 500mA でテスト | 20V:合格 30V:合格 |

|

| SDCI_TC_0003 | TCM_PHYL_INTF_ILLM | マスタ・ポートの C/Q での入力電流が監視されます。 | ILLM (VIM = 5V、VSM = 20V):8.56mA 合格 ILLM (VIM = 5.1V、VSM = 20V):8.56mA 合格 ILLM (VIM = 15V、VSM = 20V):8.57mA 合格 ILLM (VIM = VSM = 20V):8.57mA 合格 ILLM (VIM = 5V、VSM = 30V):8.57mA 合格 ILLM (VIM = 5.1V、VSM = 30V):8.57mA 合格 ILLM (VIM = 15V、VSM = 30V):8.58mA 合格 ILLM (VIM = VSM = 30V):8.59mA 合格 |

||

| SDCI_TC_0004 | TCM_PHYL_INTF_VREShigh | マスタ C/Q 出力の出力レベルを測定します。 | VRQHM (VSM = 20V):0.23V VRQHM (VSM = 30V):0.228V 合格 |

||

| SDCI_TC_0005 | TCM_PHYL_INTF_VRESLOW | マスタ C/Q 出力の出力レベルを測定します。 | VRQLM (VSM = 20V):0.225V VRQLM (VSM = 30V):0.225V 合格 |

||

| SDCI_TC_0006 | TCM_PHYL_INTF_VTHHM | C/Q 入力のデジタル入力信号が監視されます | 『IO-Link インターフェイスおよびシステム仕様書 V1.1.3』4のセクション 5.3.2.2、表 5 を参照してください | VIM@VTHHM (VSM = 20V):11.1V VIM@VTHHM (VSM = 30V):11.1V 合格 |

|

| SDCI_TC_0007 | TCM_PHYL_INTF_VTHLM | C/Q 入力のデジタル入力信号が監視されます | VIM@VTHLM (VSM = 20V):10.35V VIM@VTHLM (VSM = 30V):10.35V 合格 |

||

| SDCI_TC_0008 | TCM_PHYL_INTF_VHYSM | SDCI_TC_0006 と SDCI_TC_0007 の値の比較 | VHYSM (VSM = 20V):0.75V VHYSM (VSM = 30V):0.75V 合格 |

||

| SDCI_TC_0299 | TCM_PHYL_INTF_VOLTRANGECQ | CQ を 1Ω 経由で 0V および 30V に接続した後で動作するかどうかをテストします | 『IO-Link インターフェイスおよびシステム仕様書 V1.1.3』4のセクション 5.3.2.2、表 5 - VIL および VIH を参照してください | 合格 | |

| SDCI_TC_0021 | TCM_PHYL_INTF_IQWUH | 『IO-Link インターフェイスおよびシステム仕様書 V1.1.3』4のセクション 5.3.3.3、表 9 を参照してください | ファンクション・ジェネレータからのウェークアップ・パルス | VIM@WURQ (VSM = 20V):18.9V VIM@WURQ (VSM = 30V):28.5V 合格 |

|

| SDCI_TC_0022 | TCM_PHYL_INTF_TWUH | ファンクション・ジェネレータからのウェークアップ・パルス | TWUH@WURQ (VSM = 20V):80µs TWUH@WURQ (VSM = 30V):80µs 合格 |

||

| SDCI_TC_0023 | TCM_PHYL_INTF_IQWUL | ファンクション・ジェネレータからのウェークアップ・パルス | VIM@WURQ (VSM = 20V):0.9V VIM@WURQ (VSM = 30V):0.9V 合格 |

||

| SDCI_TC_0024 | TCM_PHYL_INTF_TWUL | ファンクション・ジェネレータからのウェークアップ・パルス | TWUL@WURQ (VSM = 20V):80µs TWUL@WURQ (VSM = 30V):80µs 合格 |