JAJY111C january 2023 – april 2023 LMQ61460-Q1 , TPS54319 , TPS62088 , TPS82671 , UCC12040 , UCC12050

パッケージの放熱特性の革新

IC のパッケージから熱を放出する能力は、電力密度に直接的な影響を及ぼします。すでに説明したように、パッケージが継続的に縮小している現状で、この能力はますます重要な問題になります。さらに、一般的なパワー・コンバータで、半導体デバイスは多くの場合、ソリューションの中で最も温度が高いパーツになります。Rsp が急激に縮小している現状で、特にこのことが当てはまります。

テキサス・インスツルメンツは HotRod™ パッケージの開発と採用に投資してきました。このパッケージは、標準的なワイヤ・ボンド・タイプの QFN (quad flat no-lead、クワッド・フラット、リードなし) パッケージを、フリップ・チップ・スタイルのパッケージで置き換えます。図 9 および図 10 は、HotRod QFN 採用でワイヤ・ボンドを排除すると同時に、QFN に近いフットプリントを維持する方法を示しています。この結果、標準的なフリップ・チップ・パッケージで見受けられる寄生ループのインダクタンスを大幅に低減しながら、QFN パッケージの放熱特性の利点をいくつか維持しています。HotRod QFN には、リードフレームとダイの間のインターコネクトが含まれています。

図 9 露出パッド付き標準ボンド・ワイヤ QFN パッケージ。

図 9 露出パッド付き標準ボンド・ワイヤ QFN パッケージ。 図 10 HotRod インターコネクト・パッケージ (フリップ・チップ・オン・リード) QFN パッケージ。

図 10 HotRod インターコネクト・パッケージ (フリップ・チップ・オン・リード) QFN パッケージ。HotRod パッケージに関連する 1 つの課題は、パッケージの放熱改善に非常に役立つことが多い、大型のダイ接続パッド (die attach pad、DAP) の製作が困難になることです。この課題を克服するために、テキサス・インスツルメンツは最近、HotRod QFN に拡張を加え、既存の利点を維持すると同時に、大型の DAP を取り付けたパッケージを実現できるようにしました。

図 11、図 12、および図 14 に、放熱性能を向上させるためにこれらのテクノロジーを拡張した 4-A LM60440 同期整流コンバータを示します。パッケージの中心にある大型の DAP を考慮したフットプリントになっていることを理解できます。以前の世代に比べて、この DAP は温度上昇の点で約 15% の改善を実現しています。これらのパッケージの進化の詳細については、テキサス・インスツルメンツの Analog Design Journal の記事『小型 DC/DC コンバータを使用した設計: HotRod™ QFN と Enhanced HotRod™ QFN パッケージの比較』を参照してください。

図 11 大型の DAP がある Enhanced HotRod QFN。

図 11 大型の DAP がある Enhanced HotRod QFN。 図 12 Enhanced HotRod QFN パッケージの LM60440 のピン配置。

図 12 Enhanced HotRod QFN パッケージの LM60440 のピン配置。 図 13 通常の HotRod パッケージの放熱性能。

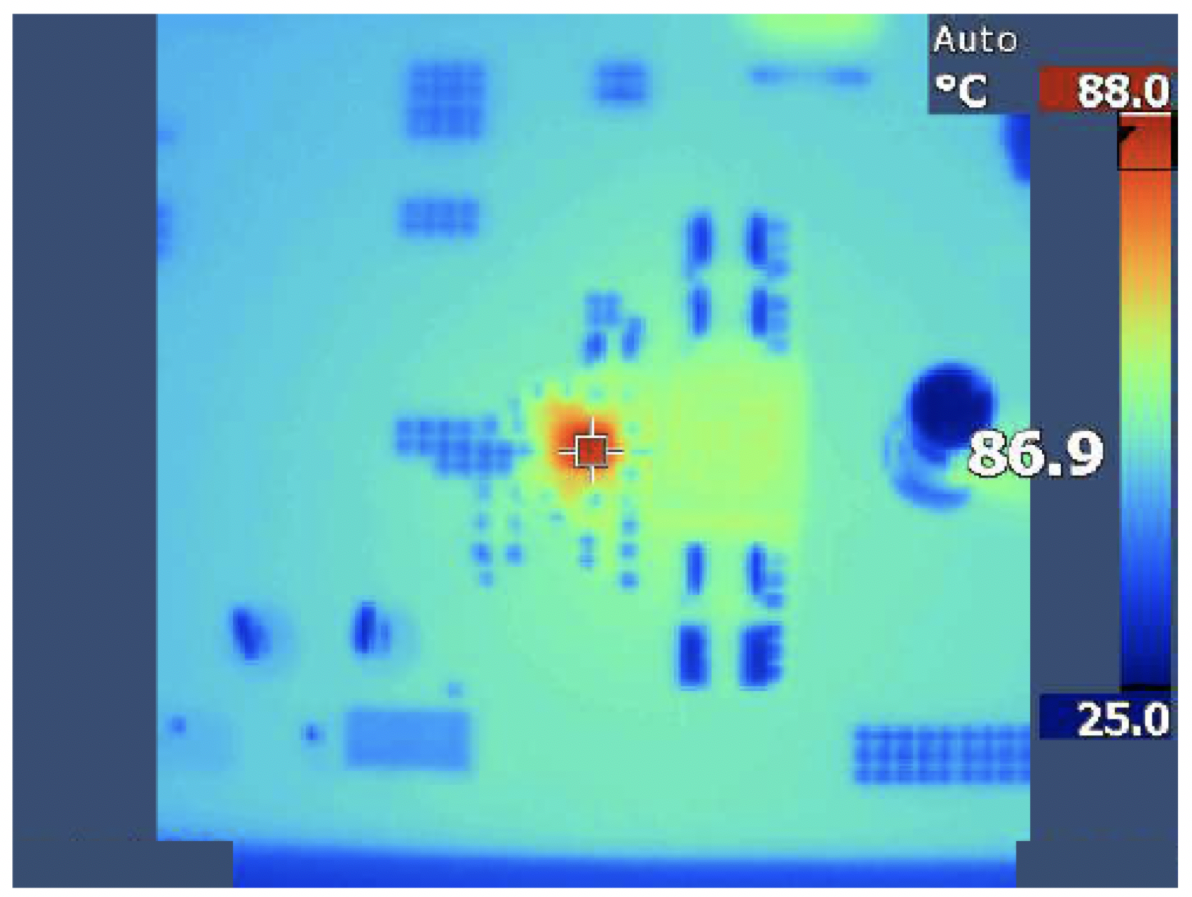

図 13 通常の HotRod パッケージの放熱性能。 図 14 Enhanced HotRod QFN パッケージに DAP を搭載した LM60440 の放熱性能。平均温度は 71.1℃まで低下

図 14 Enhanced HotRod QFN パッケージに DAP を搭載した LM60440 の放熱性能。平均温度は 71.1℃まで低下さらに、多くの設計者は、低コストでピン・リードが組み立てやすい SOT (Small-Outline Transistor) 表面実装パッケージの使用を望んでいます。テキサス・インスツルメンツは、より大きな電流密度の要件を薄型の 2 行ピン配置で満たせるように、向上したプロセス技術と回路 IP を SOT-563 パッケージと組み合わせました。最近の例の 1 つに、TPS566242 3V~16V 同期整流降圧コンバータが挙げられます。このデバイスは、1.6mm x 1.6mm の SOT-563 (6 ピン) のフットプリントで、98% デューティ・サイクルで最大 6A の連続電流をサポートします。

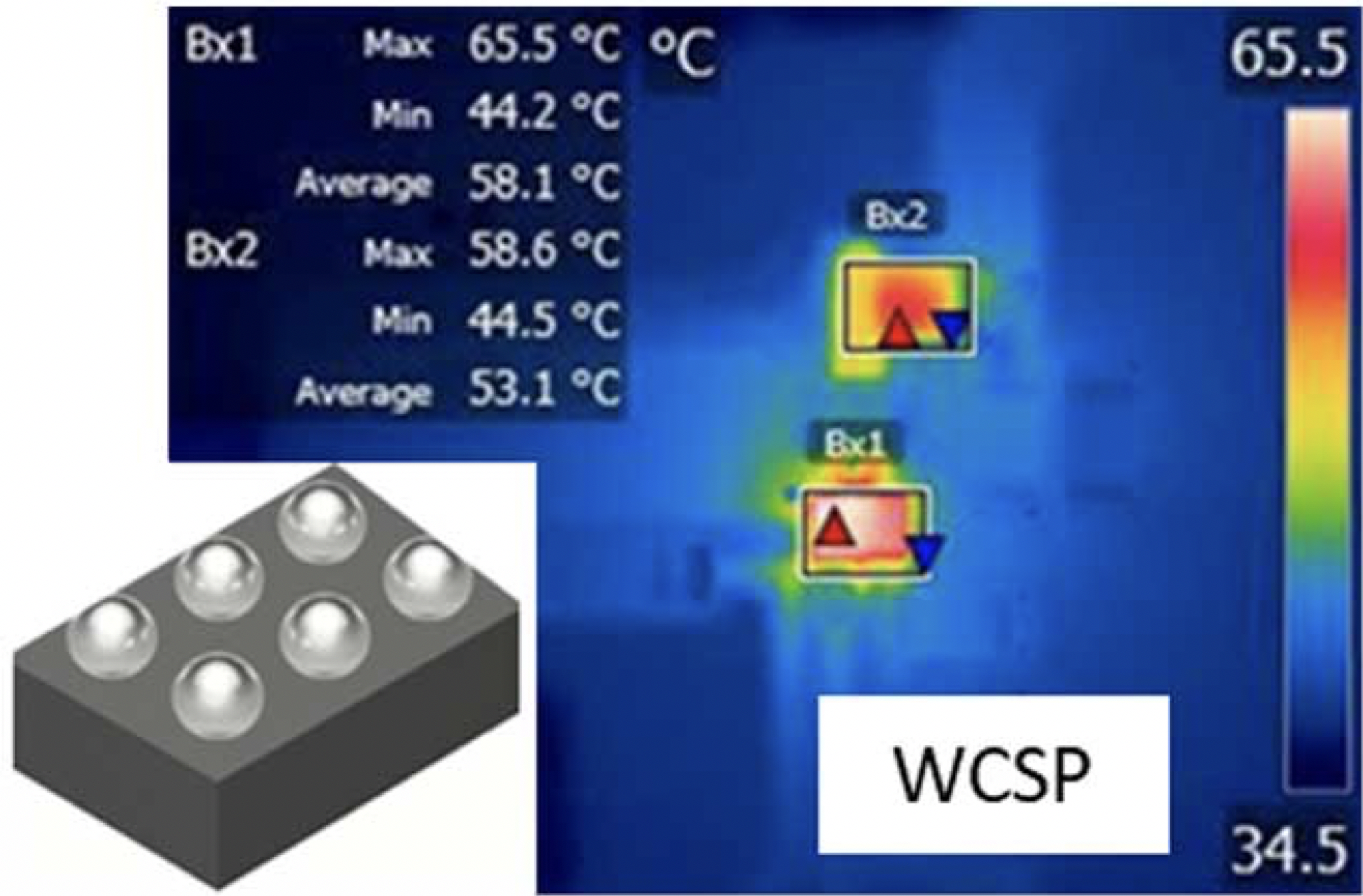

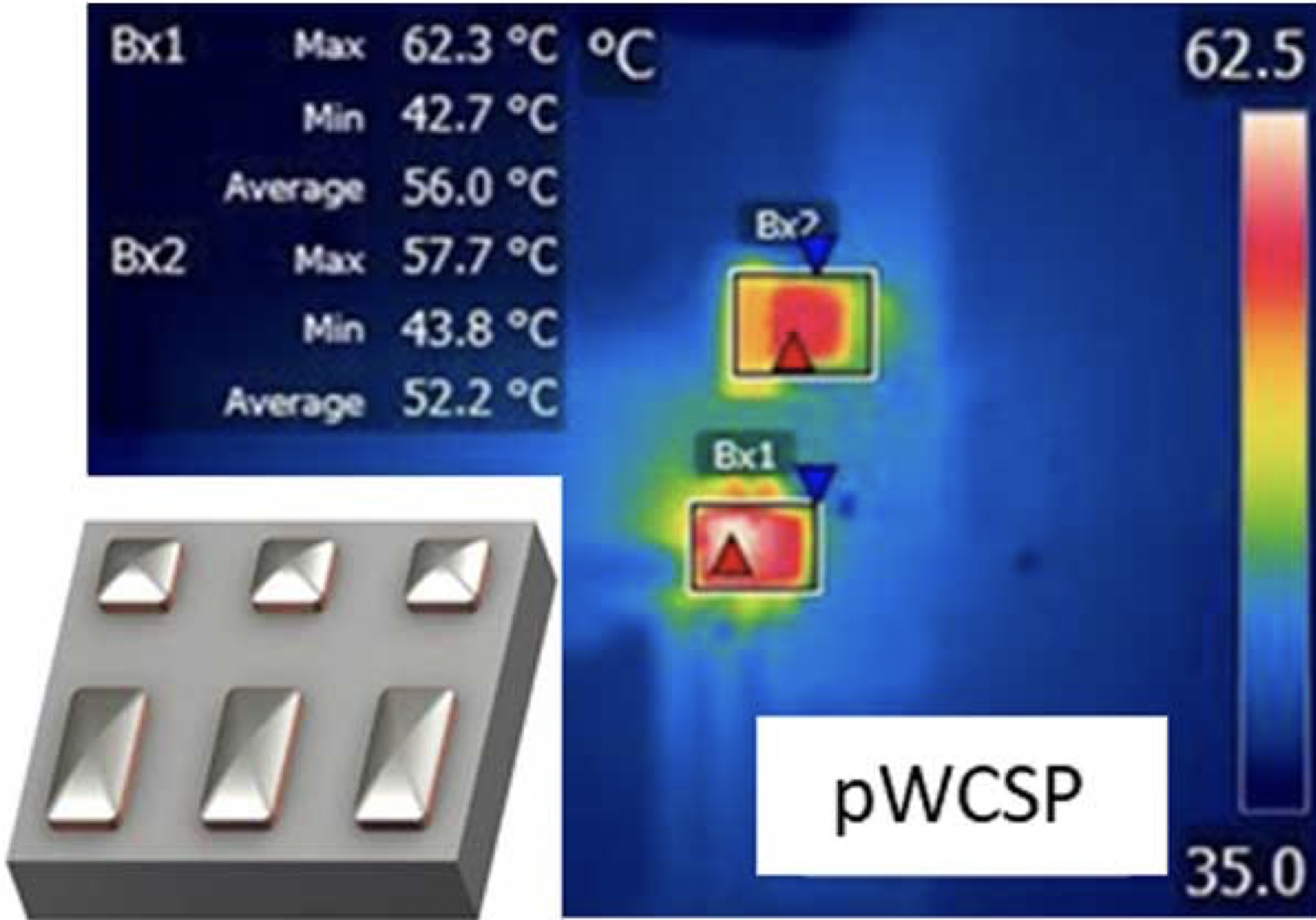

同様に、ウェハー・チップ・スケール・パッケージ (WCSP) を使用する場合、大半の熱はバンプ (突起) から外部へ直接伝わり、下部の PCB に移動します。WCSP のバンプ面積が広いほど、放熱特性は改善されます。テキサス・インスツルメンツは最近、PowerCSP™ パッケージを開発し、リリースしました。このパッケージは、WCSP の標準的な円形バンプのいくつかを大型の半田バーで置き換える方法で、パッケージの放熱特性と電気的性能を改善することを目的としています。図 15は、TPS62088 でのこのテクノロジーの実装例を示しています。図 15 は標準的な WCSP、図 16 は PowerCSP パッケージを採用した同じデバイスを示しています。温度上昇は約 5% 抑制され、システム内で他の変化は発生していません。

| VIN = 5V | VOUT = 1.8V |

| IOUT = 3A | TA = 25℃ |

| 測定ポイント:Bx1 |

| VIN = 5V | VOUT = 1.8V |

| IOUT = 3A | TA = 25℃ |

| 測定ポイント:Bx1 |