SBAA525A september 2021 – may 2023 AFE7900 , AFE7920 , AFE7950

2.1.4.2 ADC to DAC Low Latency Loopback

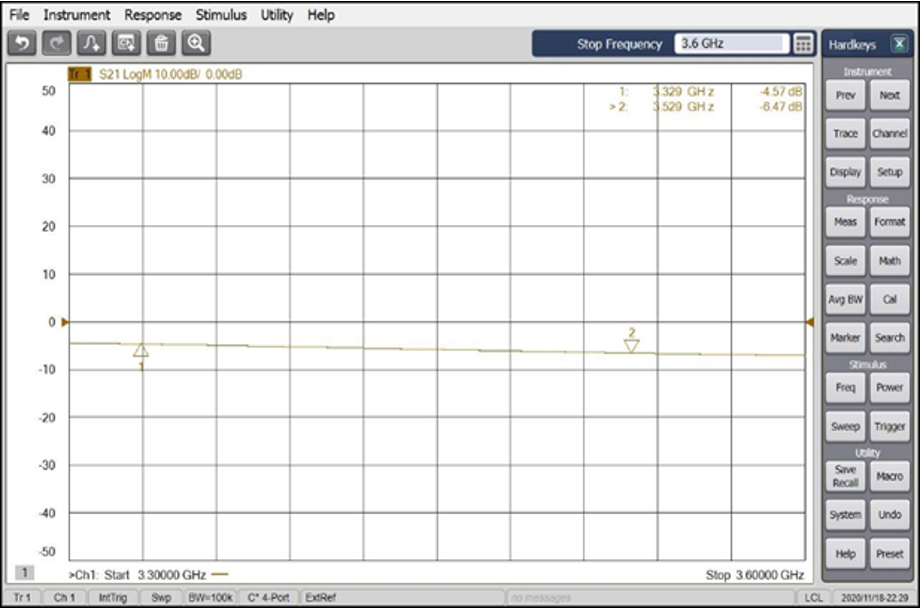

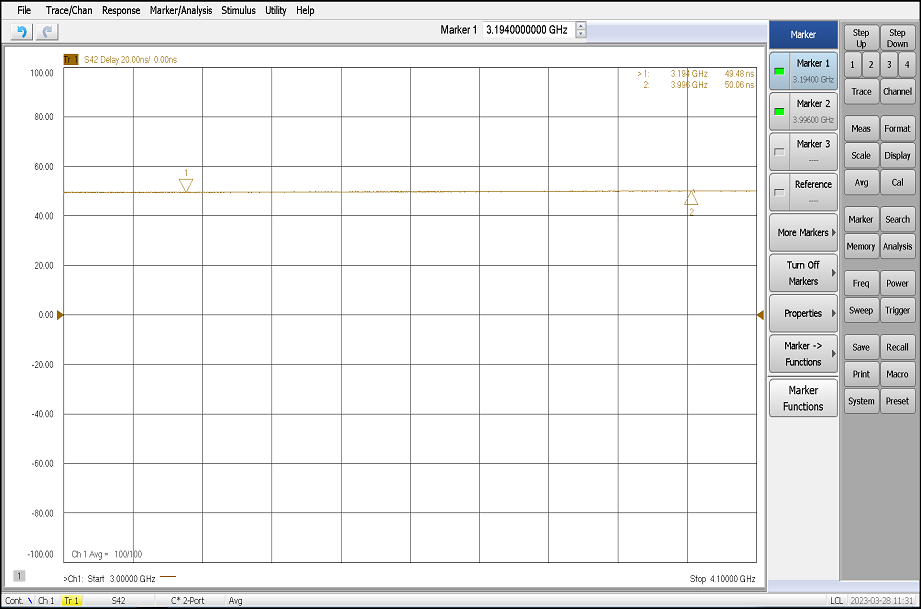

In this mode, the device is tested with loopback without DDC and JESD interface achieving high analog signal bandwidth (approximately 1 GHz). Magnitude response does not reflect any attenuation in pass band which is more dependent to external matching network loop response. Group Delay measures approximately 49.48 ns demonstrating lowest latency feedback signal chain.

Figure 2-14 Magnitude Response ADC to

DAC Low Latency Loopback

Figure 2-14 Magnitude Response ADC to

DAC Low Latency Loopback Figure 2-15 Group Delay ADC to DAC Low

Latency Loopback

Figure 2-15 Group Delay ADC to DAC Low

Latency LoopbackThere is a function named lowLatencyModeProgDelay(afeInst, chNo, progDelay) which can be used to vary the values of latency in this mode. Here, chNo is set to 0 for FBAB and 1 for FBCD. The value of progDelay can be varied from 0 to 23 where 0 corresponds to minimum latency. The loop latency increases as the value of progDelay is increased from 0 to 23.