SBAA525A september 2021 – may 2023 AFE7900 , AFE7920 , AFE7950

2.1.2.1 ADC to DAC JESD Loopback

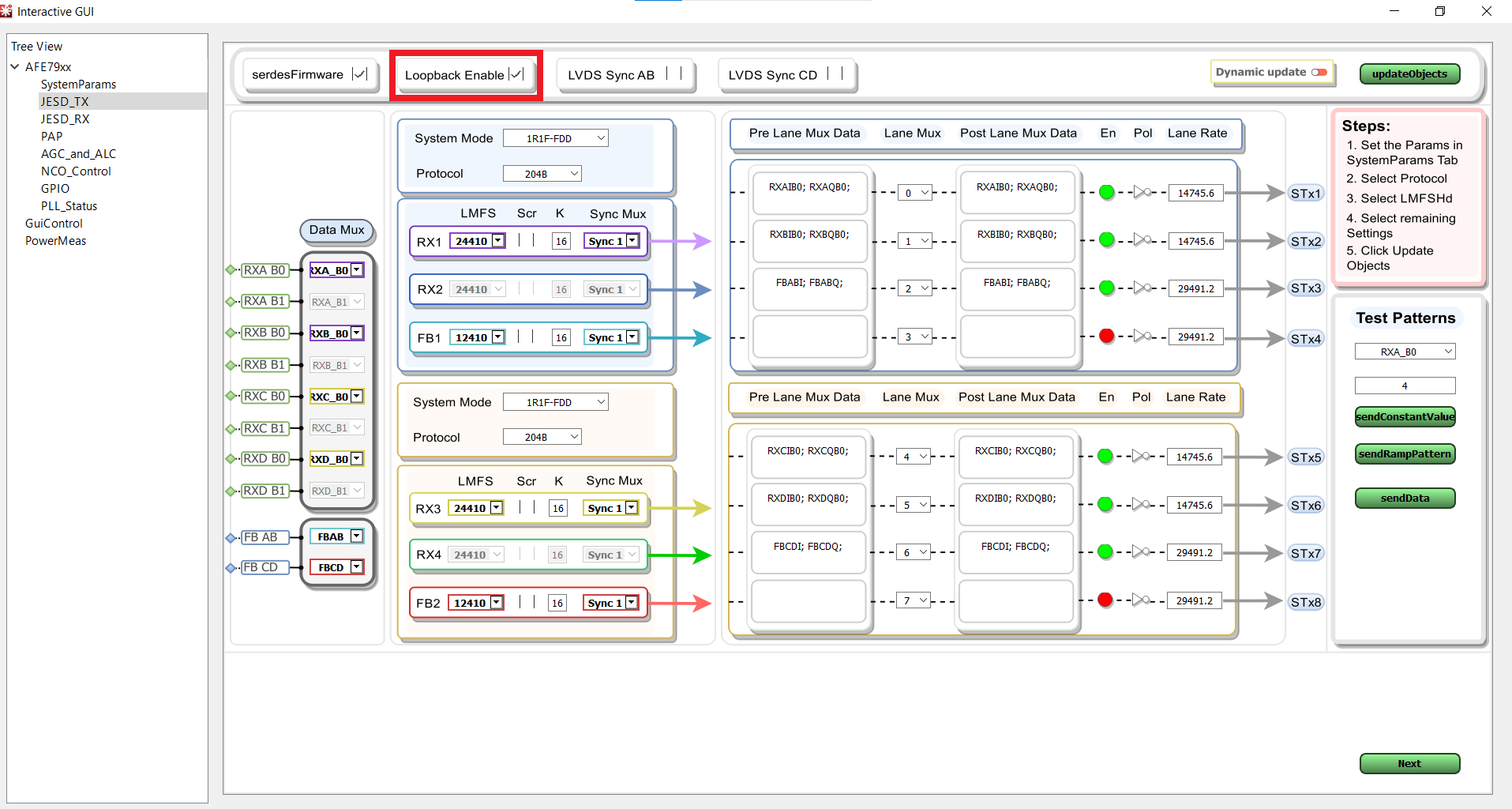

AFE supports RX ADC to DAC loopback through the internal JESD block. This can be enabled by setting jesdLoopBackEn to True. Below are the conditions to be satisfied for using this feature.

- The ADC and DAC interface rates must be same.

- The JESD settings and the lane rates must be same for both RX and TX.

- RXA must loop back to TXA, RXB must loop back to TXB, and so on.

- Loopback mode is enabled using

the check box as shown in Figure 2-3.

Figure 2-3 ADC to DAC JESD Loop

Back Enable Mode

Figure 2-3 ADC to DAC JESD Loop

Back Enable Mode