SLAAEI9 December 2023 MSPM0C1104 , MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3107-Q1 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507 , MSPM0G3507-Q1 , MSPM0L1105 , MSPM0L1106 , MSPM0L1228

- 1

- Abstract

- Trademarks

- 1MSPM0 Portfolio Overview

-

2Ecosystem And Migration

- 2.1 Ecosystem Comparison

- 2.2 Migration Process

- 2.3 Example

- 3Core Architecture Comparison

- 4Digital Peripheral Comparison

- 5Analog Peripheral Comparison

3.6.2 Event Handler of MSPM0

MSPM0 MCUs have an event manager that transfers digital events from one entity to another. The event manager implements event transfer through a defined set of event publishers (generators) and subscribers (receivers) that are interconnected through an event fabric containing a combination of static and programmable routes. The event manger can also perform handshaking with the power management and clock unit (PMCU), to make sure that the necessary clock and power domain are present for triggered event actions to take place.

Events that are transferred by the event manager include:

- Peripheral event transferred to the CPU as an interrupt request (IRQ)

- Peripheral event transferred to the DMA as a DMA trigger

- Peripheral event transferred to another peripheral to directly trigger an action in hardware

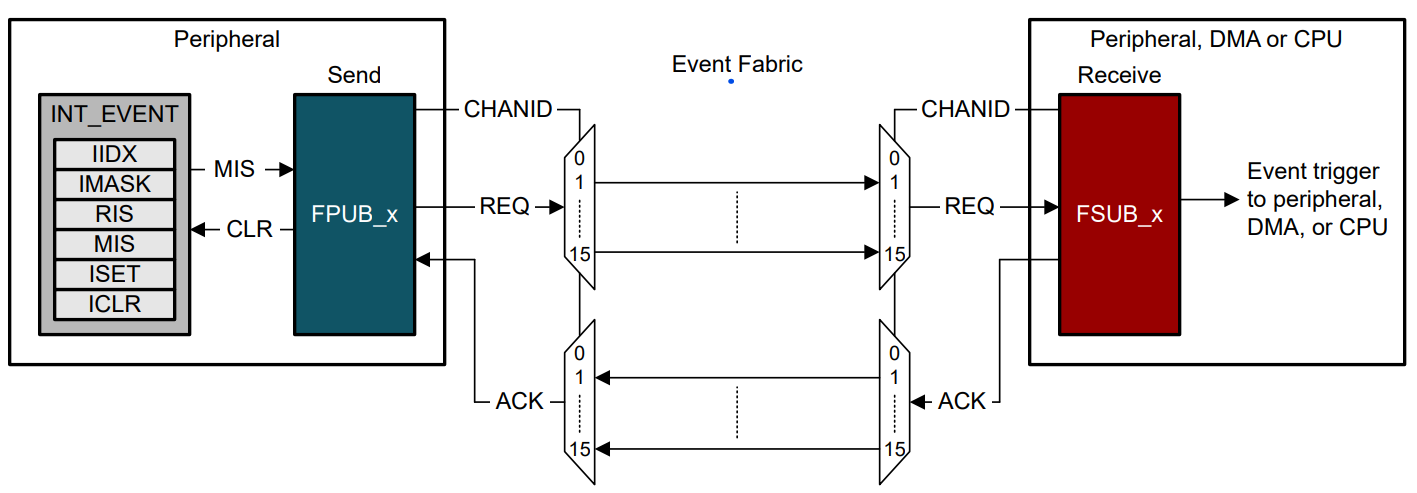

The event manager connects event publishers to event subscribers through an event fabric. There are three types of event fabric: CPU interrupt (Fixed event route), DMA route, and generic route. For example, Figure 3-4 shows the generic route.

Figure 3-4 Generic Event Route

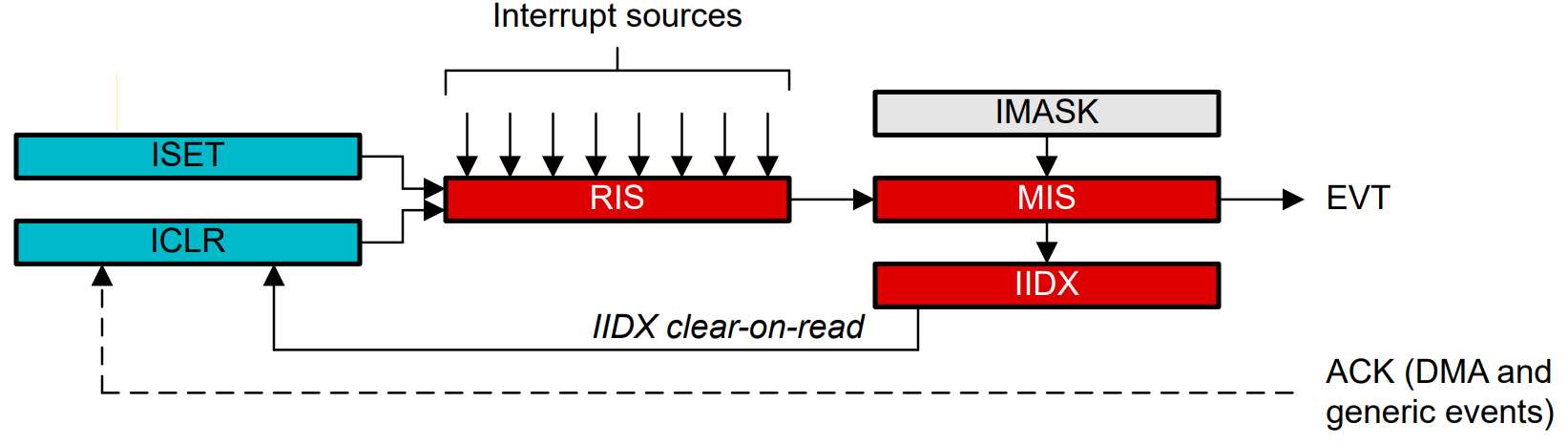

Figure 3-4 Generic Event RouteThe event management register set contains six standard registers: RIS, IMASK, MIS, ISET, ICLR, and IIDX. And the event registers are interconnected as shown in Figure 3-5. Once unmasked, a pending interrupt is indicated in both the RIS and MIS registers, and an event is generated. In the case of a CPU interrupt with a CPU interrupt event route, a read of the IIDX register clears the highest priority pending interrupt in the RIS and MIS registers and return the index of the highest priority pending interrupt to application software.

Figure 3-5 Event Management Register Relationship

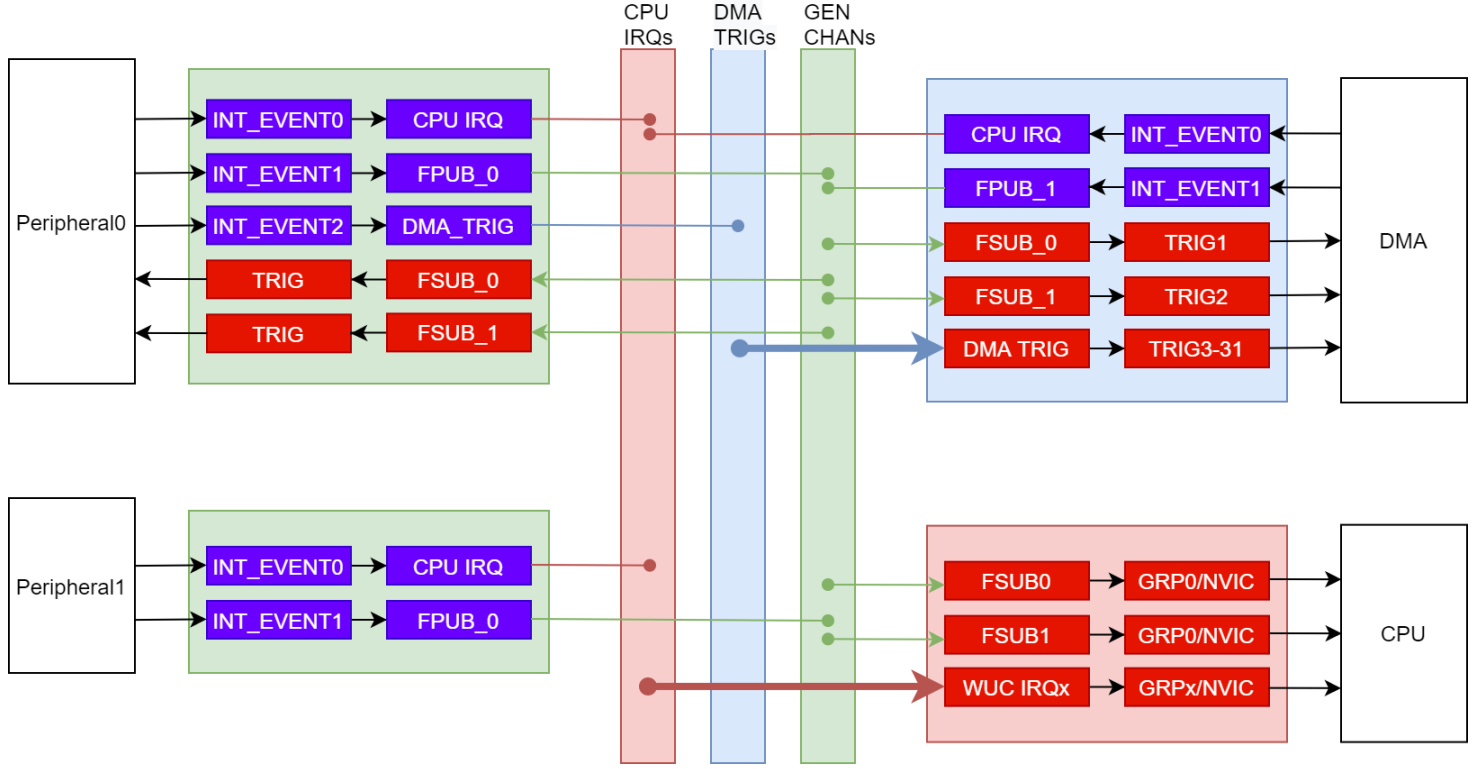

Figure 3-5 Event Management Register RelationshipFigure 3-6 shows the event map. Different peripherals are routed through different event fabrics to achieve different event transitions. For more details on the use of the event handler in MSPM0, see the Event section of the MSPM0L technical reference manual, or the MSPM0C technical reference manual.

Figure 3-6 MSPM0 Event and Interrupt

Handling

Figure 3-6 MSPM0 Event and Interrupt

Handling