SLUAAL2 june 2023 UCC256402 , UCC256403 , UCC256404

- 1

- Abstract

- Trademarks

-

1UCC25640x Frequently Asked Questions

- 1.1 For the Time Domain Simulation and Fundamental Harmonic Analysis of LLC Resonant Converters, What Model of the Transformer Should be Used?

- 1.2 How to Connect External Gate Drivers to the UCC25640x for High Gate Driver Current Capability?

- 1.3 When Powering on the PFC-LLC AC-DC Converter, What Sequence is Recommended?

- 1.4 How to Eliminate the Nuisance ZCS Detection During the Light Load?

- 1.5 What is the Purpose of Maintaining the FB Pin Voltage of the UCC25640x Controllers at a Constant Level?

- 1.6 How to Improve the Slew Rate Detection at HS Pin of the UCC25640x Controller?

- 1.7 How to Operate the UCC25640x Controller in the Open Loop?

- 1.8 What Happens if the VCR Pin Peak to Peak Voltage of the Controller Exceeds 6 V?

- 1.9 What UCC25640x settings effect the startup duration of the LLC?

- 1.10 What is Causing the Current Imbalance in the LLC's Secondary Side Windings?

- 1.11 How to Design TL431 Compensator for LLC With UCC25640x Controller

- 1.12 How to Design LLC for Battery Charging and LED Driver Applications?

- 1.13 How to Implement CC-CV Feedback Control?

- 1.14 What is the Simplest Approach to Configure the Burst Mode Thresholds for UCC25640x Based on the Load Power?

- 1.15 How to Avoid the UCC25640x Controller to Enter into Burst Mode?

- 1.16 What are the Methods for Preventing VCC From Decreasing Below the VCC Restart Threshold During Burst Mode?

- 1.17 How Does BMTL Threshold Value Impacts the Output Voltage Ripple and the VCC Pin Voltage and Magnetizing Current?

- 1.18 How to Design Magnetics for LLC?

- 1.19 How is the Dead Time in UCC25640x Determined During ZCS Detection and in the Absence of Valid Slew Rate Detection?

- 2References

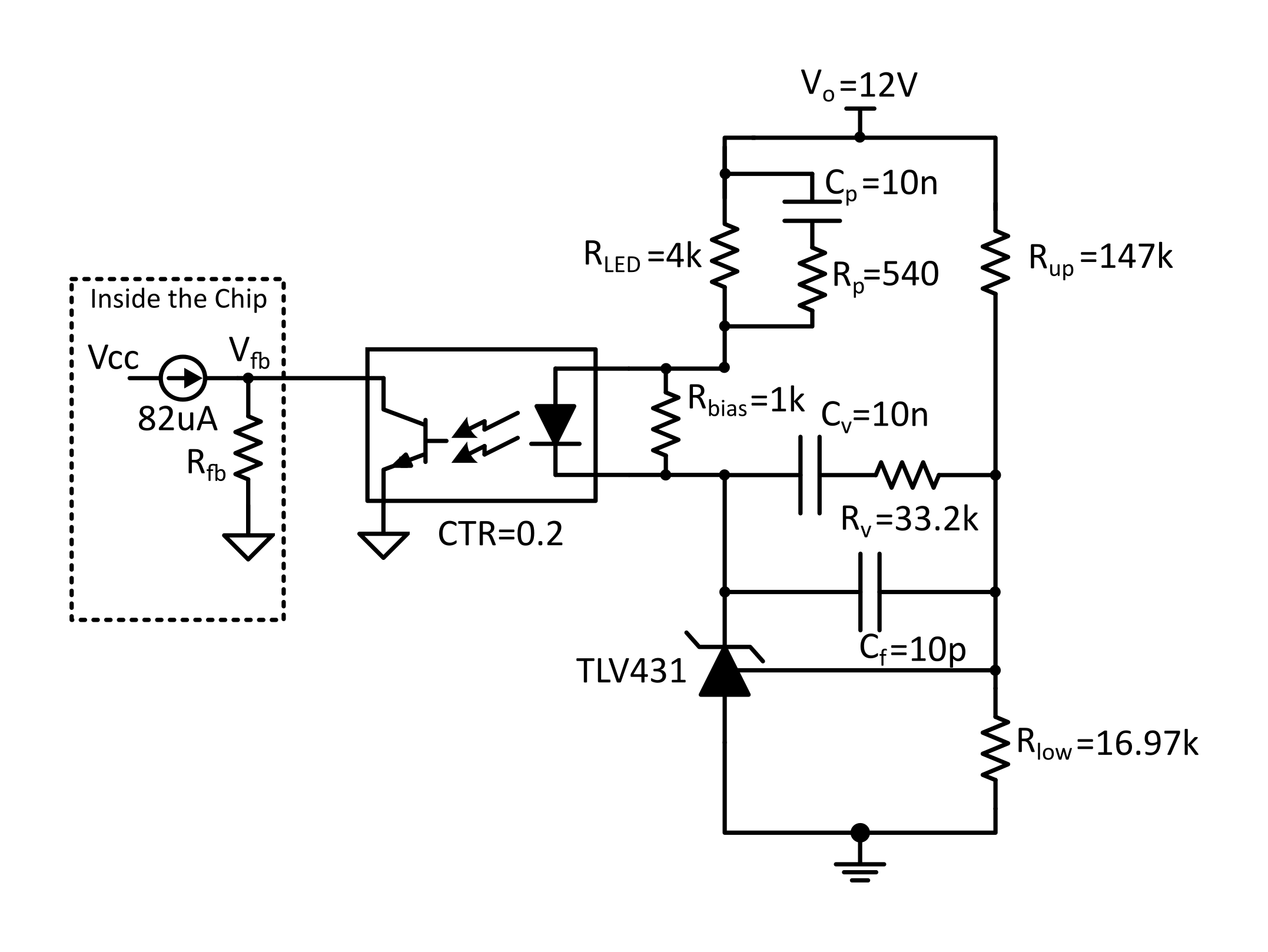

1.11.3 Type 3 Compensator Design Example

The power stage of the UCC25640x EVM [3] is considered to demonstrate the Type 3 compensator [1.12.2.3] design which is shown in Figure 1-27. Lets consider 10kHz as a cross over frequency (fc) for the loop gain.

- From Figure 1-22, the open loop gain is close to -25dB at 10kHz.

- So should be 25dB at the cross over frequency.

- Assuming in [1.12.2.3], can be approximated as . For a given phase lead ( ), cross over frequency ( ), fz, fp2 can be found out using following equations [Chapter 9.5 in Reference 9]: , , . So, .

- For a phase lead of 52o, fz and fp2 should be 3.4kHz and 29kHz respectively.

- Since fz, fp2 are found out, Go can be obtained using following expression: (25dB=17.78).

- fp1 is a high frequency pole which is used to eliminate the high frequency noise. It is recommended to place this pole close to ESR of the output capacitor. Here fp1 is chosen as 479kHz.

- fL should be chosen such that controller should be able to regulate the output voltage when the converter operates in the burst mode. So, fL should be less than the burst mode frequency. In this design, fL is considered as 88Hz.

- Rup and Rlow can be found out using following expressions: where Vo is output voltage and Vref, Iref are reference voltage and bias current through the reference pin of the shunt regulator. To make Vo independent of the Iref, the Iref should be much lower than . So, . In the EVM, TLVH431 is considered for which reference voltage is given as 1.24V. For this design, is considered as 73uA. So Rup obtained as 147kOhm. And from , Rlow obtained as 16.98kohm.

- Consider Cf as 10pF. So, Rv can be obtained as

- RLED can be obtained as

- Cv can be obtained as

- Cp, Rp are obtained as .

- Rbias is used to bias the shunt regulator. Rbias is obtained as .

Figure 1-27 Type 3 Compensator

Figure 1-27 Type 3 Compensator