SLVUBI1 May 2021

4.2 Output Voltage Ripple

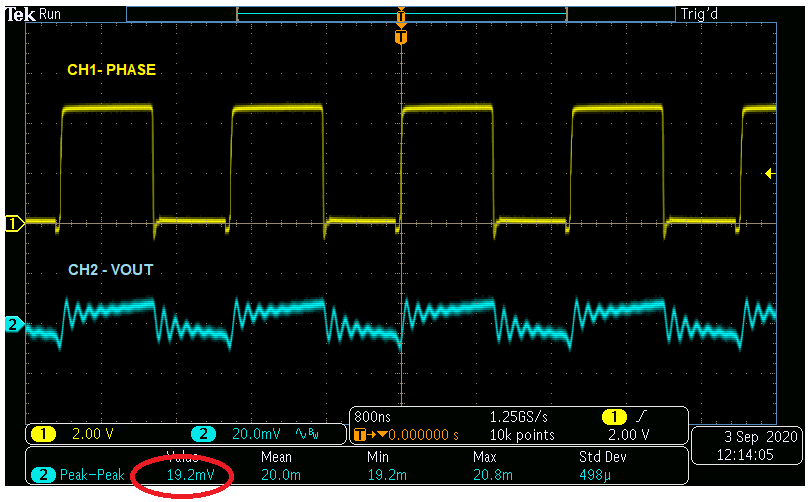

Display CH1 (PH1) and CH2 (VOUT1) [AC coupled, BW = 20 MHz] on the oscilloscope to monitor the switching phase node and the output voltage ripple as shown in Figure 4-2.

Figure 4-2 Output Voltage Ripple VIN = 5

V, VOUT = 2.5 V, IOUT = 3 A

Figure 4-2 Output Voltage Ripple VIN = 5

V, VOUT = 2.5 V, IOUT = 3 A