SLWU087E november 2013 – june 2023

- 1

- High Speed Data Converter Pro GUI

- Trademarks

- 1 Introduction

- 2 Software Start up

-

3 User Interface

- 3.1

Toolbar

- 3.1.1 File Options

- 3.1.2 Instrument Options

- 3.1.3 Data Capture Option

- 3.1.4

Test Options

- 3.1.4.1 Notch Frequency Bins

- 3.1.4.2 2 Channel Display and Cursor Lock

- 3.1.4.3 Analysis Window Markers

- 3.1.4.4 X-Scale in Time

- 3.1.4.5 Y-Scale in Voltage

- 3.1.4.6 Other Frequency Options

- 3.1.4.7 NSD Marker

- 3.1.4.8 Phase Plot

- 3.1.4.9 Phase in Degree

- 3.1.4.10 Histogram

- 3.1.4.11 Disable User Popups

- 3.1.4.12 HSDC Pro Lite Version

- 3.1.5 Help

- 3.2 Status Windows

- 3.3 Mode Selection

- 3.4 Device Selection

- 3.5 Skip Configuration

- 3.6 Capture Button (ADC Mode Only)

- 3.7 Test Selection (ADC Mode only)

- 3.8 DAC Display Panel (DAC Mode only)

- 3.9 I/Q Multi-Tone Generator

- 3.1

Toolbar

- 4 ADC Data Capture Software Operation

- 5 TSW1400 Pattern Generator Operation

- 6 TSW14J58 Functional Description

- 7 TSW14J57 Functional Description

- 8 TSW14J56 Functional Description

- 9 TSW14J50 Functional Description

- 10TSW14J10 Functional Description

- A Signal Processing in High Speed Data Converter Pro

- B History Notes

- C Revision History

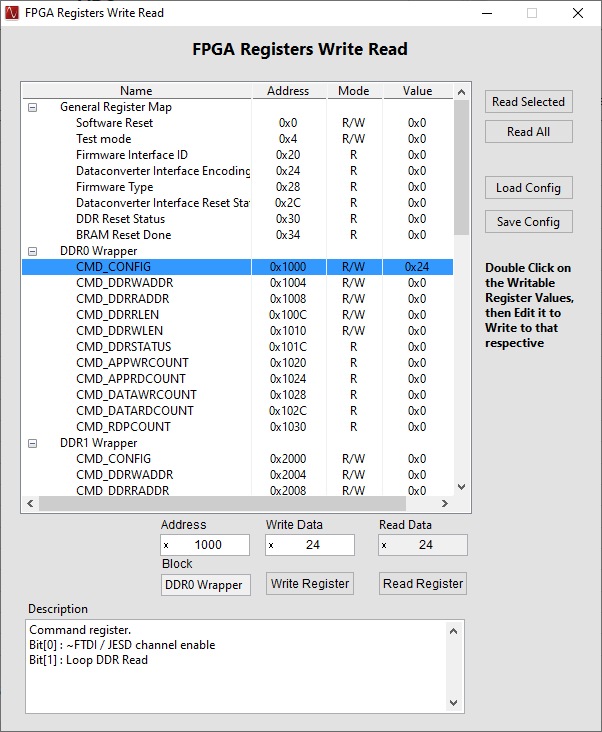

3.1.2.4 FPGA Registers Write Read

The FPGA Registers Write Read menu option (shown in Figure 3-8) allows the user to write/read the registers of the FPGA Firmware. The firmware register map of the TSW14xxx board is loaded and the Register Name, Register Address, R/W Mode, Register Values and Register Description is shown. The register write operation is done by selecting the required register element from the tree or by specifying the required register address in the "Address" input control and providing a value to be written at "Write Data" input control and then clicking on the "Write Register" button. Similarly, the register read operation is done by clicking on the "Read Register" button after specifying the required register address and the read register value are updated both in the register tree and "Read Data" output indicator. The current register configuration listed in the register map is exported as “.cfg” file by using the “Save Config” button and the same is loaded by using the “Load Config” button. The “Load Config” operation overwrites the existing data in registers with the value specified in the loaded configuration file.

Figure 3-8 FPGA Registers Write Read

Window

Figure 3-8 FPGA Registers Write Read

Window