SPRAD61A March 2023 – November 2023 AM2732 , AM2732 , AM2732-Q1 , AM2732-Q1

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Power

- 3 Clocking

- 4 Resets

- 5 Bootstrapping

- 6 JTAG Emulators and Trace

- 7 Multiplexed Peripherals

- 8 Digital Peripherals

- 9 Layer Stackup

- 10Vias

- 11BGA Power Fan-Out and Decoupling Placement

- 12References

- 13Revision History

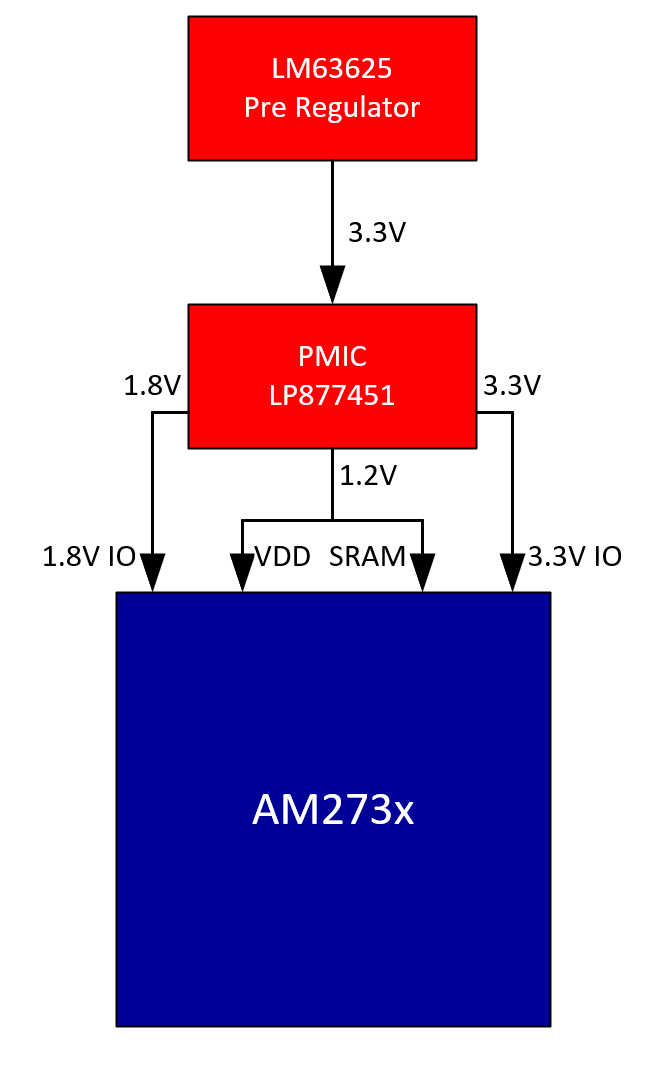

2.2 Integrated PMIC Power Solution

The AM273x GP EVM integrates a Power Management Integrated Circuit (PMIC) based power solution that may be used as a reference solution for some systems. The solution consists of a LM63625 voltage converter pre-regulator and a LP877451 PMIC to generate the MCU core, SRAM, system digital and analog I/O power. A TPS73501 Low Drop Out (LDO) regulator is used for the Ethernet PHY.

The power good generation circuits available on the PMIC and DC-DC regulators should be combined to a single line and used to drive the reset (nRESET) of the AM273x device.

Figure 2-1 AM273x PMIC Example Solution

Figure 2-1 AM273x PMIC Example Solution Figure 2-2 AM273x PMIC 3.3V Pre-Regulator

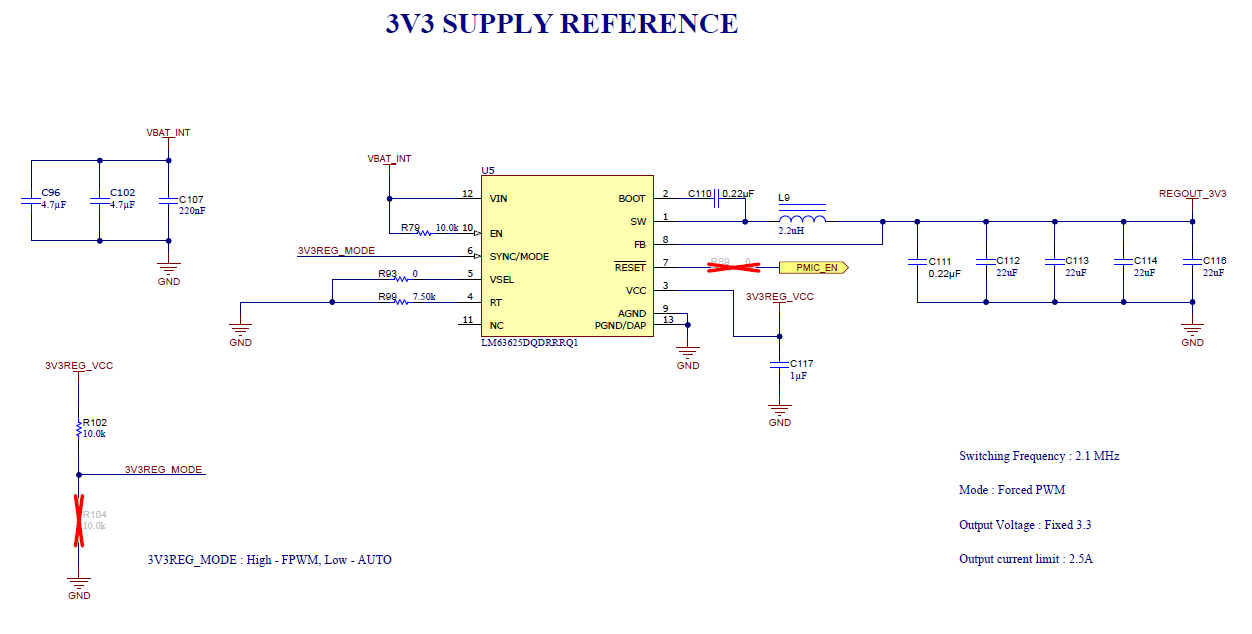

Implementation

Figure 2-2 AM273x PMIC 3.3V Pre-Regulator

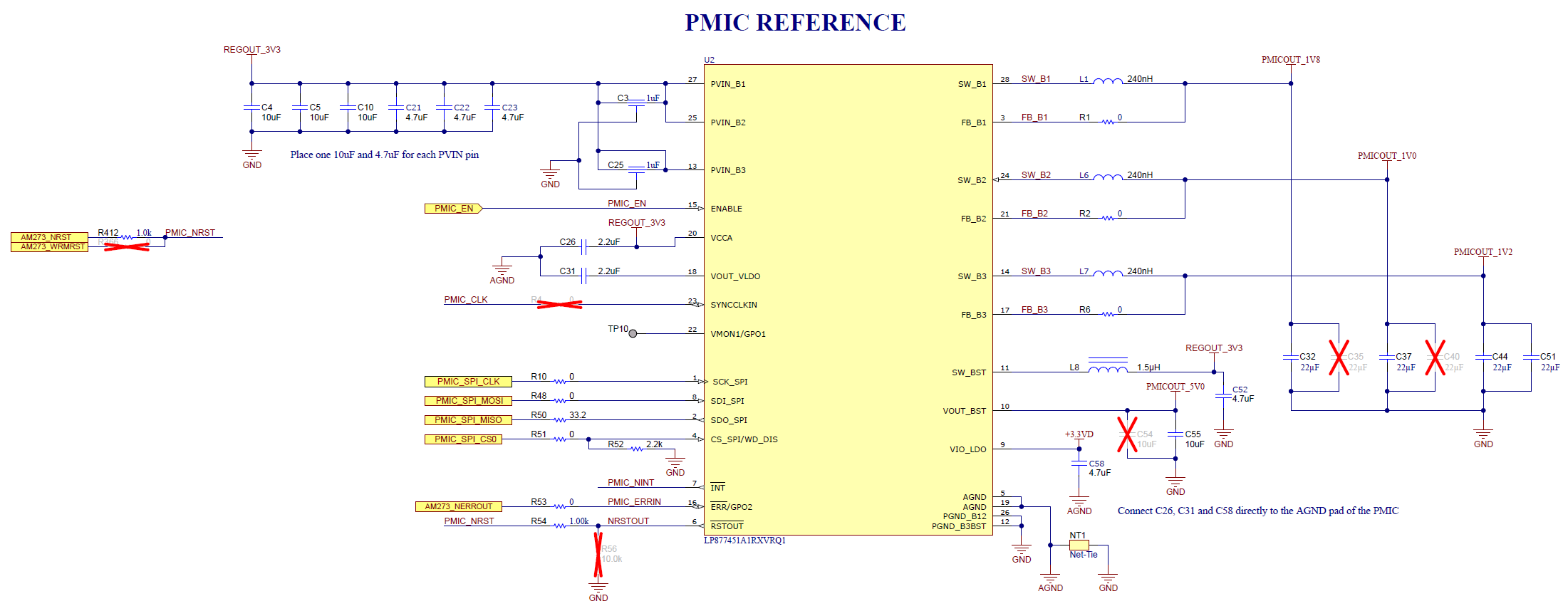

Implementation Figure 2-3 AM273x PMIC Implementation

Figure 2-3 AM273x PMIC Implementation