SPRUIT1B May 2020 – November 2020

- Trademarks

- 1Introduction

- 2GESI Expansion Board Overview

- 3GESI Expansion Board - User Setup/Configuration

- 4GESI Expansion Board Hardware Architecture

- A Interface Mapping

- B GESI Board GPIO Mapping

- C I2C Address Mapping

- D Revision History

4.9 GESI LaunchPad-Booster Pack Interface

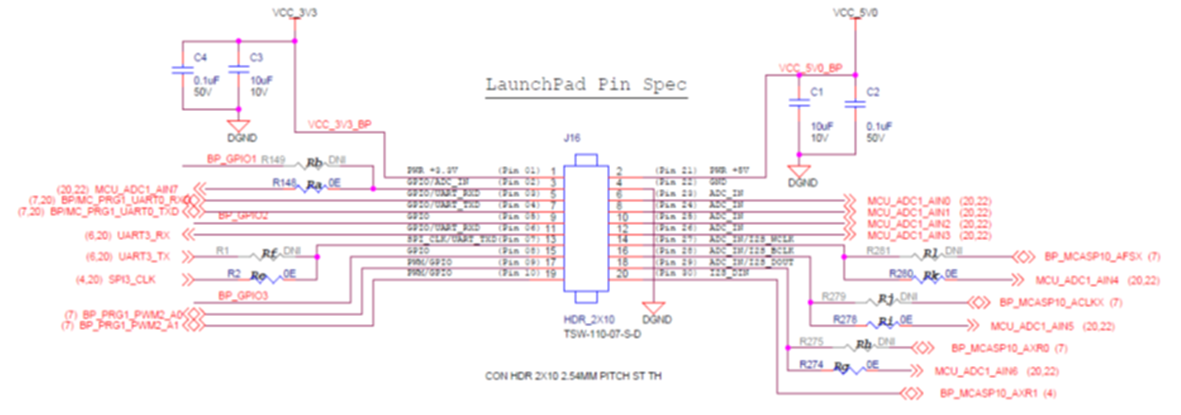

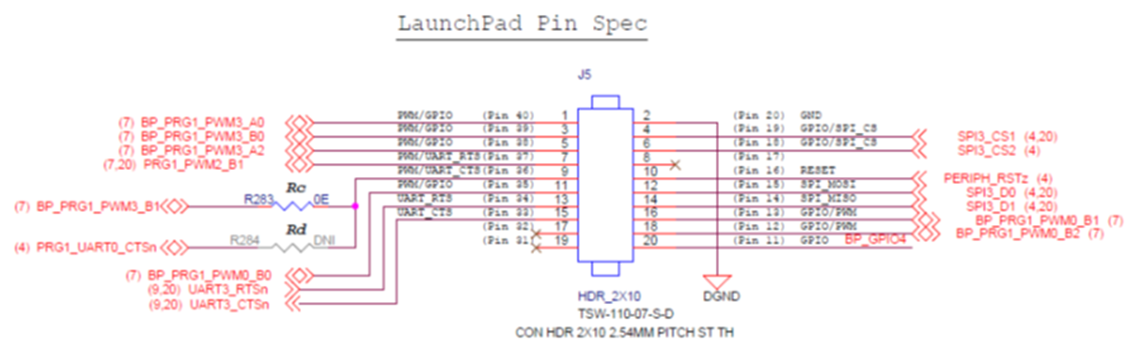

A GESI Launchpad connectors (J5 and J16) provided in GESI board to interface with Boosterpack modules. BoosterPack plug-in modules shall be plugged in to extend the functionality like wireless connectivity, capacitive touch, temperature sensing, displays and much more. Table 4-7 contains the pin out details of both connectors.

Except BOOST-DRV8848, all other BP interfaces listed below are supported similar to Maxwell EVM:

- BOOSTXL-ULN2003

- BOOST-DRV8711

- BOOSTXL-DRV8301

- CC3100BOOST

- BOOST-CC2564MODA

For resistor population option to support specific Boosterpack module, see Figure 4-13.

Table 4-7 Pinouts of Booster Pack

Interfacing Connectors

| J16 – LHS | J5 – RHS | ||||

|---|---|---|---|---|---|

| Pin | Net Name | Function | Pin | Net Name | Function |

| 1 | VCC_3V3_BP | 1 | BP_PRG1_PWM3_A0 | PWM/GPIO | |

| 2 | VCC_5V0_BP | 2 | DGND | ||

| 3 | MCU_ADC1_AIN7 | GPIO/ADC_IN | 3 | BP_PRG1_PWM3_B0 | PWM/GPIO |

| 4 | DGND | 4 | SPI3_CS1 | GPIO/SPI_CS | |

| 5 | BP/MC_PRG1_UART0_RXD | GPIO/UART_RXD | 5 | BP_PRG1_PWM3_A2 | PWM/GPIO |

| 6 | MCU_ADC1_AIN0 | ADC_IN | 6 | SPI3_CS2 | GPIO/SPI_CS |

| 7 | BP/MC_PRG1_UART0_TXD | GPIO/UART_TXD | 7 | PRG1_PWM2_B1 | PWM/UART_RTS |

| 8 | MCU_ADC1_AIN1 | ADC_IN | 8 | NC | |

| 9 | BP_GPIO2 | GPIO | 9 | BP_PRG1_PWM3_B1 | PWM/UART_CTS |

| 10 | MCU_ADC1_AIN2 | ADC_IN | 10 | PERIPH_RSTz | RESET |

| 11 | UART3_RX | GPIO/UART_RXD | 11 | BP_PRG1_PWM0_B0 | PWM/GPIO |

| 12 | MCU_ADC1_AIN3 | ADC_IN | 12 | SPI3_D0 | SPI_MOSI |

| 13 | SPI3_CLK | SPI_CLK/UART_TXD | 13 | UART3_RTSn | UART_RTS |

| 14 | MCU_ADC1_AIN4 | ADC_IN/I2S_WCLK | 14 | SPI3_D1 | SPI_MISO |

| 15 | BP_GPIO3 | GPIO | 15 | UART3_CTSn | UART_CTS |

| 16 | MCU_ADC1_AIN5 | ADC_IN/I2S_BCLK | 16 | BP_PRG1_PWM0_B1 | GPIO/PWM |

| 17 | BP_PRG1_PWM2_A0 | PWM/GPIO | 17 | NC | |

| 18 | MCU_ADC1_AIN6 | ADC_IN/I2S_DOUT | 18 | BP_PRG1_PWM0_B2 | GPIO/PWM |

| 19 | BP_PRG1_PWM2_A1 | PWM/GPIO | 19 | NC | |

| 20 | BP_MCASP10_AXR1 | I2S_DIN | 20 | BP_GPIO4 | GPIO |

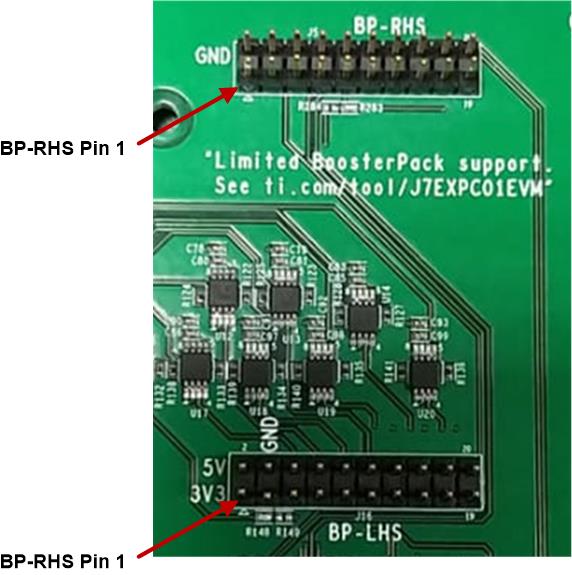

Figure 4-13 shows the BoosterPack headers on GESI Expansion Board.

Figure 4-13 BoosterPack Headers

Figure 4-13 BoosterPack Headers Figure 4-14 BoosterPack I/F LHS

Headers

Figure 4-14 BoosterPack I/F LHS

Headers Figure 4-15 BoosterPack I/F RHS

Headers

Figure 4-15 BoosterPack I/F RHS

Headers Figure 4-16 GESI launchpad-Booster Pack

Pinout

Figure 4-16 GESI launchpad-Booster Pack

Pinout