SPRUJA2 November 2023

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Additional Images

- 2.2 Key Features

- 2.3 Interface Mapping

- 2.4 Power ON/OFF Procedure

- 2.5 Clocking

- 2.6 Reset

- 2.7 CSI Interface

- 2.8 OLDI Interface

- 2.9 DSI Interface

- 2.10 Audio Codec Interface

- 2.11 HDMI Display Interface

- 2.12 JTAG Interface

- 2.13 Test Automation Header

- 2.14 UART Interface

- 2.15 USB Interface

- 2.16 Memory Interfaces

- 2.17 Ethernet Interface

- 2.18 GPIO Port Expander

- 2.19 GPIO Mapping

- 2.20 Power

- 2.21 EVM User Setup/Configuration

- 2.22 Expansion Headers

- 2.23 Interrupt

- 2.24 I2C Address Mapping

- 3Hardware Design Files

- 4Compliance Information

- 5Additional Information

2.21.2 Boot Modes

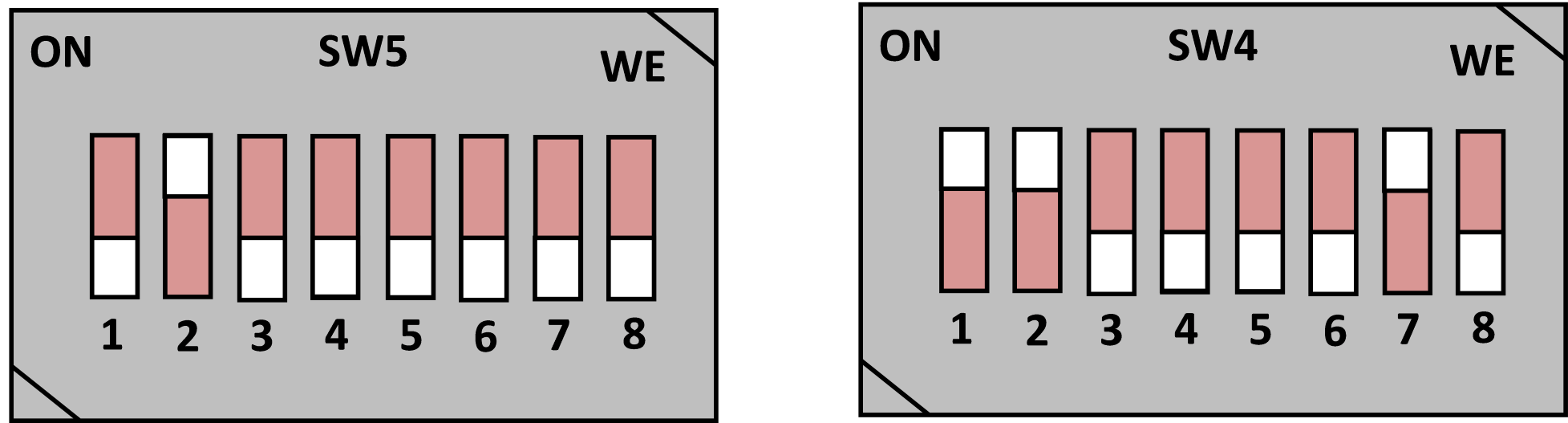

The boot mode for the SK EVM is defined by two banks of switches SW4 and SW5 or by the I2C buffer connected to the Test automation (XDS110 & Header). This allows for AM62P SOC Boot mode control by either the user (DIP Switch Control) or by the Test Automation.

All the bits of switch (SW4 & SW5) have a weak pull down resistor and a strong pull up resistor. Note that OFF setting provides a low logic level (‘0’) and an ON setting provide a high logic level (‘1’).

Figure 2-27 Boot Mode Switch (MMCSD

Boot)

Figure 2-27 Boot Mode Switch (MMCSD

Boot)The boot mode pins of the SOC have associated alternate functions during normal operation. Hence isolation is provided using Buffer IC’s to cater for alternate pin functionality. The output of the buffer is connected to the boot mode pins on the AM62P SOC and the output is enabled only when the boot mode is needed during a reset cycle.

The input to the buffer is connected to the DIP switch circuit and to the output of an I2C IO Expander set by the test automation circuit. If the test automation circuit controls the boot mode, then all the switches are manually set to the OFF position. The boot mode buffer is powered by an always ON power supply to make sure that the boot mode remains present even if the SOC is power cycled.

Switch SW4 and SW5 bits [15:0] are used to set the SOC Boot mode.

The switch map to the boot mode functions is provided in the tables below.

| Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Reserved | Reserved | Backup boot mode configuration | Backup boot mode | Primary boot mode configuration | Primary boot mode | PLL configuration | |||||||||

- BOOTMODE[2:0]– Denote system clock frequency for PLL configuration.

- The below table gives the details of PLL reference clock selection.

| SW4.3 | SW4.2 | SW4.1 | PLL REF CLK (MHz) |

|---|---|---|---|

| OFF | OFF | OFF | 19.2 |

| OFF | OFF | ON | 20 |

| OFF | ON | OFF | 24 |

| OFF | ON | ON | 25 |

| ON | OFF | OFF | 26 |

| ON | OFF | ON | 27 |

| ON | ON | OFF | RSVD |

| ON | ON | ON | RSVD |

- BOOTMODE[6:3] – This provides primary boot mode configuration to select the requested boot mode after POR, that is, the peripheral/memory to boot from primary boot device selection details.

| SW4.7 | SW4.6 | SW4.5 | SW4.4 | Primary Boot Device Selected |

|---|---|---|---|---|

| OFF | OFF | OFF | OFF | Serial NAND |

| OFF | OFF | OFF | ON | OSPI |

| OFF | OFF | ON | OFF | QSPI |

| OFF | OFF | ON | ON | SPI |

| OFF | ON | OFF | OFF | Ethernet RGMII |

| OFF | ON | OFF | ON | Ethernet RMII |

| OFF | ON | ON | OFF | I2C |

| OFF | ON | ON | ON | UART |

| ON | OFF | OFF | OFF | MMC/SD card |

| ON | OFF | OFF | ON | eMMC |

| ON | OFF | ON | OFF | USB0 |

| ON | OFF | ON | ON | GPMC NAND |

| ON | ON | OFF | OFF | GPMC NOR |

| ON | ON | OFF | ON | Rsvd |

| ON | ON | ON | OFF | xSPI |

| ON | ON | ON | ON | No boot/Dev Boot |

- BOOTMODE[12:10] – Select the backup boot mode, that is, the peripheral/memory to boot from, if primary boot device failed.

| SW5.5 | SW5.4 | SW5.3 | Backup Boot Device Selected |

|---|---|---|---|

| OFF | OFF | OFF | None (No backup mode) |

| OFF | OFF | ON | USB |

| OFF | ON | OFF | Reserved |

| OFF | ON | ON | UART |

| ON | OFF | OFF | Ethernet |

| ON | OFF | ON | MMC/SD |

| ON | ON | OFF | SPI |

| ON | ON | ON | I2C |

- BOOTMODE[9:7] – These pins provide optional settings and are used in conjunction with the primary boot device selected.

| SW5.2 | SW5.1 | SW4.8 | Boot Device |

|---|---|---|---|

| Reserved | Read Mode 2 | Read Mode 1 | Serial NAND |

| Reserved | Iclk | Csel | QSPI |

| Reserved | Iclk | Csel | OSPI |

| Reserved | Mode | Csel | SPI |

| Clkout | 0 | Link Info | Ethernet RGMII |

| Clkout | Clk src | 0 | Ethernet RMII |

| Bus Reset | Reserved | Addr | I2C |

| Reserved | Reserved | Reserved | UART |

| 1 | Reserved | Fs/raw | MMC/ SD card |

| Reserved | Reserved | Reserved | eMMC |

| Core Volt | Mode | Lane swap | USB0 |

| Reserved | Reserved | Reserved | GPMC NAND |

| Reserved | Reserved | Reserved | GPMC NOR |

| Reserved | Reserved | Reserved | Reserved |

| SFPD | Read Cmd | Mode | xSPI |

| Reserved | ARM/Thumb | No/Dev | No boot/Dev Boot |

- BOOTMODE[13] – These pins provide optional settings and are used in conjunction with the backup boot device devices. Switch SW 3.6 when ON sets 1 and sets 0 if OFF, see the device specific TRM.

- BOOT-MODE[15:14] – Reserved. Provides backup boot media configuration options.