TIDT320A january 2023 – july 2023

3.6 Load Regulation

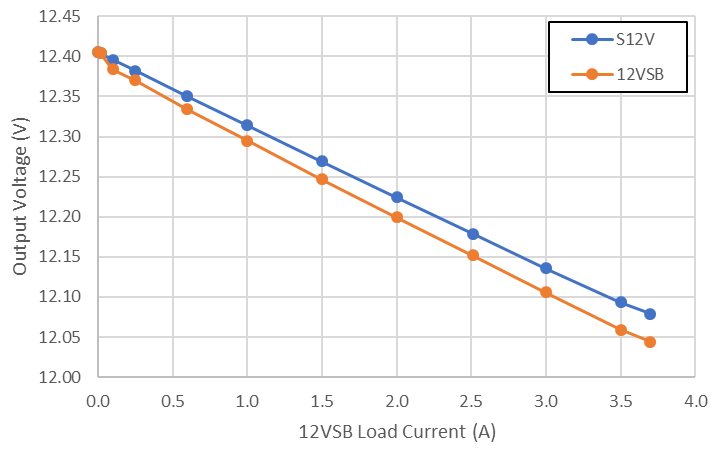

The data from the 390 VDC input efficiency measurements was used to generate the 12VSB and S12V regulation plot shown in Figure 3-27. No additional loading was applied to P18V and S12V.

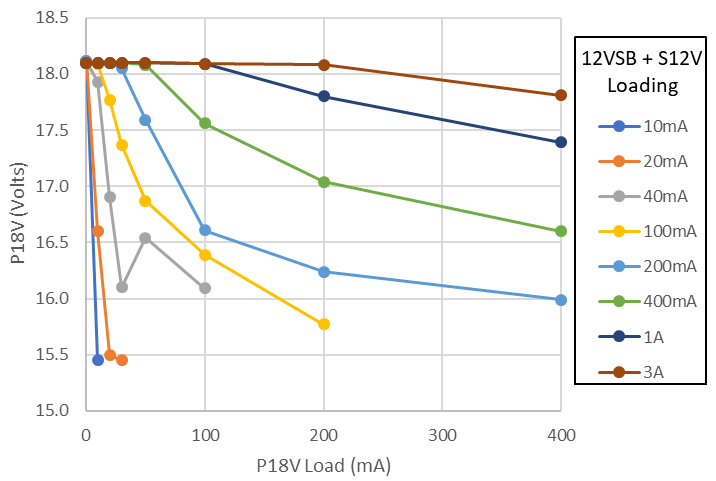

The second plot (Figure 3-10) shows the voltage measured on P18V for different loading combinations on all outputs.

Figure 3-9 12VSB and S12V Output Voltage

Regulation

Figure 3-9 12VSB and S12V Output Voltage

Regulation Figure 3-10 P18V Output Voltage Regulation

Figure 3-10 P18V Output Voltage Regulation