TIDUE53I march 2018 – july 2023 TMS320F28P550SJ , TMS320F28P559SJ-Q1

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1 Required Hardware and Software

- 3.2 Testing and Results

- 4Design Files

- 5Trademarks

- 6About the Authors

- 7Revision History

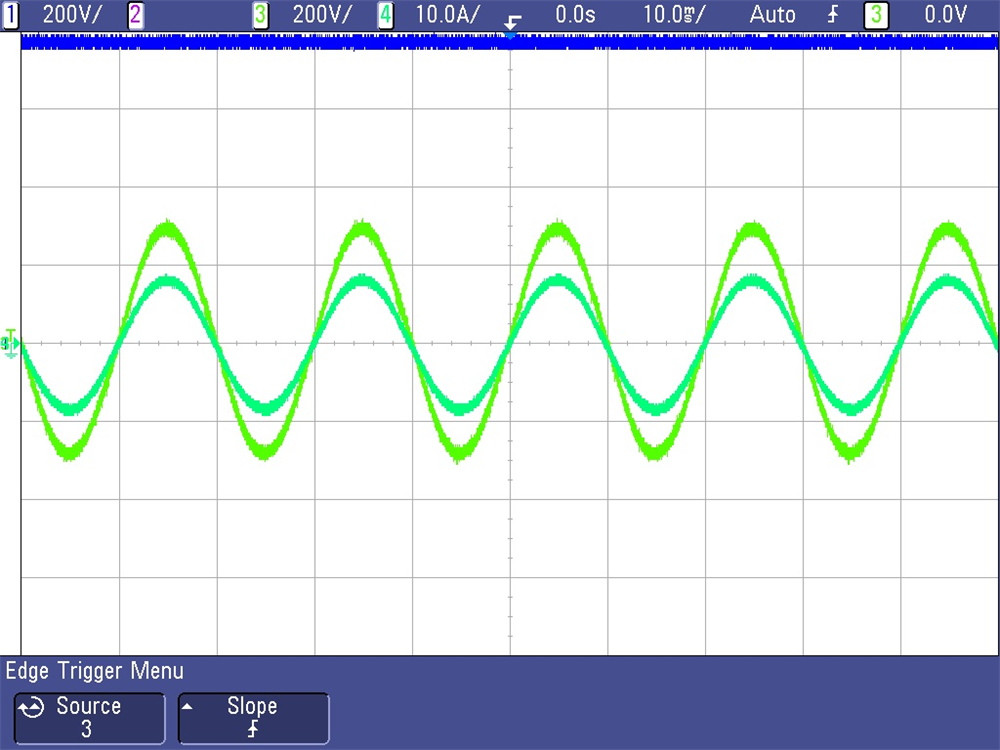

3.2.5.3.1 Inverter Closed Loop Results

The inverter is tested in the closed current loop in Lab 3 where the current reference is varied by changing the variable TINV_idRef_pu from the watch window. Setting this value to around 0.35 pu should deliver around 3.5 kW of power at the AC terminals. Figure 3-51 shows closed current loop operation and the efficiency results obtained. Scope signals: Channel 1 - DC link voltage (blue), Channel 2 - AC voltage (light green), Channel 3 - AC current (dark green).

Figure 3-51 Inverter Closed Current Loop Waveforms

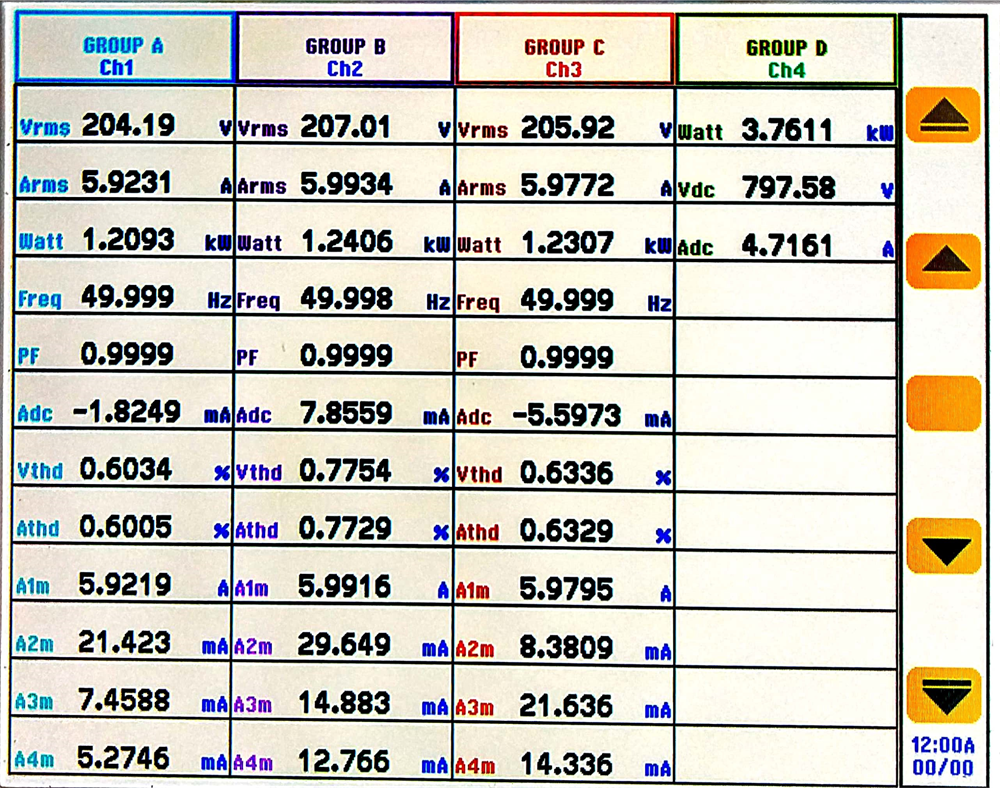

Figure 3-51 Inverter Closed Current Loop WaveformsFigure 3-52 shows power key efficiency and THD figures captured with power analyzer at 3.8 kW.

Figure 3-52 Inverter Closed Current Loop Results

Figure 3-52 Inverter Closed Current Loop Results