SLAAE74A December 2022 – March 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507 , MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1305 , MSPM0L1306 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

- Abstract

- Trademarks

- 1Software Porting Flow

- 2Development Environments

- 3Migration Considerations

- 4Revision History

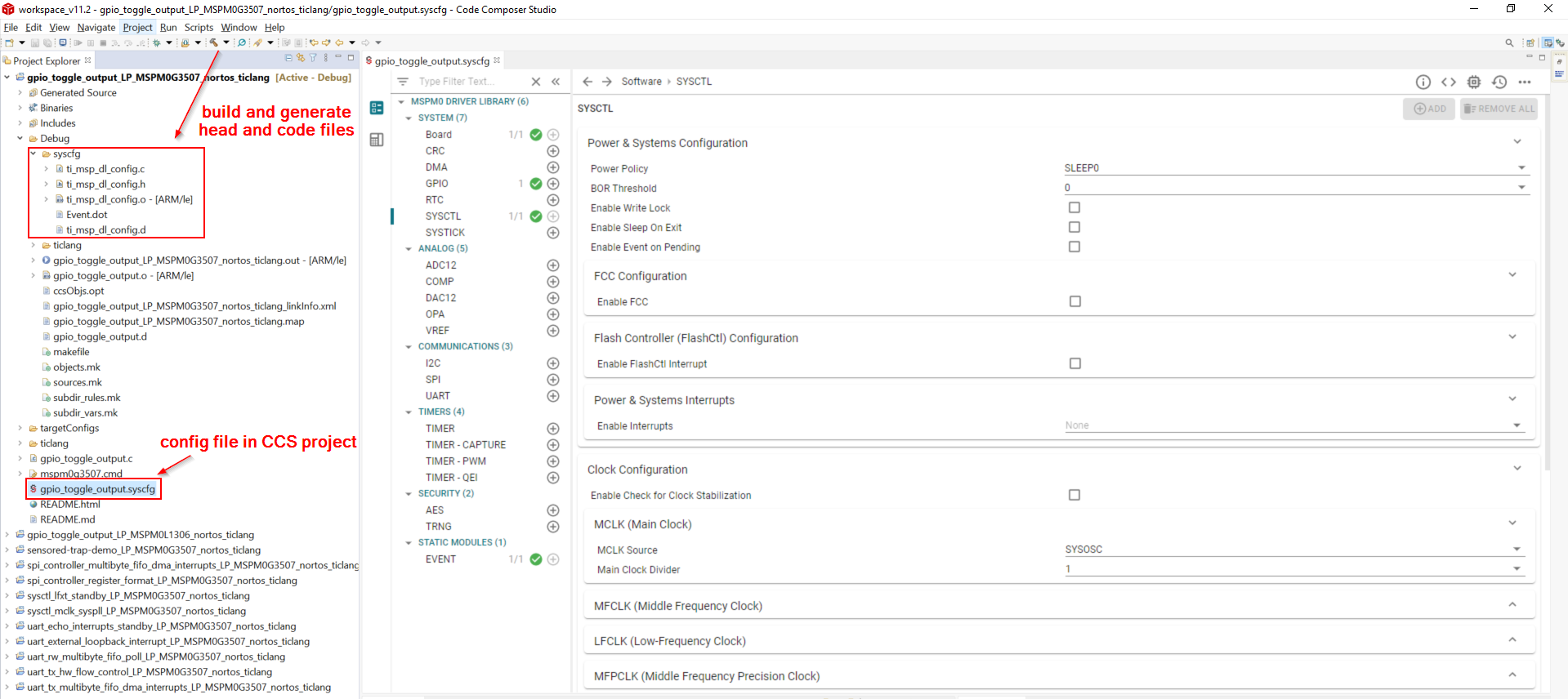

2.3.3 Example of a SysConfig Project

In the toggle output example project shown in #GUID-36995428-80D9-4006-A379-6717B352C160, the configuration file is included in the project. When the project is built, CCS generates the configuration header and code files based on the configuration file. In this project, the GPIOs and system clock are configured. For further development, open the SysConfig file in CCS and modify the peripherals as needed. The header and code files are updated when the project is built.

Figure 2-5 SysConfig Project With CCS

Figure 2-5 SysConfig Project With CCS