SLAAE75A November 2022 – March 2023 MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

9.3 Traces, Vias, and Other PCB Components

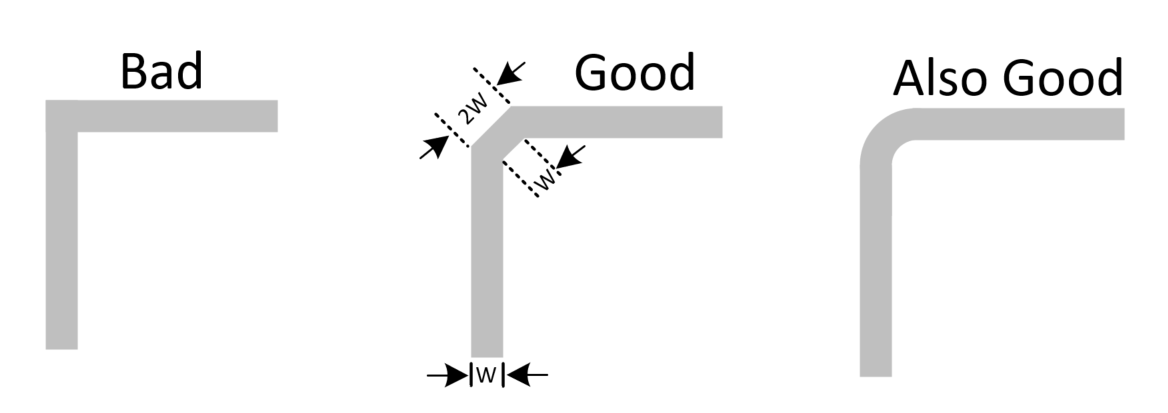

A right angle in a trace can cause more radiation. The capacitance increases in the region of the corner and the characteristic impedance changes. This impedance change causes reflections. Avoid right-angle bends in a trace and try to route them with at least two 45° corners. To minimize any impedance change, the best routing would be a round bend, as shown in #FIG_WT4_PQB_GVB.

Figure 9-3 Poor and Correct Way of Bending Traces in Right Angle

Figure 9-3 Poor and Correct Way of Bending Traces in Right AngleTo minimize crosstalk, not only between two signals on one layer but also between adjacent layers, route them 90° to each other. More complex boards need to use vias while routing; however, care must be taken when using vias as they add additional inductance and capacitance, and reflections occur due to the change in the characteristic impedance. Vias also increase the trace length. When using differential signals, use vias in both traces or compensate the delay in the other trace as well.

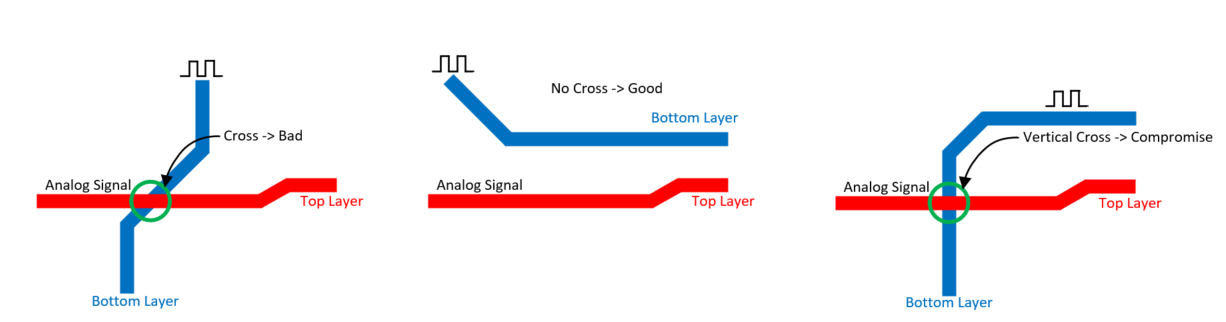

For signal traces, pay more attention to the impact of high-frequency pulse signals, especially on relatively small analog signals (like sensor signals). Too many crossovers will couple the electromagnetic noise of the high-frequency signal to the analog signal, which will result in a low signal-to-noise ratio of the signal and affect the signal quality. Therefore, it is necessary to avoid crossing when designing. But if there is indeed an unavoidable intersection, it is recommended to intersect vertically to minimize the interference of electromagnetic noise. #FIG_GK3_RQB_GVB shows how to reduce this noise.

Figure 9-4 Poor and Correct Cross Traces for Analog and High-Frequency Signals

Figure 9-4 Poor and Correct Cross Traces for Analog and High-Frequency Signals