SLAAE75A November 2022 – March 2023 MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

4.2 External Clock Output (CLK_OUT)

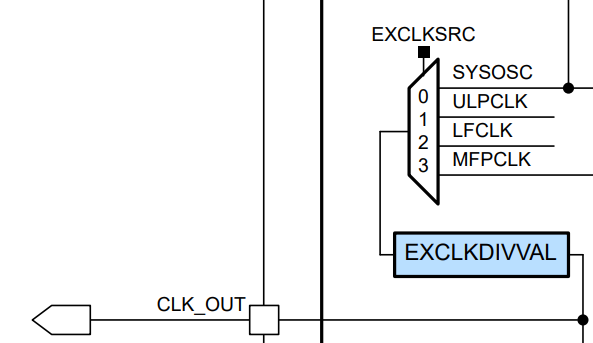

A clock output unit is provided for pushing out digital clocks from the device to external circuits or to the frequency clock counter. This feature is useful for clocking external circuitry such as an external ADC that does not have its own clock source. The clock output unit has a flexible set of sources to select from and includes a programmable divider.

Figure 4-3 MSPM0L Series External Clock Output

Figure 4-3 MSPM0L Series External Clock OutputAvailable clock sources for CLK_OUT:

- SYSOSC

- ULPCLK

- MFCLK

- LFCLK

The selected clock source is divided by 1, 2, 4, 8, 16, 32, 64, or 128 before being output to the pin or to the frequency clock counter.