SLVUC73B January 2022 – February 2024 TPS7H4003-SEP

7 Board Layout

The following is the layer stack of the TPS7H4003EVM board.

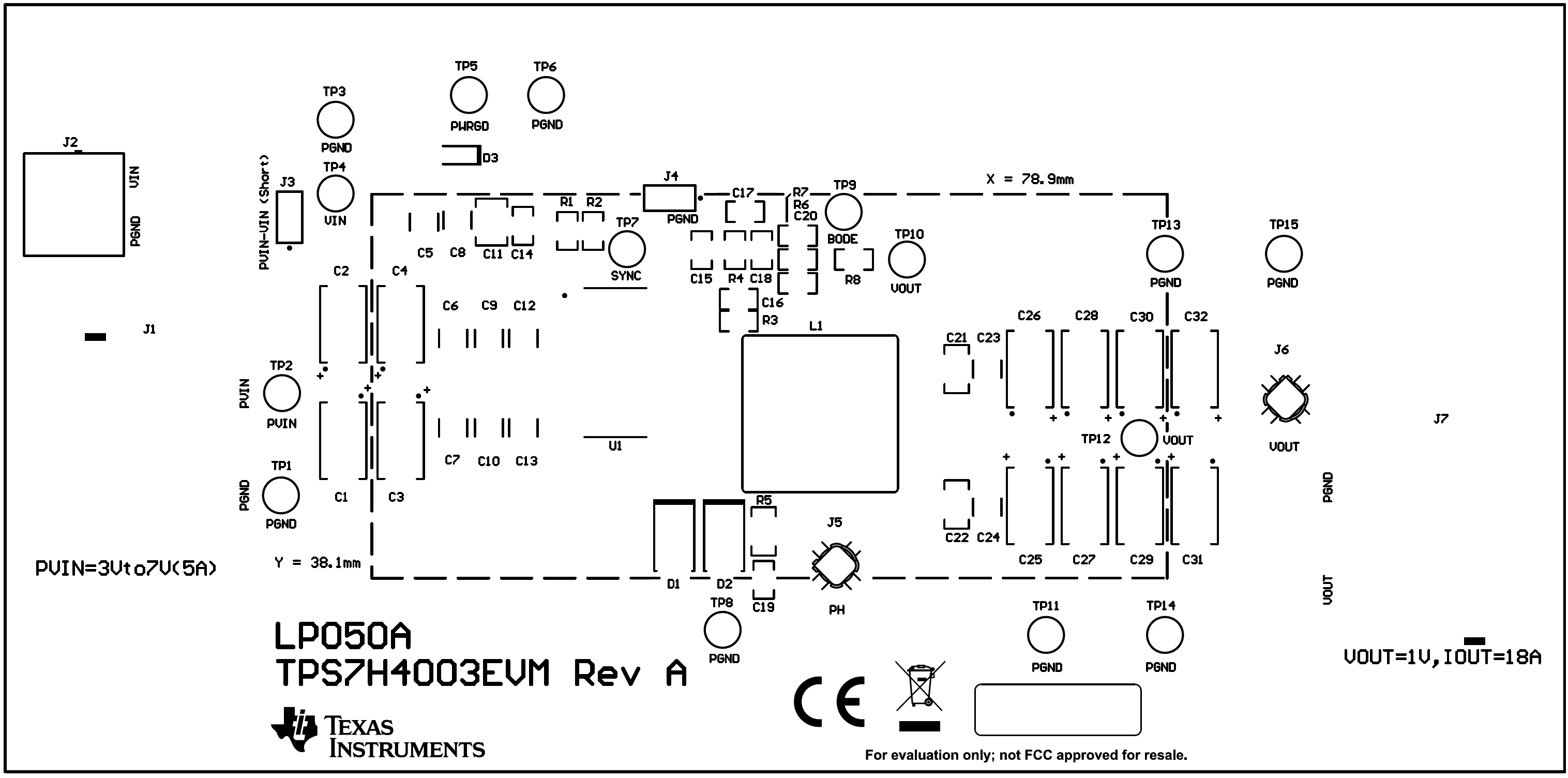

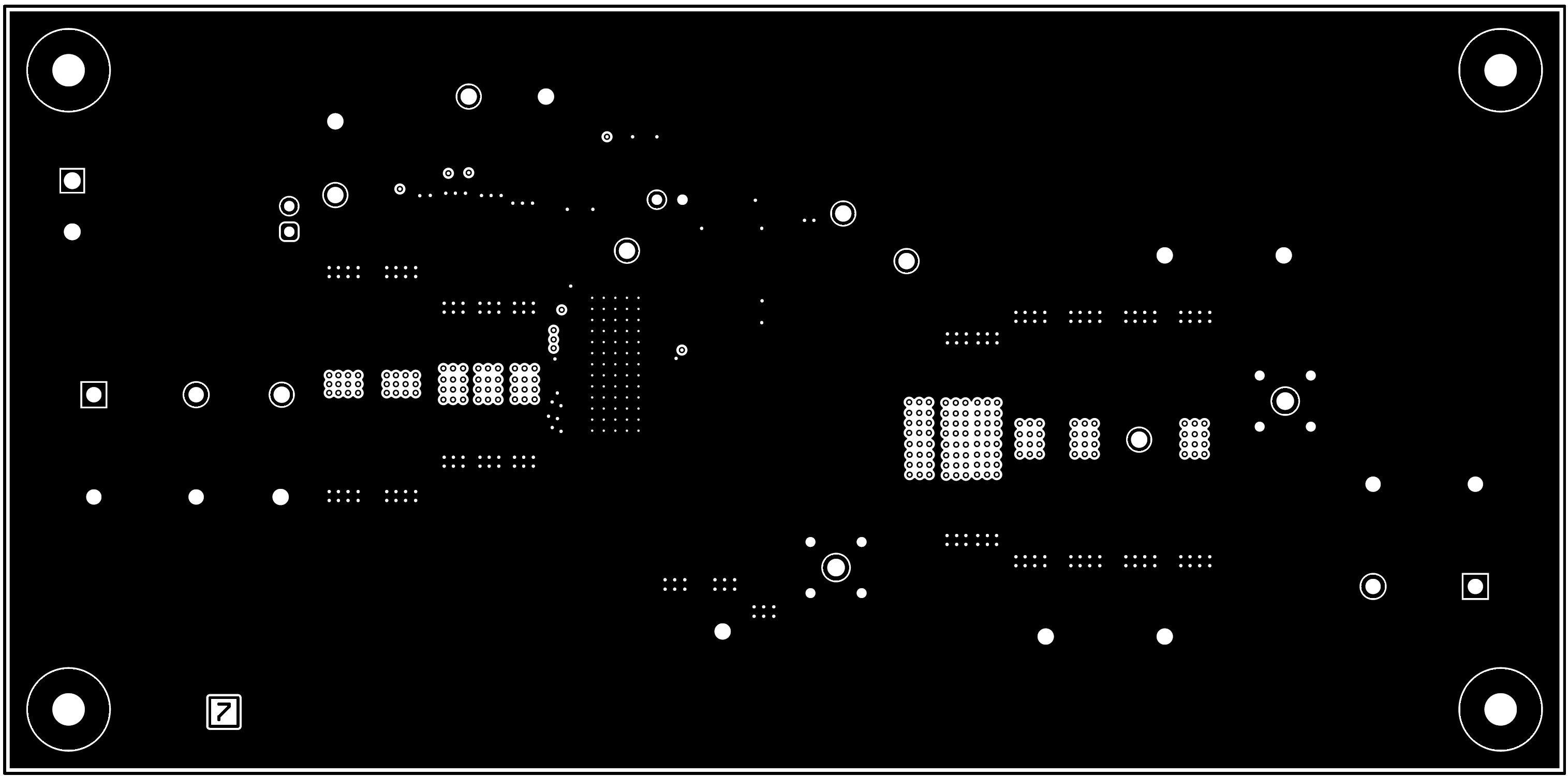

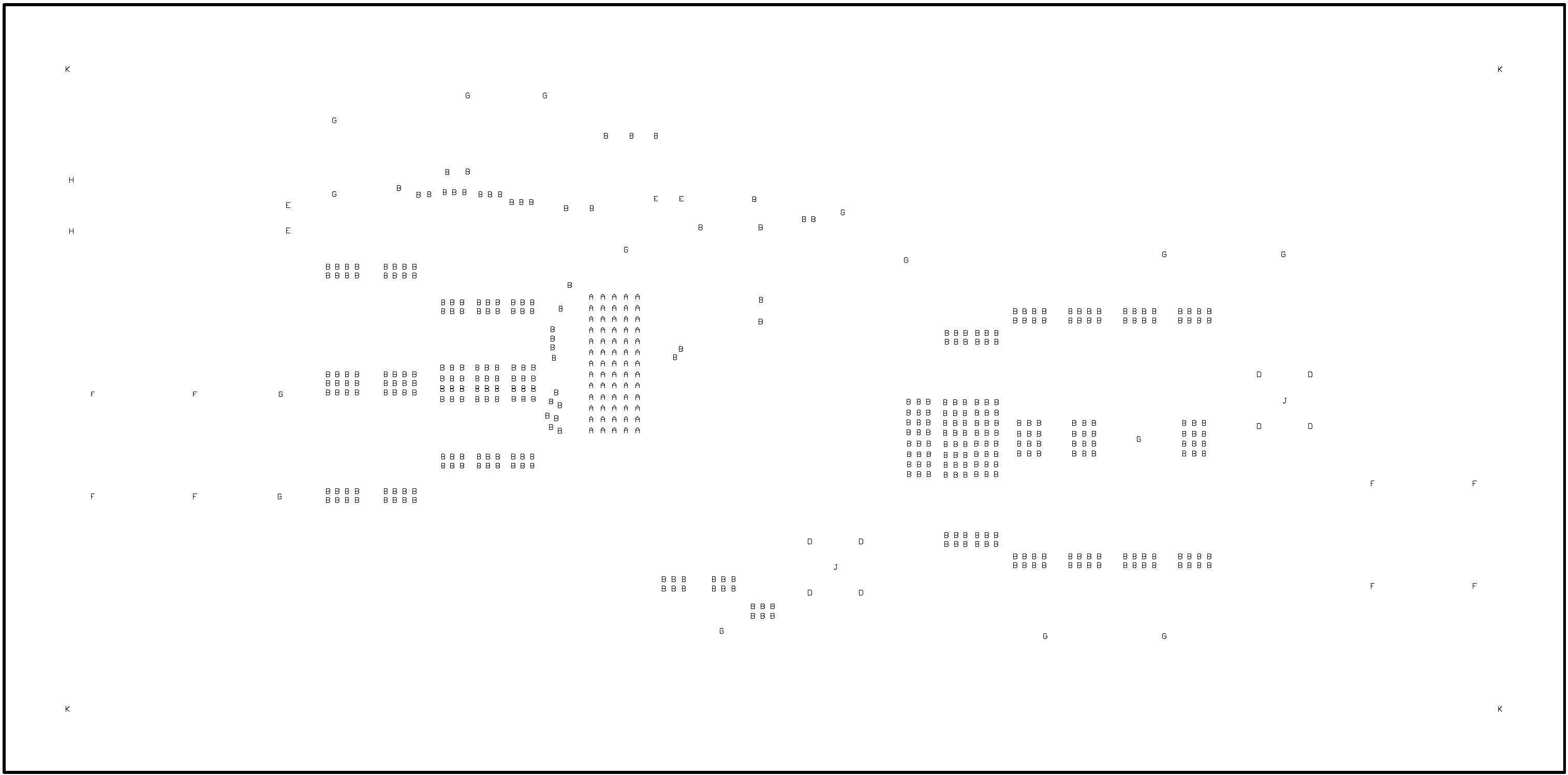

Figure 7-1 Top Overlay

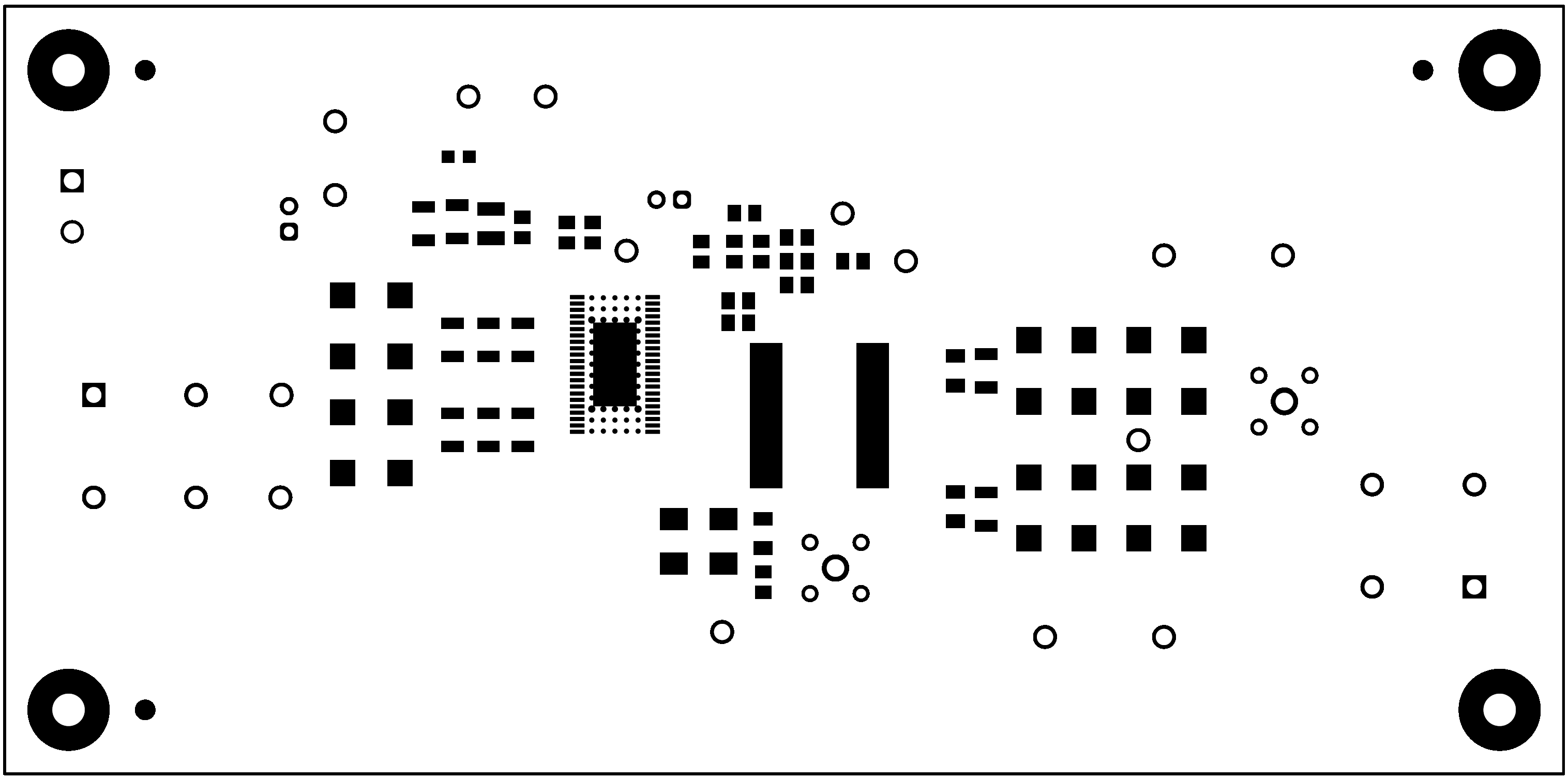

Figure 7-1 Top Overlay Figure 7-2 Top Solder

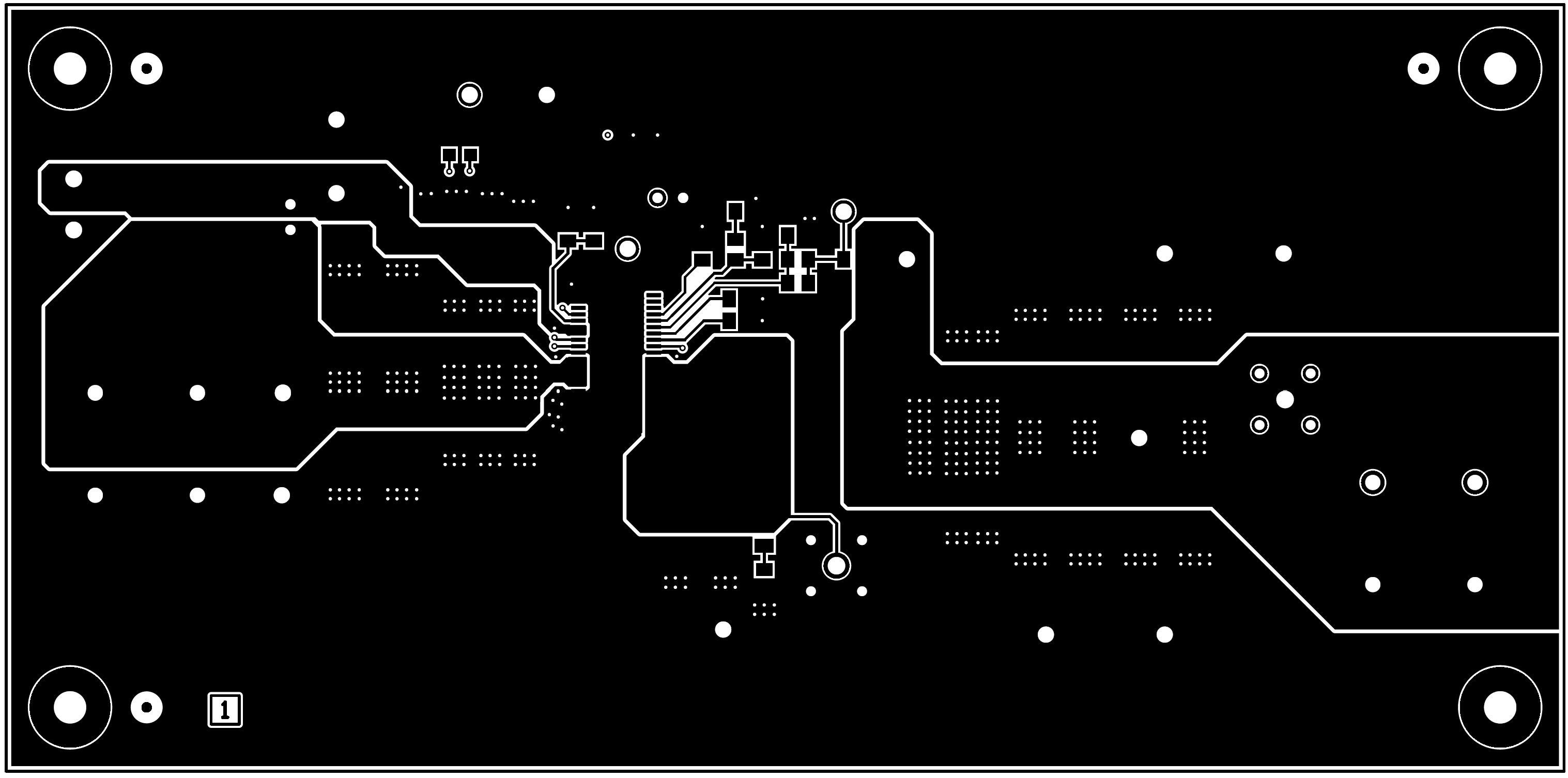

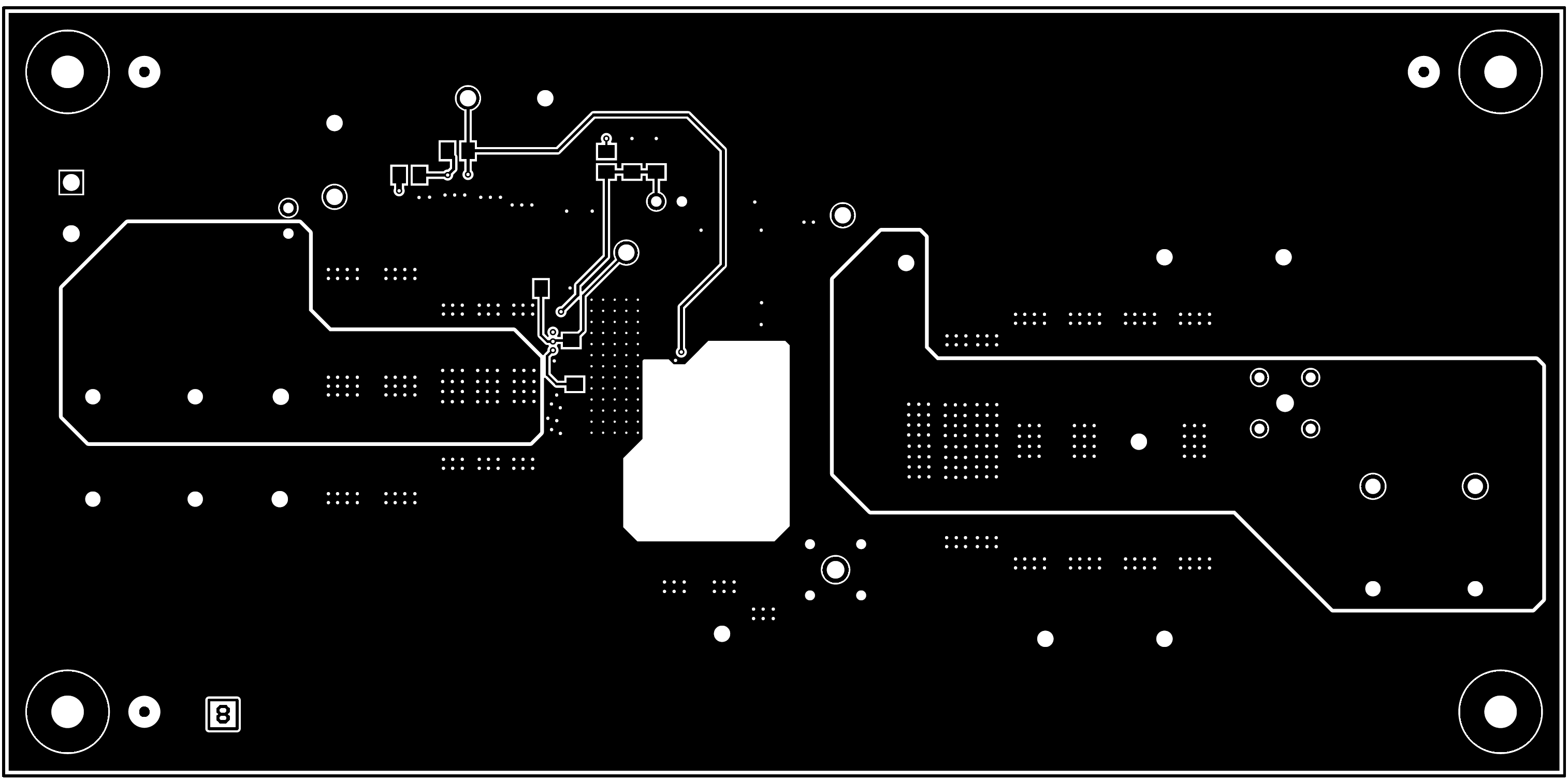

Figure 7-2 Top Solder Figure 7-3 Top Layer

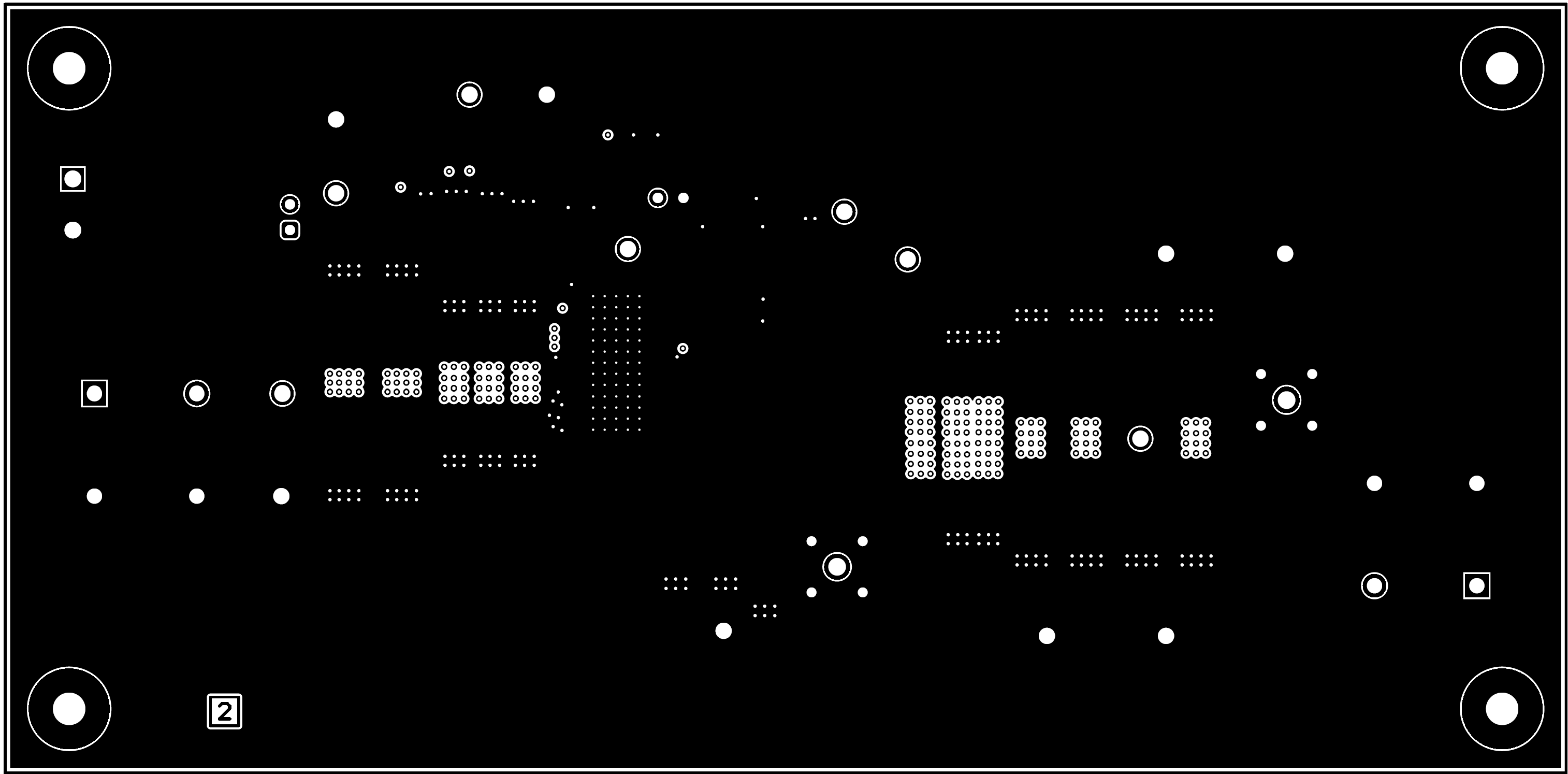

Figure 7-3 Top Layer Figure 7-4 Signal Layer One

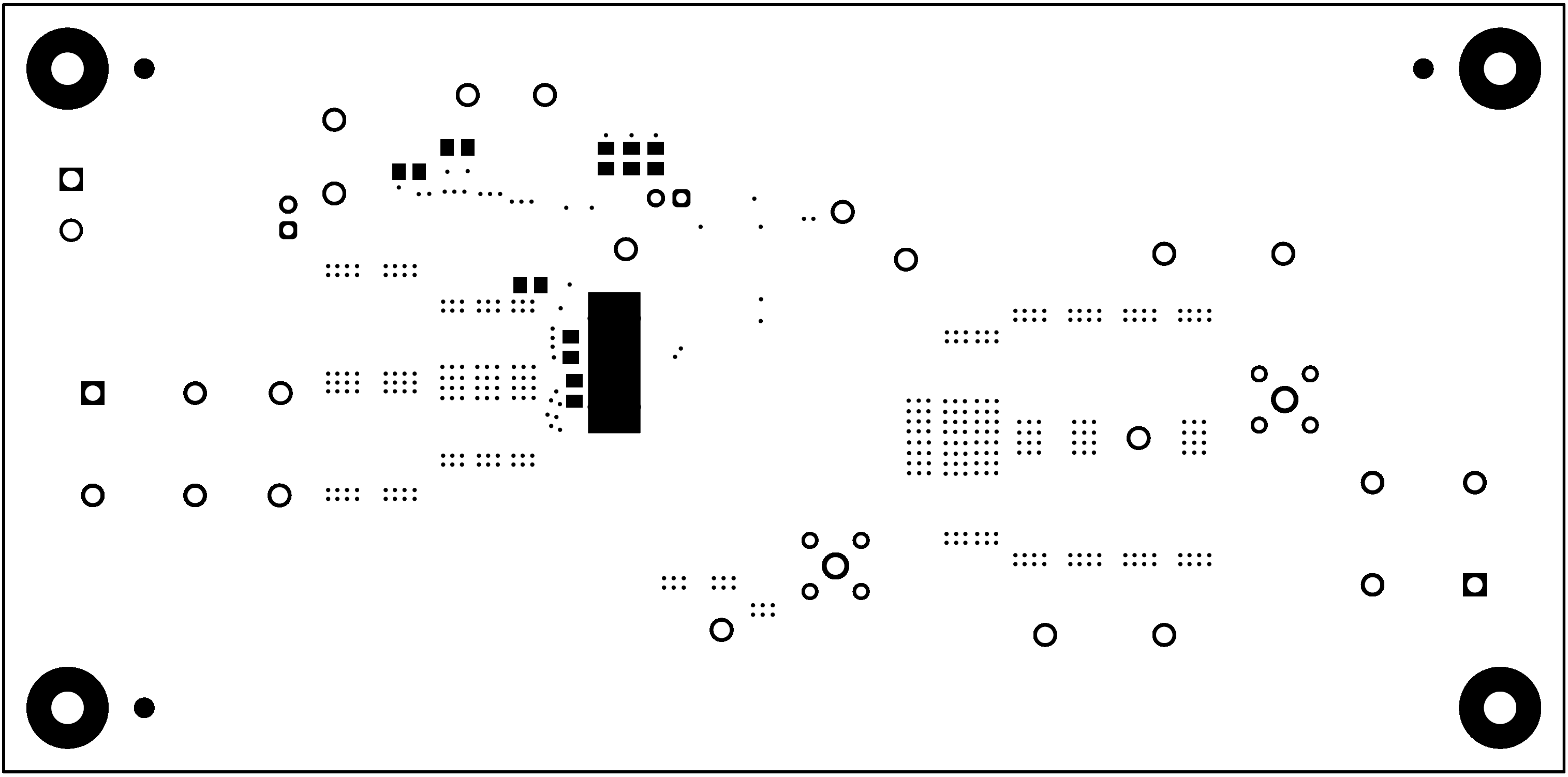

Figure 7-4 Signal Layer One Figure 7-5 Signal Layer Two

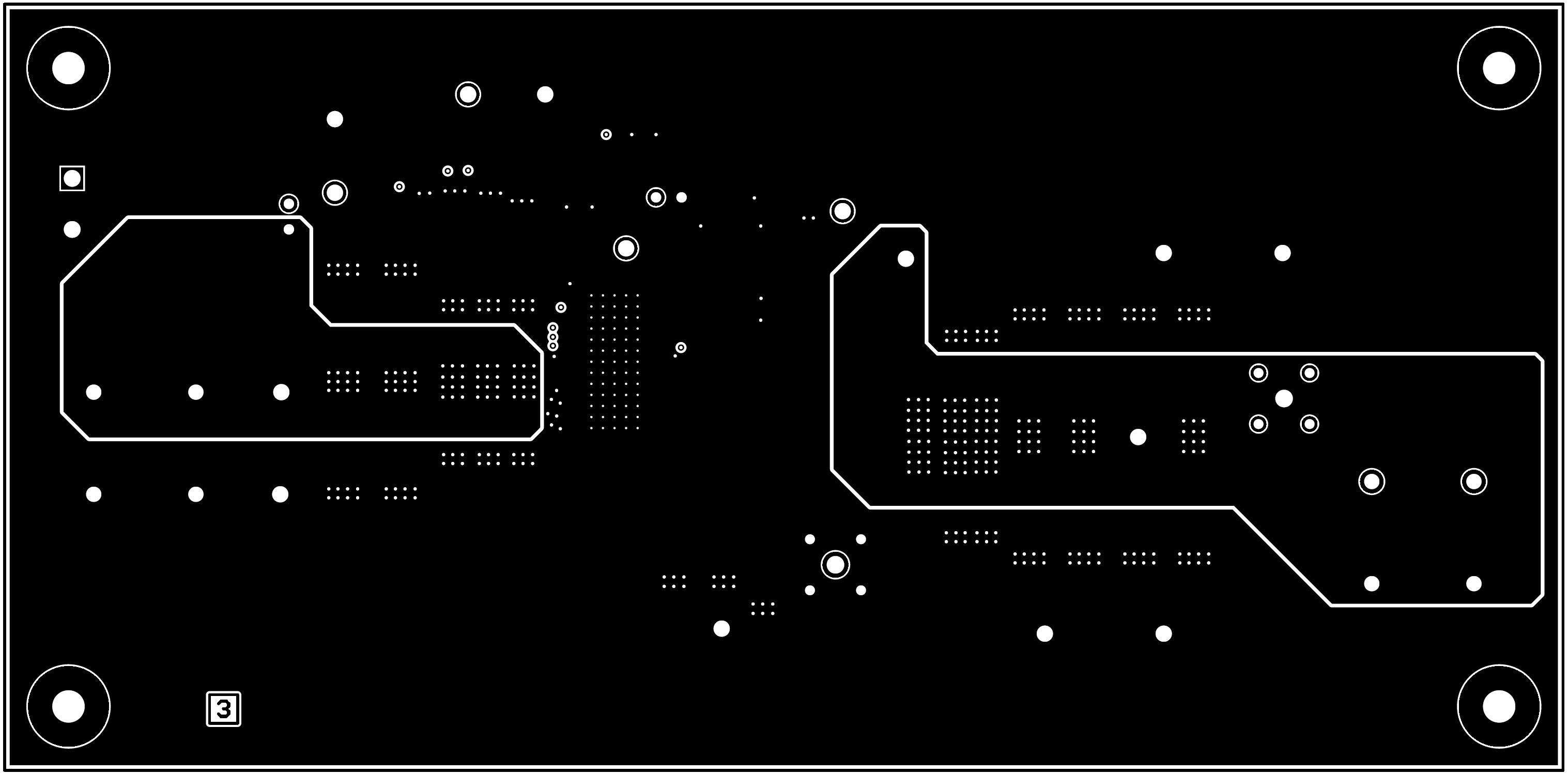

Figure 7-5 Signal Layer Two Figure 7-6 Signal Layer Three

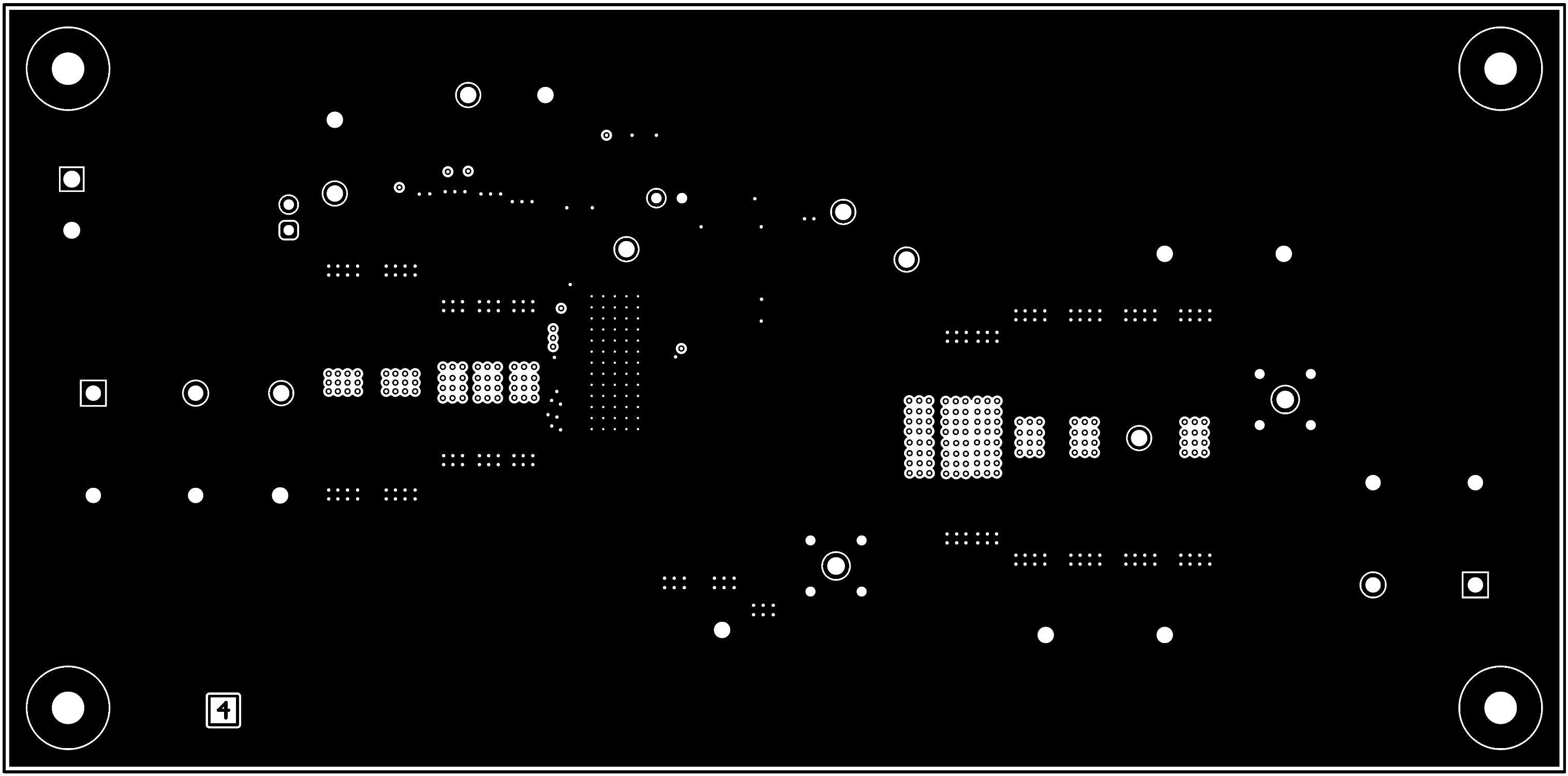

Figure 7-6 Signal Layer Three Figure 7-7 Signal Layer Four

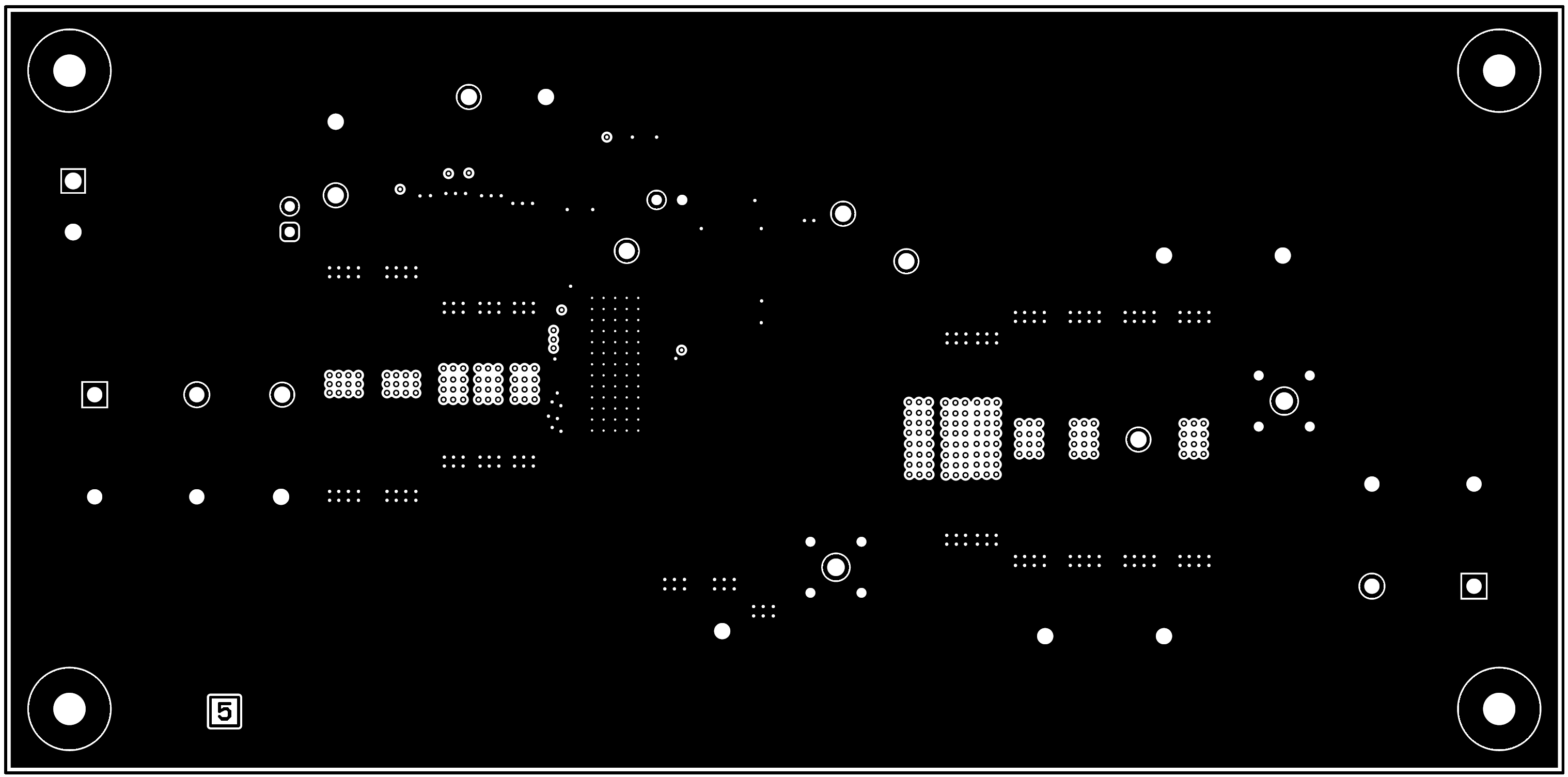

Figure 7-7 Signal Layer Four Figure 7-8 Signal Layer Five

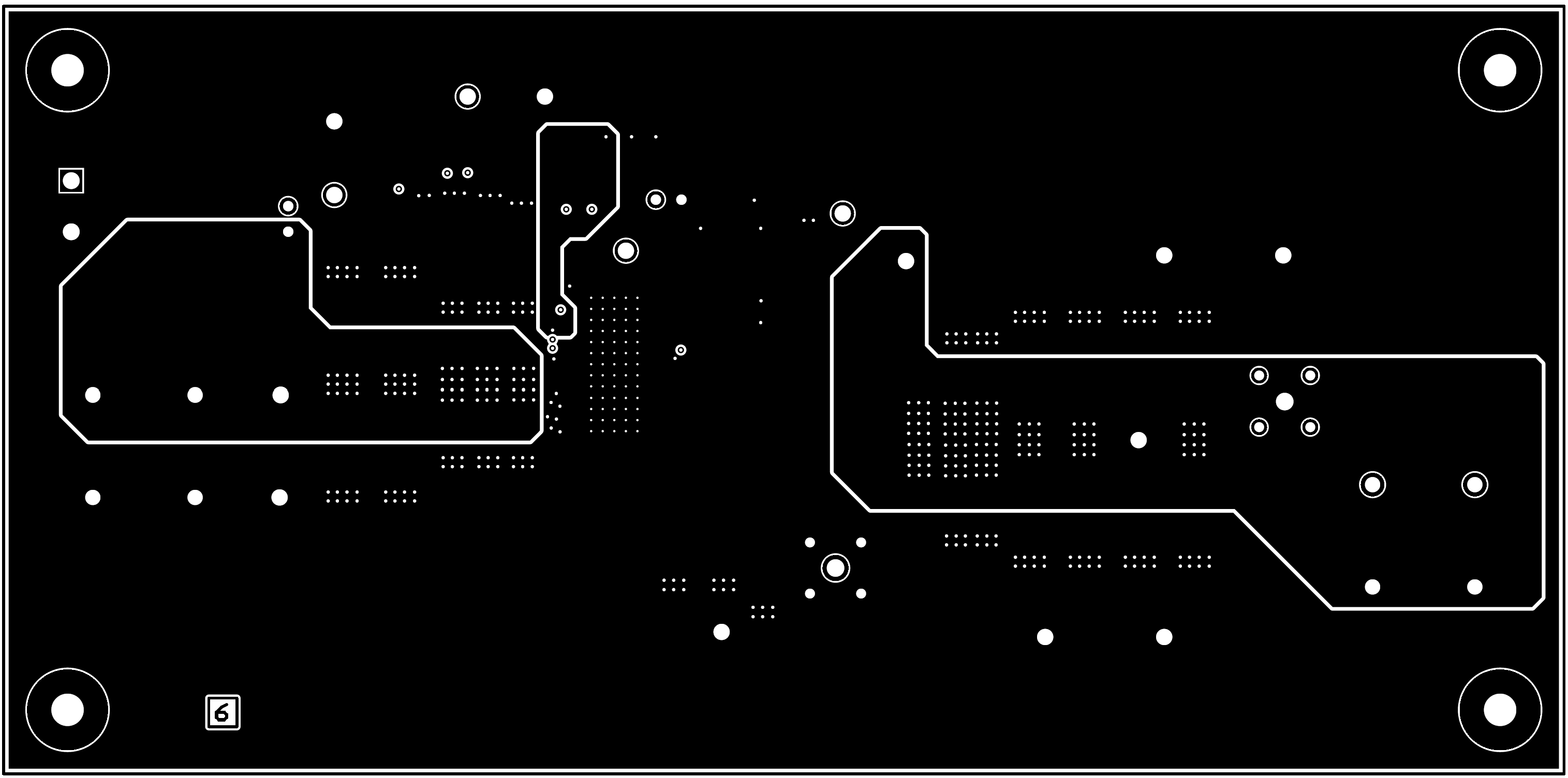

Figure 7-8 Signal Layer Five Figure 7-9 Signal Layer Six

Figure 7-9 Signal Layer Six Figure 7-10 Bottom Layer

Figure 7-10 Bottom Layer Figure 7-11 Bottom Solder

Figure 7-11 Bottom Solder Figure 7-12 Bottom Overlay

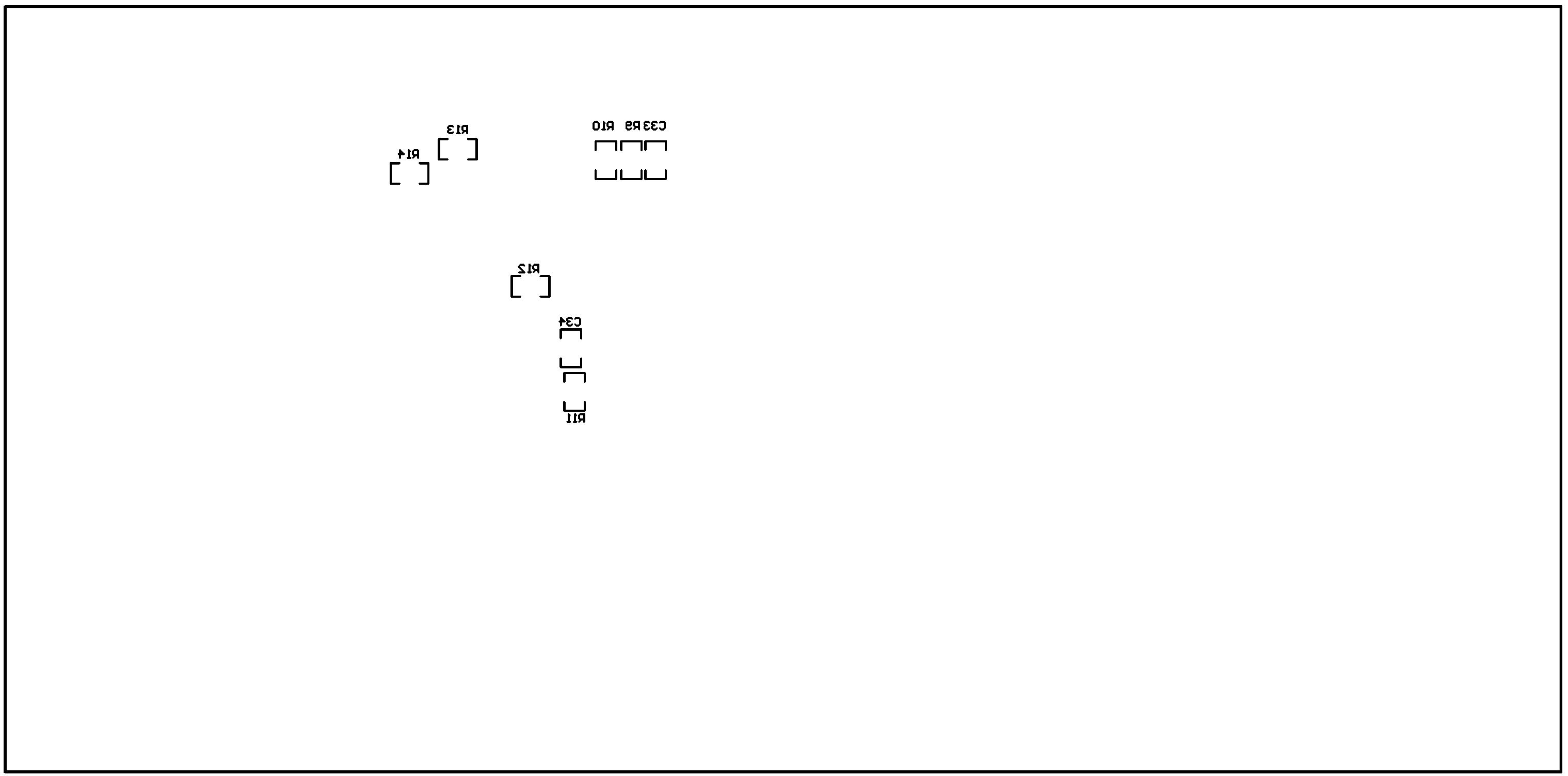

Figure 7-12 Bottom Overlay Figure 7-13 Drill Drawing

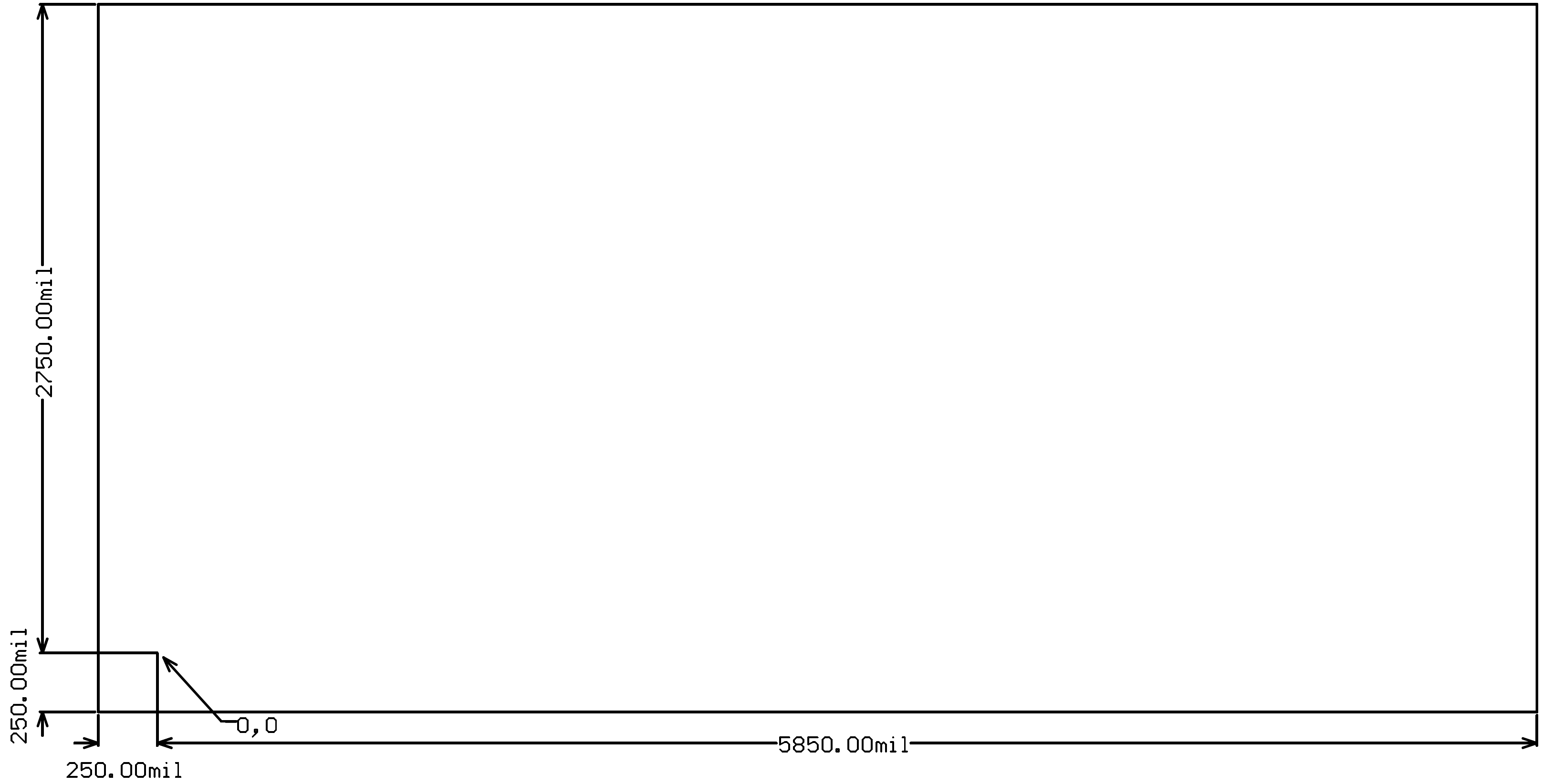

Figure 7-13 Drill Drawing Figure 7-14 PCB Dimensions

Figure 7-14 PCB Dimensions