SNLA421 December 2022 DS320PR810 , SN75LVPE5412 , SN75LVPE5421

1.1 Add-in-Card (AIC) Form Factor

To participate in system and electrical testing, the redrivers were designed onto an AIC which can also accommodate a standard PCIe endpoint which is compliant to the PCIe standard. This endpoint acts as the redrivers test partner; the test partner is used to transmit compliant PCIe Tx presets, perform loopback, and inter operate with Host system components. The redriver and the AIC to which the redriver is mounted must be designed to allow any and all normal PCIe link configuration and activity. This design includes some of the following items:

- Receiver Detection

- PCIe Reset

- PCIe Speed Changes

- Equalization Link Training

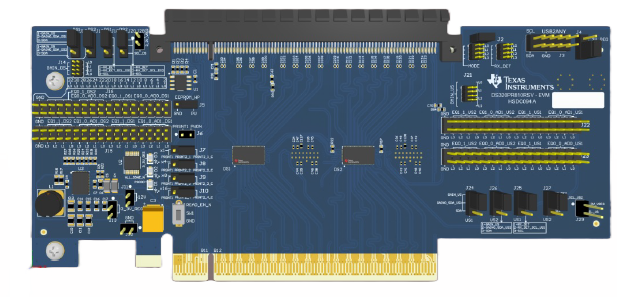

Figure 1-1 DS320PR810 Riser Card EVM