SPRAD65 December 2022 TDA4VM , TDA4VM-Q1

3 Demo Verify

- Make a pre-build SD card:

- ti-processor-sdk-rtos-j721e-evm-07_01_00_11-prebuilt$ sudo ./mk-linux-card.sh /dev/sdc

- ti-processor-sdk-rtos-j721e-evm-07_01_00_11-prebuilt$./install_to_sd_card

- ti-processor-sdk-rtos-j721e-evm-07_01_00_11-prebuilt$./install_data_set_to_sd_card.sh ../psdk_rtos_ti_data_set_07_01_00.tar.gz

- Save the previous changes,

compile the SDK, and update the SD card:

- ti-processor-sdk-rtos-j721e-evm-07_01_00_11/vision_apps$ make sdk -j8

- ti-processor-sdk-rtos-j721e-evm-07_01_00_11/vision_apps$ make linux_fs_install_sd

- ti-processor-sdk-linux-j7-evm-07_01_00_10$ make all -j8

- ti-processor-sdk-linux-j7-evm-07_01_00_10$ make install

- ti-processor-sdk-linux-j7-evm-07_01_00_10$ cp ./targetNFS/boot/* /media/$USER/rootfs/boot/

- Download the mobileNetv1 model for test:

- Copy the model to the

corresponding directory to generate a model format that TIDL can execute:

- ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/test/testvecs/models/public/caffe$ mkdir mobileNet1.0v1&&cd mobileNet1.0v1/

- cp ~/Desktop/MobileNet-Caffe/mobilenet.caffemodel ./

- cp ~/Desktop/MobileNet-Caffe/mobilenet_deploy.prototxt ./

- ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/utils/tidlModelImport$ ./out/tidl_model_import.out ../../../ti_dl/test/testvecs/config/import/public/caffe/tidl_import_mobilenet_v1.txt

Caffe Network File : ../../test/testvecs/models/public/caffe/mobileNet1.0v1/mobilenet_deploy.prototxt Caffe Model File : ../../test/testvecs/models/public/caffe/mobileNet1.0v1/mobilenet.caffemodel TIDL Network File : ../../test/testvecs/config/tidl_models/caffe/tidl_net_mobilenet_v1.bin TIDL IO Info File : ../../test/testvecs/config/tidl_models/caffe/tidl_io_mobilenet_v1_ Name of the Network : MOBILENET ~~~~~Running TIDL in PC emulation mode to collect Activations range for each layer~~~~~ Processing config file #0 : /home/test/Desktop/pc_disk/ti_sdk/TDA4VM/ti-7.1/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/test/testvecs/config/tidl_models/caffe/tidl_import_mobilenet_v1.txt.qunat_stats_config.txt ----------------------- TIDL Process with REF_ONLY FLOW ------------------------ # 0 . .. T 280.71 .... ..... ... A : 895, 1.0000, 1.0000, 895 .... ..... # 1 . .. T 279.96 .... ..... ... A : 557, 0.5000, 0.5000, 829 .... ..... # 2 . .. T 263.92 .... ..... ... A : 442, 0.3333, 0.3333, 829 .... ..... # 3 . .. T 260.39 .... ..... ... A : 498, 0.2500, 0.2500, 751 .... ..... ~~~~~Running TIDL in PC emulation mode to collect Activations range for each layer~~~~~ Processing config file #0 : /home/test/Desktop/pc_disk/ti_sdk/TDA4VM/ti-7.1/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/test/testvecs/config/tidl_models/caffe/tidl_import_mobilenet_v1.txt.qunat_stats_config.txt ----------------------- TIDL Process with REF_ONLY FLOW ------------------------ # 0 . .. T 566.09 .... ..... ... A : 895, 1.0000, 1.0000, 895 .... ..... # 1 . .. T 556.95 .... ..... ... A : 557, 0.5000, 1.0000, 733 .... ..... # 2 . .. T 553.00 .... ..... ... A : 442, 0.3333, 0.6667, 675 .... ..... # 3 . .. T 559.57 .... ..... ... A : 498, 0.2500, 0.5000, 833 .... ..... ***************** Calibration iteration number 0 completed ************************ ------------------ Network Compiler Traces ----------------------------- successful Memory allocation **************************************************** ** ALL MODEL CHECK PASSED ** **************************************************** - Copy the newly generated model to

the board side:

- cp ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/test/testvecs/config/tidl_models/caffe/ tidl_io_mobilenet_v1_1.bin /media/$USER/rootfs/opt/vision_apps/test_data/tivx/tidl_models/

- cp ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/test/testvecs/config/tidl_models/caffe/ tidl_net_mobilenet_v1.bin /media/$USER/rootfs/opt/vision_apps/test_data/tivx/tidl_models/

- Run demo on TDA4EVM:

- cd /opt/vision_apps

- source ./vision_apps_init.sh

- ./run_app_tidl.sh

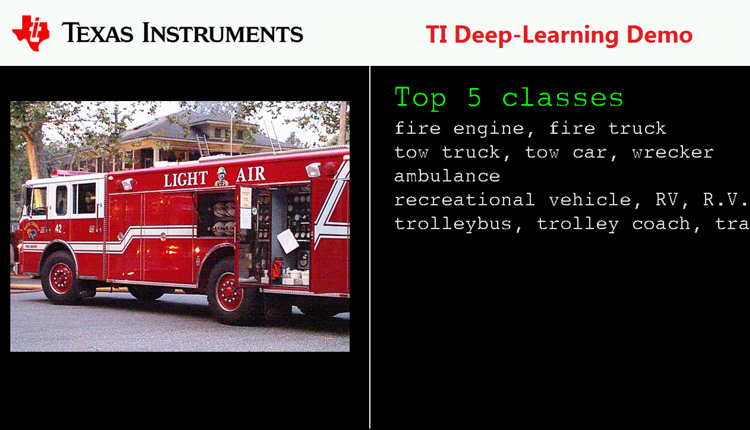

Figure 3-1 Image Classification

Result

Figure 3-1 Image Classification

Result