SPRUJ10D May 2022 – September 2023

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Kit Overview

- 3Board Setup

-

4Hardware Description

- 5.1 Functional Block Diagram

- 5.2 GPIO Mapping

- 5.3 Reset

- 5.4 Clock

- 5.5 Memory Interface

- 5.6 Ethernet Interface

- 5.7 I2C

- 5.8 Industrial Application LEDs

- 5.9 SPI

- 5.10 UART

- 5.11 MCAN

- 5.12 FSI

- 5.13 JTAG

- 5.14 Test Automation Header

- 5.15 LIN

- 5.16 MMC

- 5.17 ADC and DAC

- 5.18 EQEP and SDFM

- 5.19 EPWM

- 5.20 BoosterPack Headers

- 5.21 Pinmux Mapping

- 5References

- 6Revision History

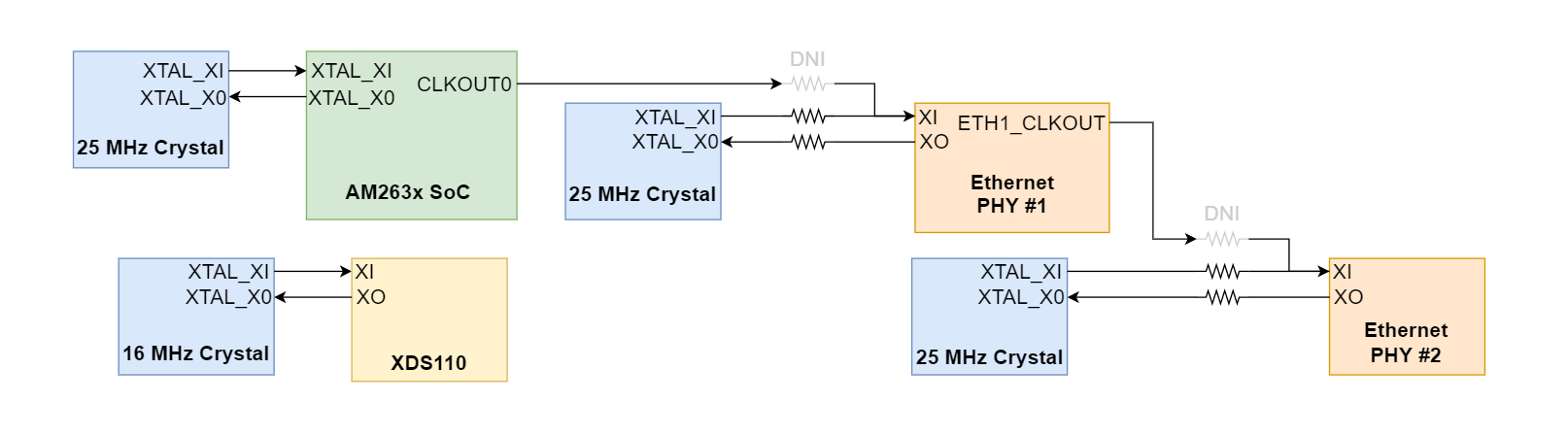

4.4 Clock

The AM263x SoC requires a 25MHz clock input for XTAL_XI. The AM263x LaunchPad uses a 25MHz crystal for the SoC clock source. The LaunchPad also has two 25MHz Crystals on-board for the Ethernet PHY clocking. The SoC clock signal output CLKOUT0 can be used as a clock source for Ethernet PHY #1 by removing the resistors mounted for XTAL_XI and XTAL_XO from the 25MHz Ethernet PHY #1 Crystal and mounting the appropriate resistor for the CLKOUT0 signal to be routed to the XI pin of the Ethernet PHY.

The Ethernet PHY #1 clock signal output ETH1_CLKOUT can be used as a clock source for Ethernet PHY #2 by removing the resistors mounted for XTAL_XI and XTAL_XO from the 25MHz Ethernet PHY #2 Crystal and mounting the appropriate resistor for the ETH1_CLKOUT signal to be routed to the XI pin of Ethernet PHY #2.

The LaunchPad also requires a 16 MHz clock source for the XDS110 for UART-USB JTAG support.

Figure 4-5 AM263x LaunchPad Clock Tree

Figure 4-5 AM263x LaunchPad Clock Tree